#### TECHNICAL MANUAL

## GENERAL SYSTEM TACTICAL ELECTRONIC WARFARE SYSTEM

FMS SERIES F-15C AND F-15D

WR-ALC/LFIT

This information is furnished on the conditions that it will not be released to another nation without the specific authorization of the Department of the Air Force of the United States; it will be used for military purposes only; the recipient will report promptly to the United States any known or suspected compromise; and the information will be provided substantially the same degree of security afforded it by the Department of Defense of the United States. Also, regardless of any other markings on the document, it will not be downgraded or declassified without the written approval of originating U.S. agency. Any request for this document should be referred to WR-ALC/LFI, 296 COCHRAN STREET, ROBINS AFB, GA 31098-1622.

This publication supersedes TO SR1F-15C-2-99GS-00-1 thru Change 8 dated 01 February 1998.

This publication is incomplete without classified TO SR1F-15C-2-99GS-00-2.

#### LIST OF EFFECTIVE PAGES

Insert latest changed pages; dispose of superseded pages in accordance with applicable regulations.

NOTE: On a changed page, the portion of the text affected by the latest change is indicated by a vertical line in the outer margin of the page. Changes to illustrations are indicated by vertical lines, miniature pointing hands, shaded areas or a major change symbol.

#### Dates of issue for original and changed pages:

| Ot | iginal | 0 | 15 | Mar 0 | n |

|----|--------|---|----|-------|---|

|    |        |   |    |       |   |

Total number of pages in this publication is 248 consisting of the following:

| Page     | #Change | Page  | #Change | Page    | #Change | Page  | #Change |

|----------|---------|-------|---------|---------|---------|-------|---------|

| No.      | No.     | No.   | No.     | No.     | No.     | No.   | No.     |

| Title    | 0       | 11-35 | 0       | 13-1    | 0       | 13-47 | 0       |

| Α        |         |       | 0       |         | 0       |       | 0       |

| В        |         |       | 0       |         | 0       |       | 0       |

| C blank  |         |       | 0       |         | 0       |       | 0       |

| i        |         |       | 0       |         | 0       |       | 0       |

| ii       | 0       | 11-40 | 0       | 13-6    | 0       |       | 0       |

| iii      |         |       | 0       | 13-7    | 0       |       | 0       |

| iv       | 0       | 11-42 | 0       | 13-8    | 0       | 13-54 | 0       |

| v        | 0       | 11-43 | 0       | 13-9    | 0       | 13-55 | 0       |

| vi blank |         | 11-44 | 0       |         | 0       | 13-56 | 0       |

| 00-1     | 0       |       | 0       | 13-11 . | 0       | 13-57 | 0       |

| 00-2     | 0       | 11-46 | 0       | 13-12   | 0       | 13-58 | 0       |

| 11-1     |         | 11-47 | 0       | 13-13   | 0       | 13-59 | 0       |

| 11-2     |         |       | 0       |         | 0       |       | 0       |

| 11-3     |         |       | 0       |         | 0       |       | 0       |

| 11-4     |         | -     | 0       |         | 0       |       | 0       |

| 11-5     |         |       | 0       |         | 0       |       | 0       |

| 11-6     |         |       | 0       |         | 0       |       | 0       |

| 11-7     |         |       | 0       |         | 0       |       | 0       |

| 11-8     |         |       | 0       | _       | 0       |       | 0       |

| 11-9     |         |       | 0       |         | 0       |       | 0       |

| 11-10    |         |       | 0       |         | 0       |       | 0       |

| 11-10    |         |       | 0       |         | 0       |       | 0       |

| 11-12    |         |       | 0       |         | 0       |       | 0       |

| 11-13    |         |       | 0       |         | 0       |       | 0       |

| 11-14    |         | -     | 0       |         | 0       |       | 0       |

| 11-15    |         |       | 0       |         | 0       |       | 0       |

| 11-16    |         | _     | 0       |         | 0       |       | 0       |

| 11-17    |         |       | 0       |         | 0       |       | 0       |

|          |         |       |         | , .     | 0       |       | 0       |

| 11-18    |         |       | 0       |         |         |       | 0       |

| 11-19    |         |       |         |         | 0       |       |         |

| 11-20    |         |       | 0       |         | 0       |       | 0       |

| 11-21    |         |       | 0       |         | 0       |       | 0       |

| 11-22    |         |       | 0       |         | 0       |       | 0       |

| 11-23    |         | -     | 0       |         | 0       |       | 0       |

| 11-24    |         |       | 0       |         | 0       |       | 0       |

| 11-25    |         |       | 0       |         | 0       |       | 0       |

| 11-26    |         |       | 0       |         | 0       |       | 0       |

| 11-27    |         |       | 0       |         | 0       |       | 0       |

| 11-28    |         |       | 0       |         | 0       |       | 0       |

| 11-29    |         |       | 0       |         | 0       |       | 0       |

| 11-30    |         |       | 0       |         | 0       |       | 0       |

| 11-31    |         |       | 0       |         | 0       | _     | 0       |

| 11-32    |         |       | 0       |         | 0       |       | 0       |

| 11-33    |         |       | 0       |         | 0       |       | 0       |

| 11-34    | 0       | 11-80 | 0       | 13-46 . | 0       | 13-92 | 0       |

| Page<br>No. | #Change<br>No. | _                | Page<br>No. | #Change<br>No. | _ | #Change<br>No. |

|-------------|----------------|------------------|-------------|----------------|---|----------------|

| 13-93       | 0              | 15-32 blank      | ı           |                |   |                |

|             | 0              | Glossary 1       |             |                |   |                |

|             | 0              | Glossary 2 blank | 1           |                |   |                |

|             | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

| 13-101      | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

|             |                |                  |             |                |   |                |

| 13-108 blar | nk0            |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

| 14-7        | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

| 14-14       | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

| 15-7        | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

| =           | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

| 15-13       | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

| 15-20       | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

|             | 0              |                  |             |                |   |                |

| 15-51       |                |                  |             |                |   |                |

#### **TABLE OF CONTENTS**

| Section | on/Parag      | raph                                             | Page  |

|---------|---------------|--------------------------------------------------|-------|

| LIST    | OF ILLUS      | TRATIONS                                         | iii   |

| LIST    | OF TABL       | ES                                               | iv    |

| INTRO   | ODUCTIC       | ON                                               | V     |

|         | PURPOS        | SE AND SCOPE                                     | v     |

|         | SIGNIF        | ICANT CHANGES                                    | V     |

|         | APPLIC        | CABILITY NOTATIONS                               | V     |

|         |               | VEMENT REPORTS                                   |       |

|         | RECOR         | D OF APPLICABLE TIME COMPLIANCE TECHNICAL ORDERS | V     |

| 00      | TACTIO        | CAL ELECTRONIC WARFARE SYSTEM (TEWS)             | 0-1   |

|         | 00-1          | SYSTEM FUNCTIONAL DESCRIPTION                    | 0-1   |

|         | 00-2          | DESCRIPTION                                      | 0-1   |

|         | 00-12         | SPECIAL MAINTENANCE REQUIREMENTS                 | 0-1   |

|         | 00-13         | RF TRANSMISSION LINE/WAVEGUIDE/RF COMPONENT      |       |

|         |               | TEST PROCEDURES                                  | 0-1   |

|         | 00-14         | CONSUMABLE MATERIALS LIST                        | 0-1   |

|         | 00-15         | SUPPORT EQUIPMENT LIST                           |       |

|         | 00-16         | TEST EQUIPMENT                                   | 0-1   |

| XI      | RADAR         | R WARNING RECEIVER SET AN/ALR-56C (RWR)          | 11-1  |

|         | 11-1          | SYSTEM FUNCTIONAL DESCRIPTION                    | 11-1  |

|         | 11-4          | DESCRIPTION                                      | 11-1  |

|         | 11-8          | LINE REPLACEABLE UNITS                           |       |

|         | 11 <b>-</b> 9 | COMPONENT DESCRIPTION                            |       |

|         | 11-22         | PRINCIPLES OF OPERATION                          | 11-2  |

|         | 11-416        | SPECIAL MAINTENANCE REQUIREMENTS                 | 11-79 |

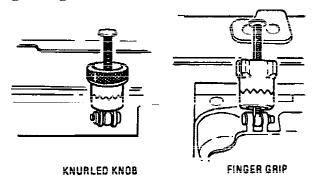

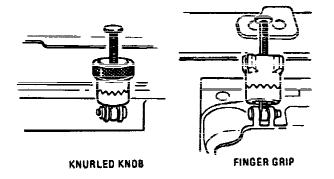

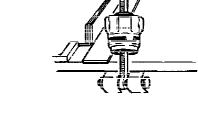

|         | 11-417        | FASTENERS                                        |       |

|         | 11-424        | CONSUMABLE MATERIALS LIST                        |       |

|         | 11-425        | SUPPLIES (CONSUMABLES)                           |       |

|         | 11-426        | SUPPORT EQUIPMENT LIST                           |       |

|         | 11-427        | TEST EQUIPMENT                                   |       |

|         | 11-428        | SPECIAL TOOLS                                    | 11-79 |

| XIII    | COUNT         | ERMEASURES SET AN/ALQ-135E(V) (ICMS) - F-15C     | 13-1  |

|         | 13-1          | SYSTEM FUNCTIONAL DESCRIPTION                    | 13-1  |

|         | 13-4          | DESCRIPTION                                      | 13-1  |

|         | 13-6          | LINE REPLACEABLE UNITS                           | 13-1  |

|         | 13-7          | COMPONENT DESCRIPTION                            |       |

|         | 13-32         | PRINCIPLES OF OPERATION                          | 13-9  |

| Secti | on/Parag | raph                                      | Page       |

|-------|----------|-------------------------------------------|------------|

|       | 13-185   | SPECIAL MAINTENANCE REQUIREMENTS          | 13-106     |

|       | 13-186   | FASTENERS                                 | 13-106     |

|       | 13-193   | CONSUMABLE MATERIALS LIST                 | 13-106     |

|       | 13-194   | SUPPLIES (CONSUMABLES)                    | 13-106     |

|       | 13-195   | SUPPORT EQUIPMENT LIST                    | 13-107     |

|       | 13-196   | TEST EQUIPMENT                            | 13-107     |

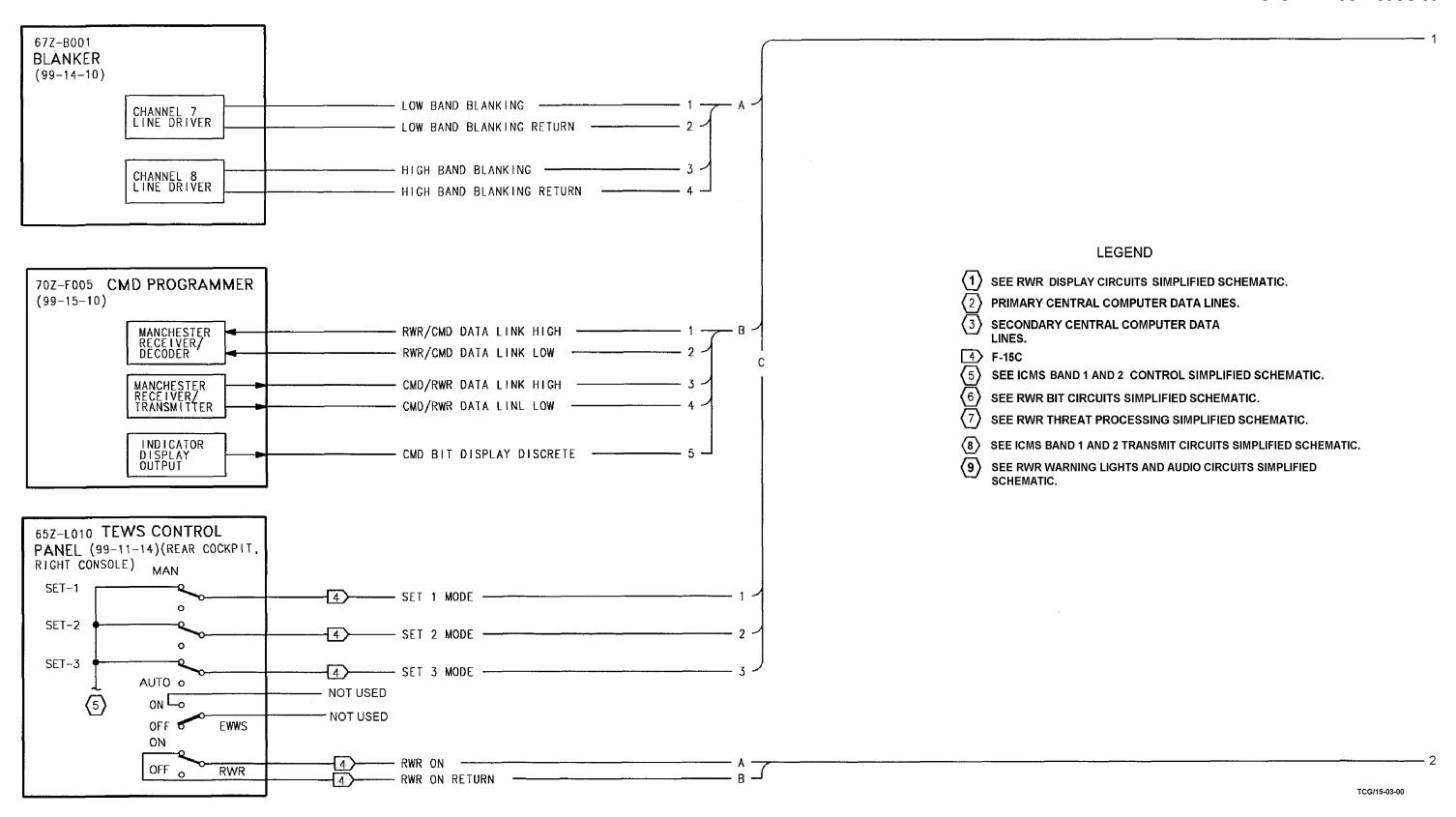

| XIV   | INTERF   | FERENCE BLANKER                           | 14-1       |

|       | 14-1     | SYSTEM FUNCTIONAL DESCRIPTION             | 14-1       |

|       | 14-3     | DESCRIPTION                               | 14-1       |

|       | 14-6     | PRINCIPLES OF OPERATION                   | 14-1       |

|       | 14-25    | SPECIAL MAINTENANCE REQUIREMENTS          | 14-11      |

|       | 14-26    | FASTENERS                                 | 14-11      |

|       | 14-33    | CONSUMABLE MATERIALS LIST                 | 14-13      |

|       | 14-34    | SUPPLIES (CONSUMABLES)                    | 14-13      |

|       | 14-35    | SUPPORT EQUIPMENT LIST                    | 14-13      |

|       | 14-36    | TEST EQUIPMENT                            | 14-13      |

|       | 14-37    | SPECIAL TOOLS                             | 14-14      |

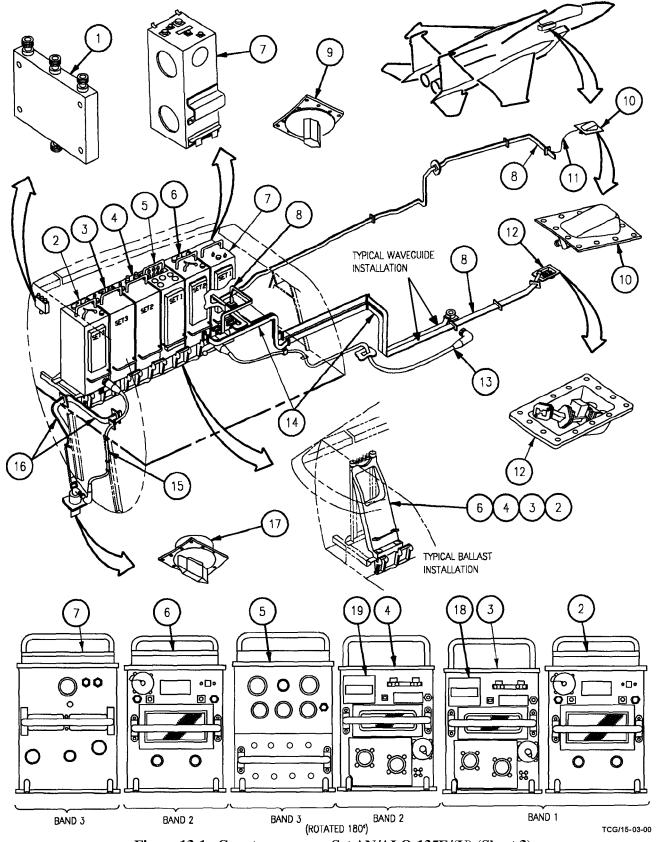

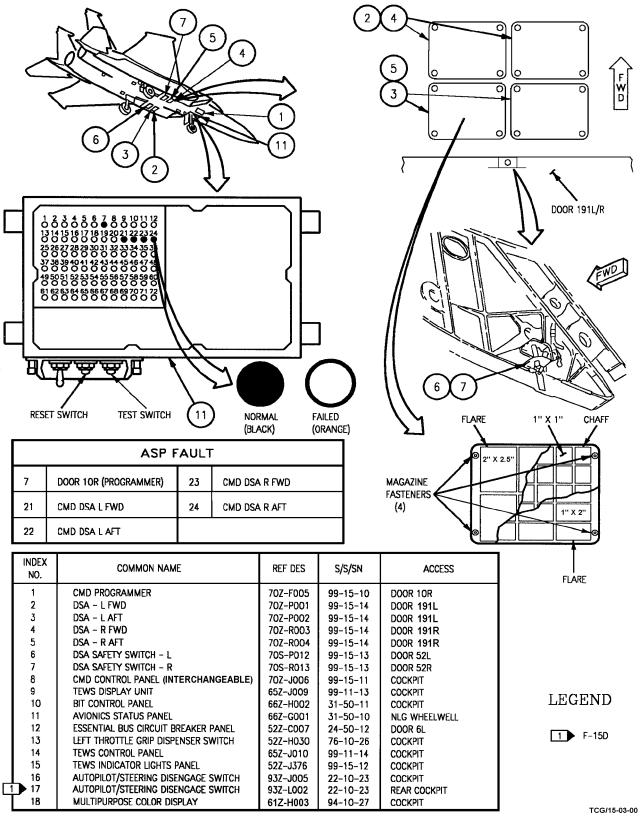

| XV    | COUNT    | TERMEASURES DISPENSER SET (CMD) AN/ALE-45 | 15-1       |

|       | 15-1     | SYSTEM FUNCTIONAL DESCRIPTION             | 15-1       |

|       | 15-4     | DESCRIPTION                               | 15-1       |

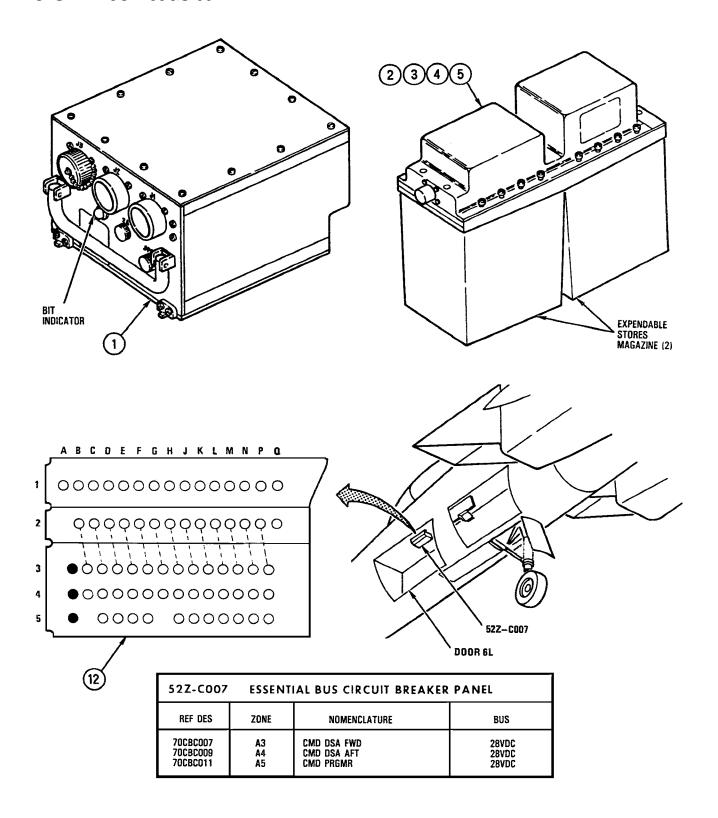

|       | 15-5     | LINE REPLACEABLE UNITS                    | 15-1       |

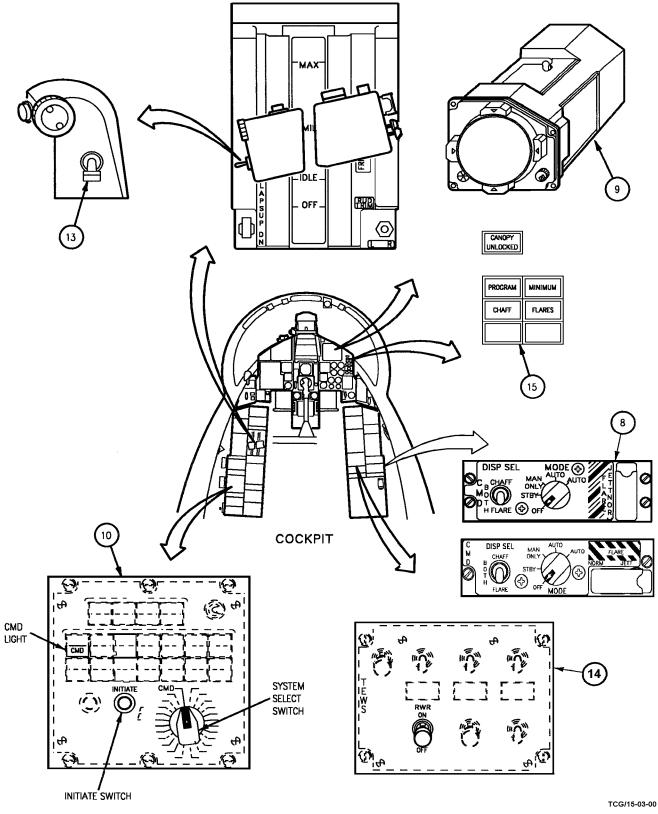

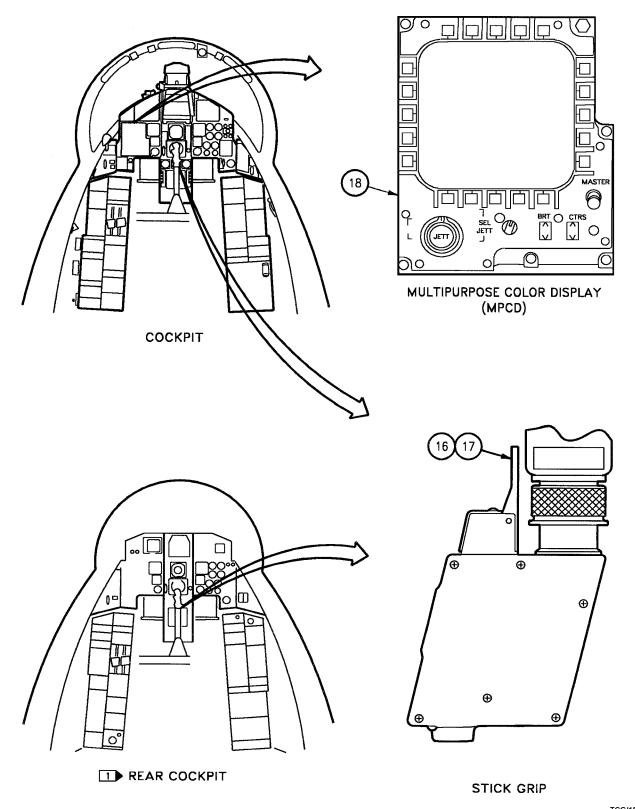

|       | 15-6     | COMPONENT DESCRIPTION                     | 15-2       |

|       | 15-12    | RELATED COMPONENT DESCRIPTION             | 15-2       |

|       | 15-14    | PRINCIPLES OF OPERATION                   | 15-2       |

|       | 15-42    | SPECIAL MAINTENANCE REQUIREMENTS          | 15-30      |

|       | 15-44    | FASTENERS                                 | 15-30      |

|       | 15-50    | CONSUMABLE MATERIALS LIST                 | 15-31      |

|       | 15-51    | SUPPLIES (CONSUMABLES)                    | 15-31      |

|       | 15-52    | SUPPORT EQUIPMENT LIST                    | 15-31      |

|       | 15-53    | TEST EQUIPMENT                            | 15-31      |

| GLOS  | SSARY    |                                           | Glossary 1 |

#### **LIST OF ILLUSTRATIONS**

| Figure No | Title                                                      | Page  |

|-----------|------------------------------------------------------------|-------|

| 00-1      | TEWS Block Diagram                                         | 0-2   |

| 11-1      | Countermeasures Receiving Set AN/ALR-56C                   | 11-4  |

| 11-2      | RWR Functional Block Diagram                               | 11-10 |

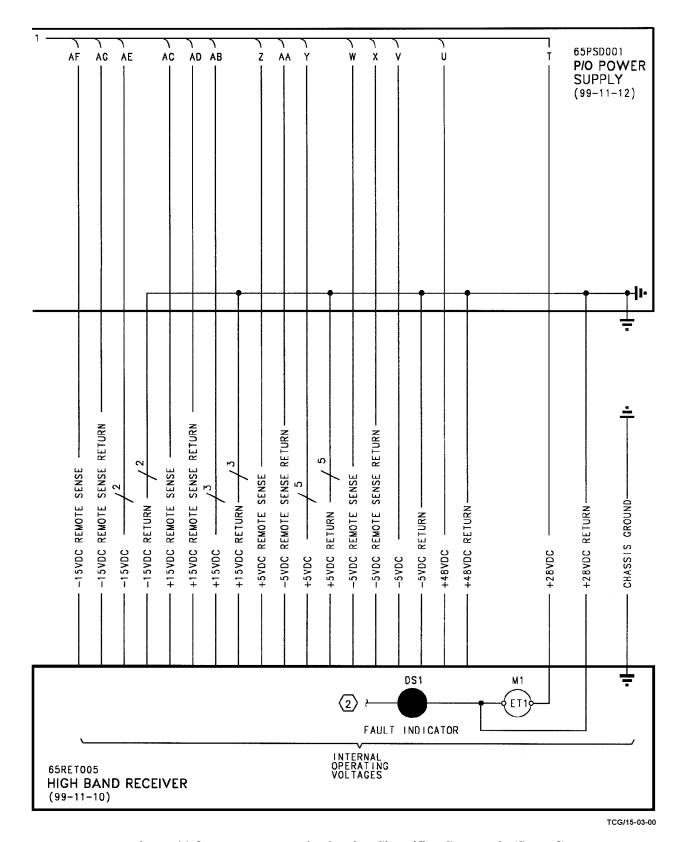

| 11-3      | RWR Power Distribution Simplified Schematic                | 11-15 |

| 11-4      | RWR Displays                                               | 11-18 |

| 11-5      | RWR Receiving Simplified Schematic                         | 11-21 |

| 11-6      | RWR Threat Processing Simplified Schematic                 | 11-24 |

| 11-7      | RWR Display Circuits Simplified Schematic                  | 11-32 |

| 11-8      | RWR Warning Lights and Audio Circuits Simplified Schematic | 11-35 |

| 11-9      | RWR BIT Circuits Simplified Schematic                      | 11-65 |

| 11-10     | RWR Interface Simplified Schematic                         | 11-71 |

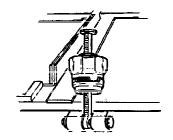

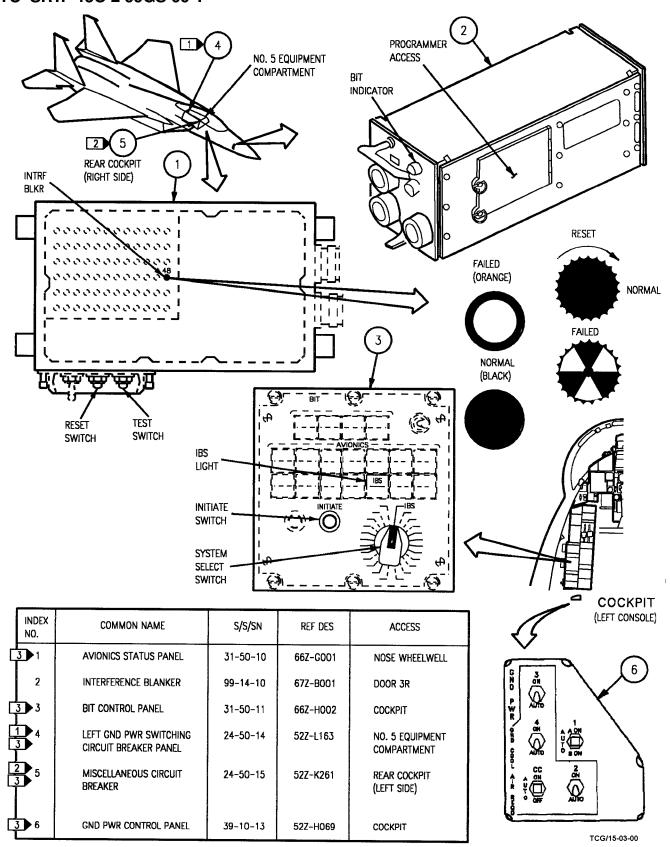

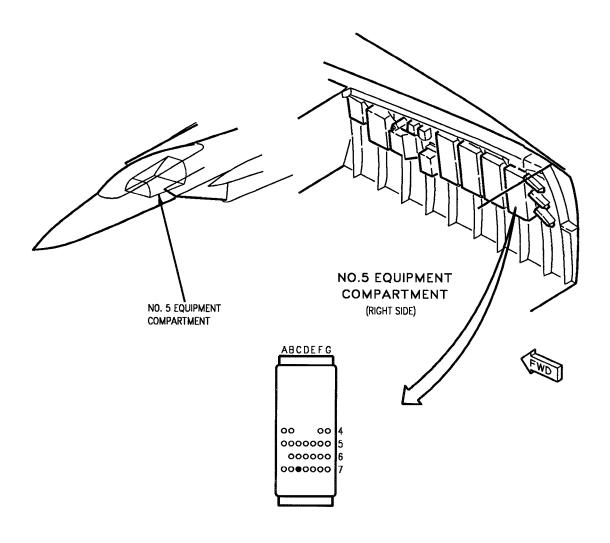

| 13-1      | Countermeasures Set AN/ALQ-135E(V)                         | 13-11 |

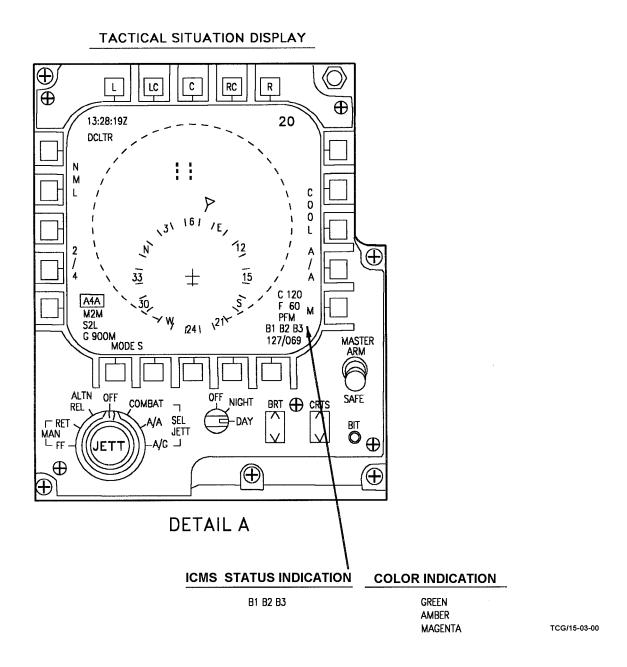

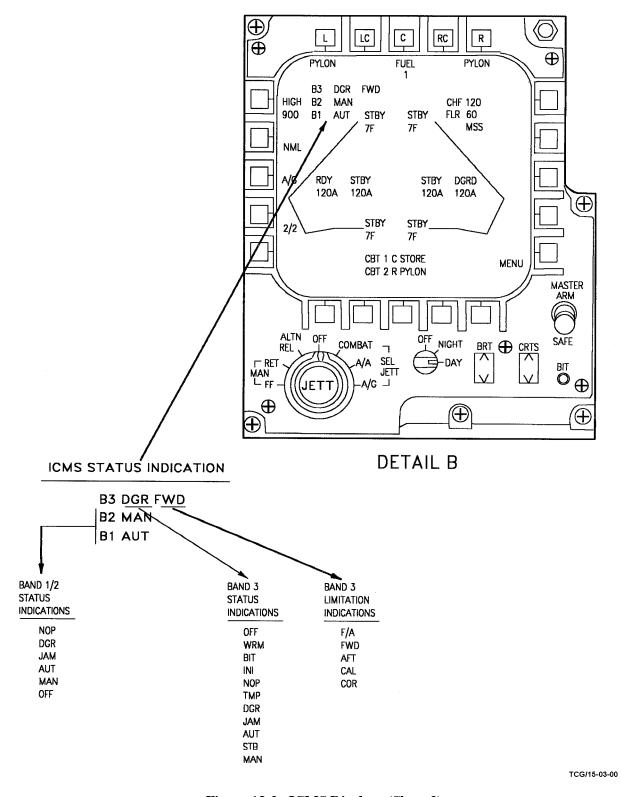

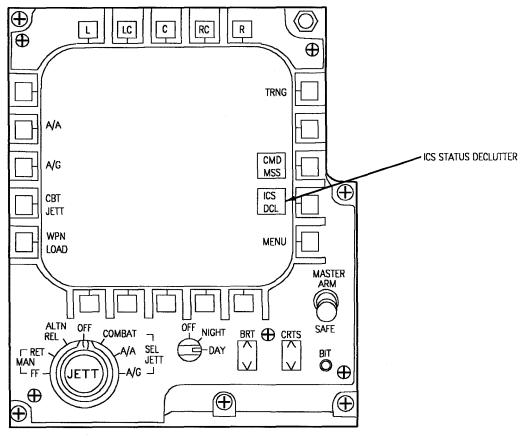

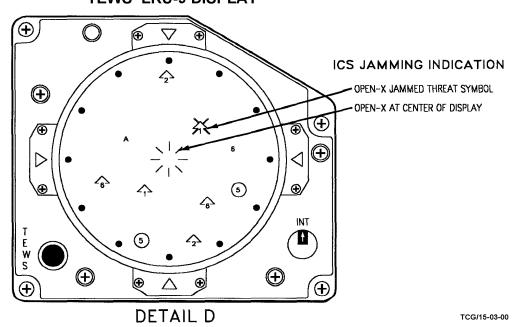

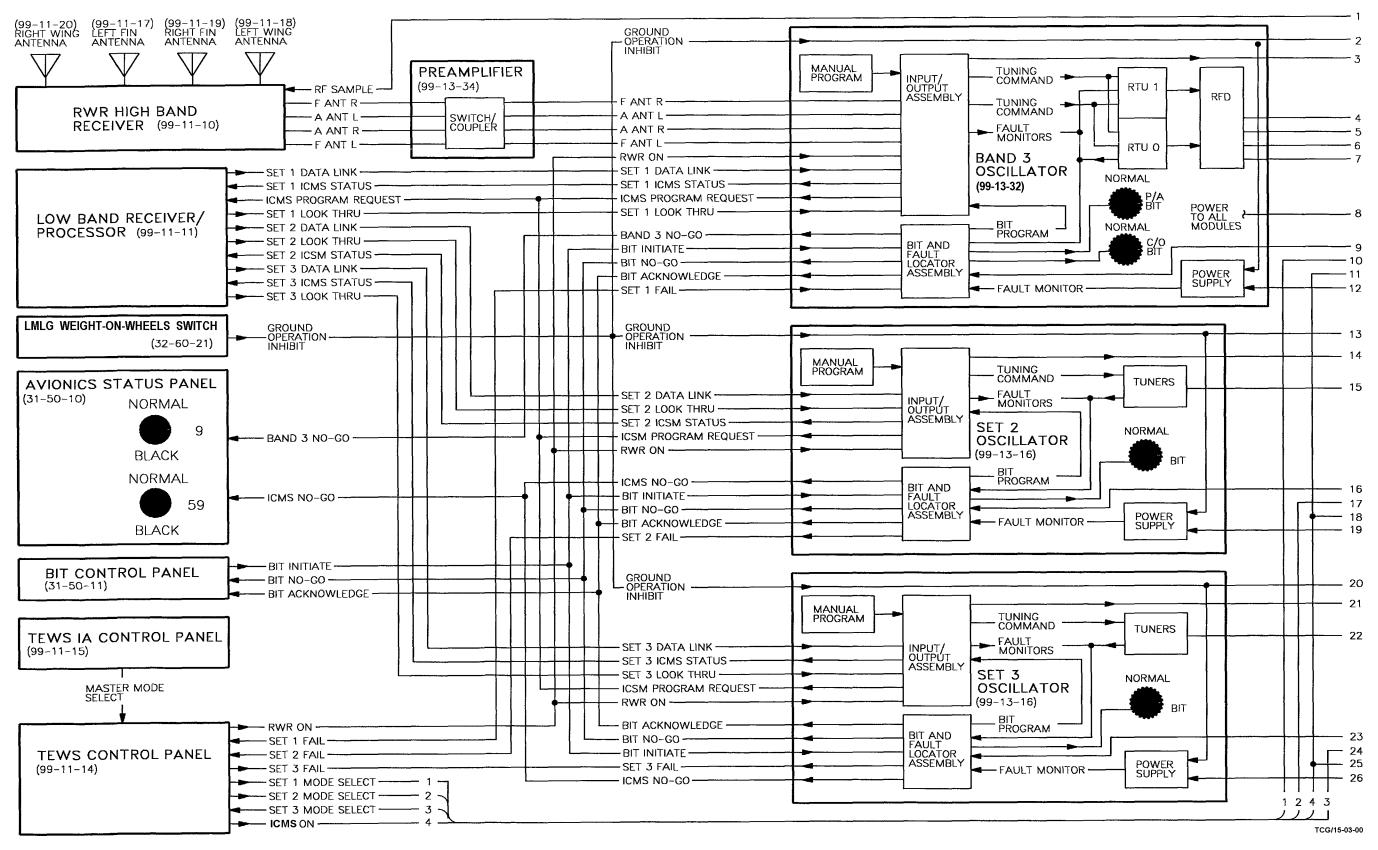

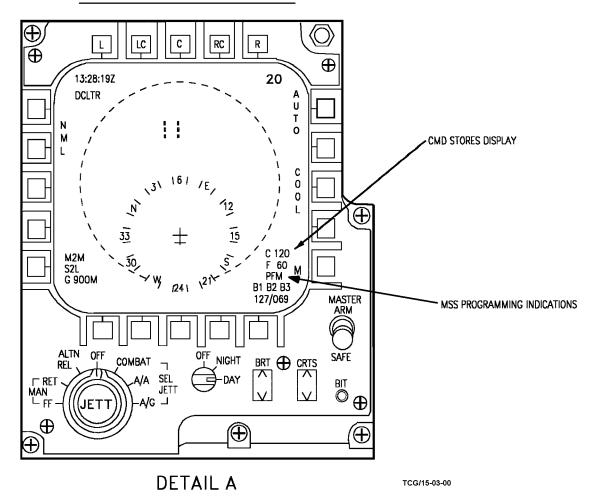

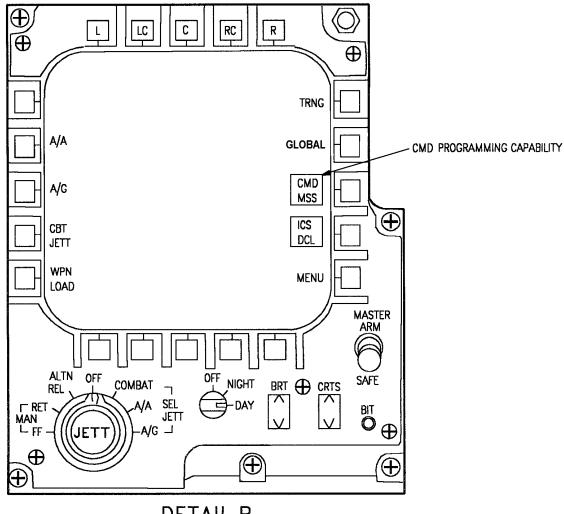

| 13-2      | ICMS Displays                                              | 13-24 |

| 13-3      | ICMS Functional Block Diagram                              | 13-29 |

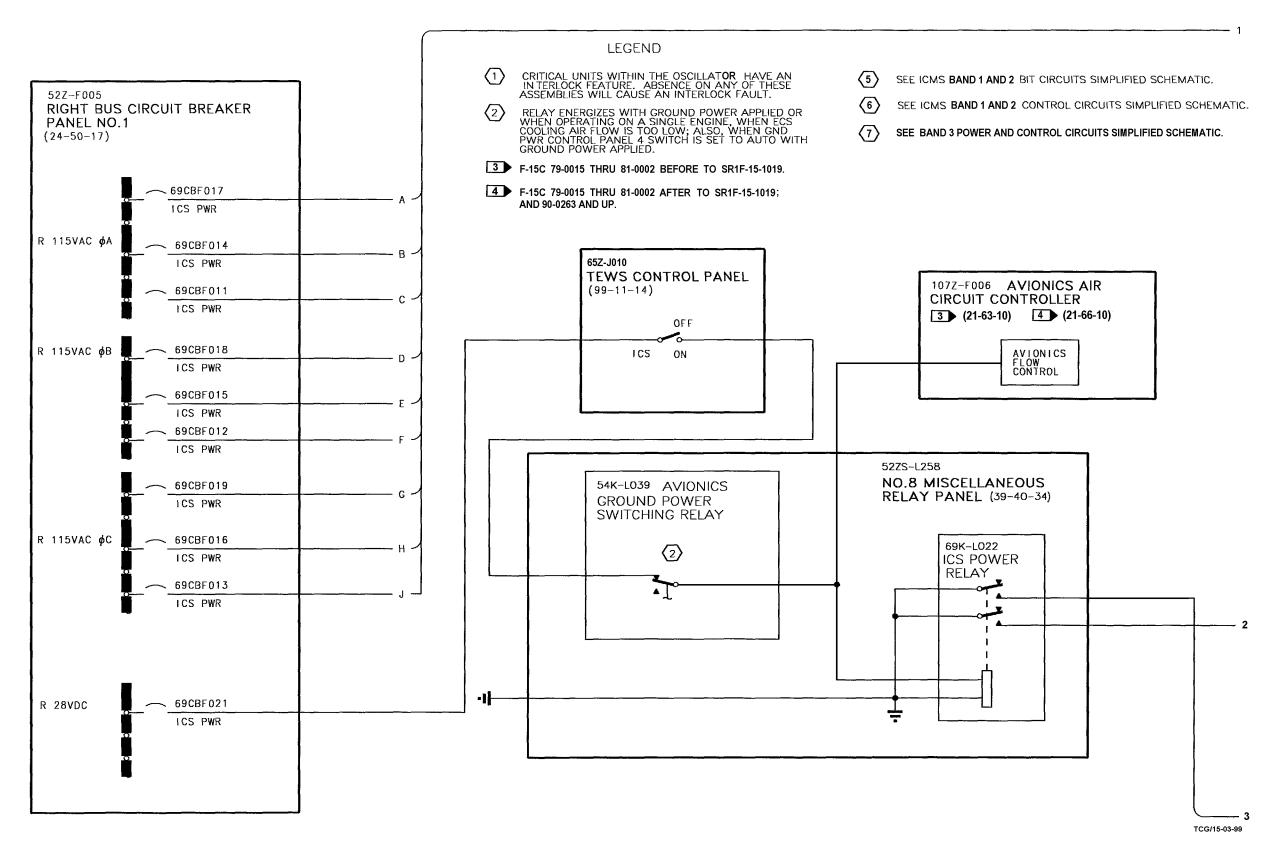

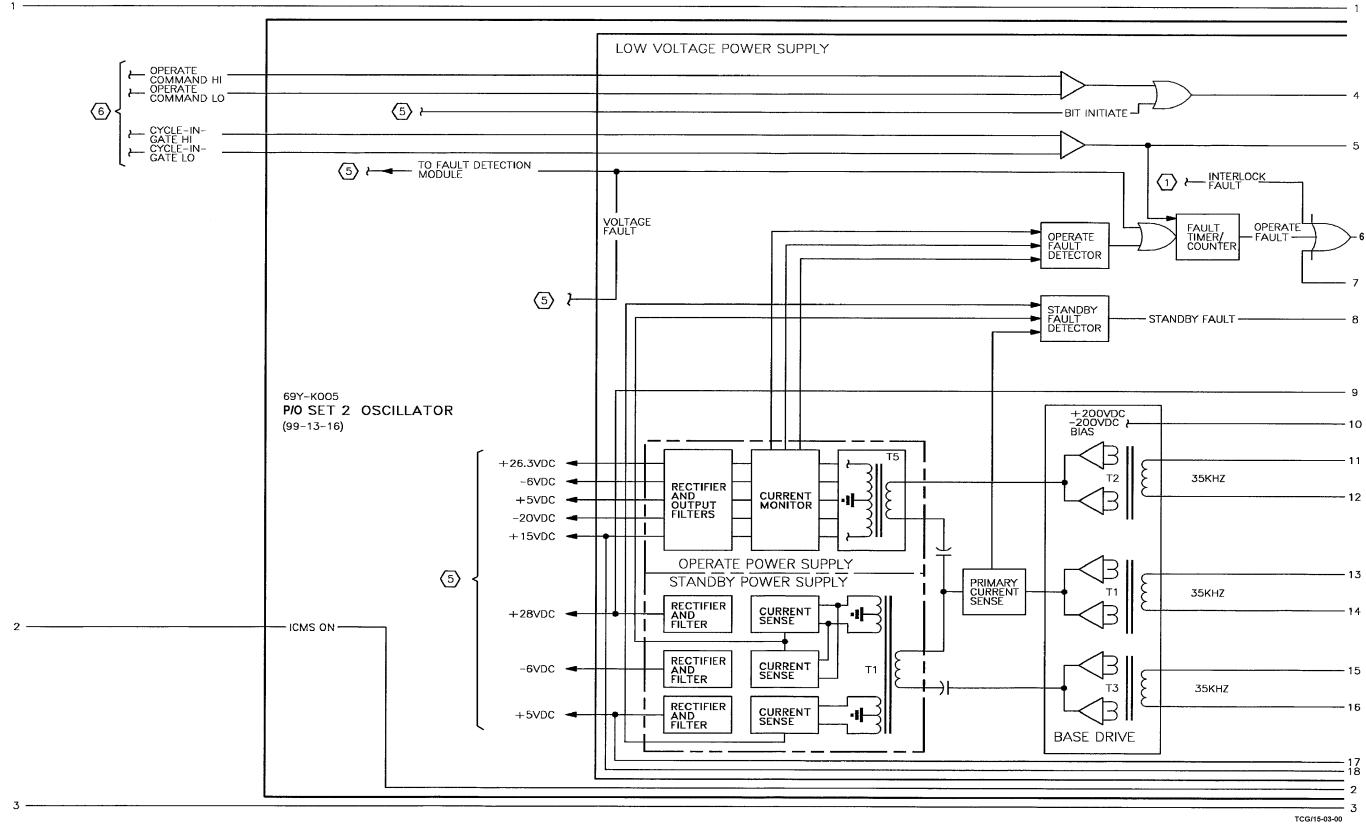

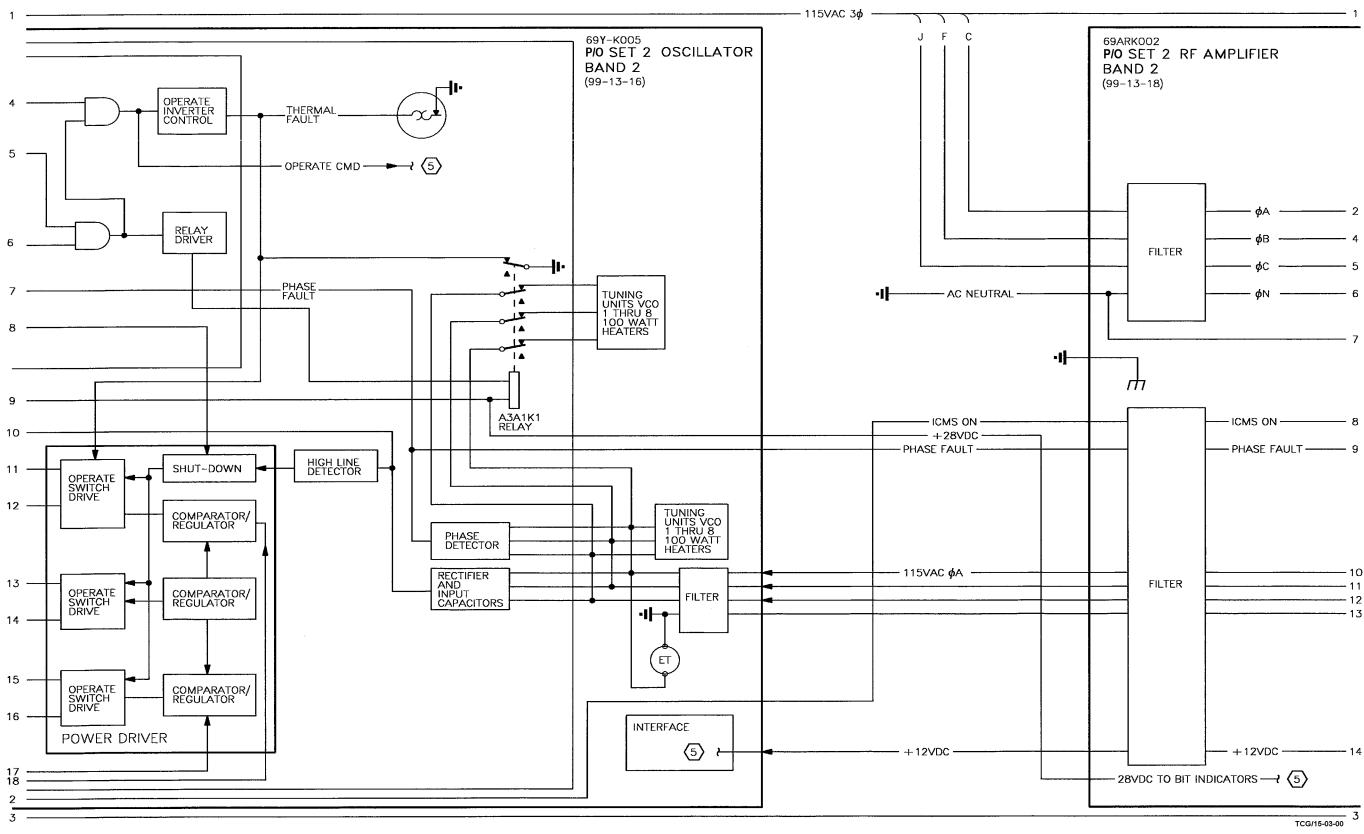

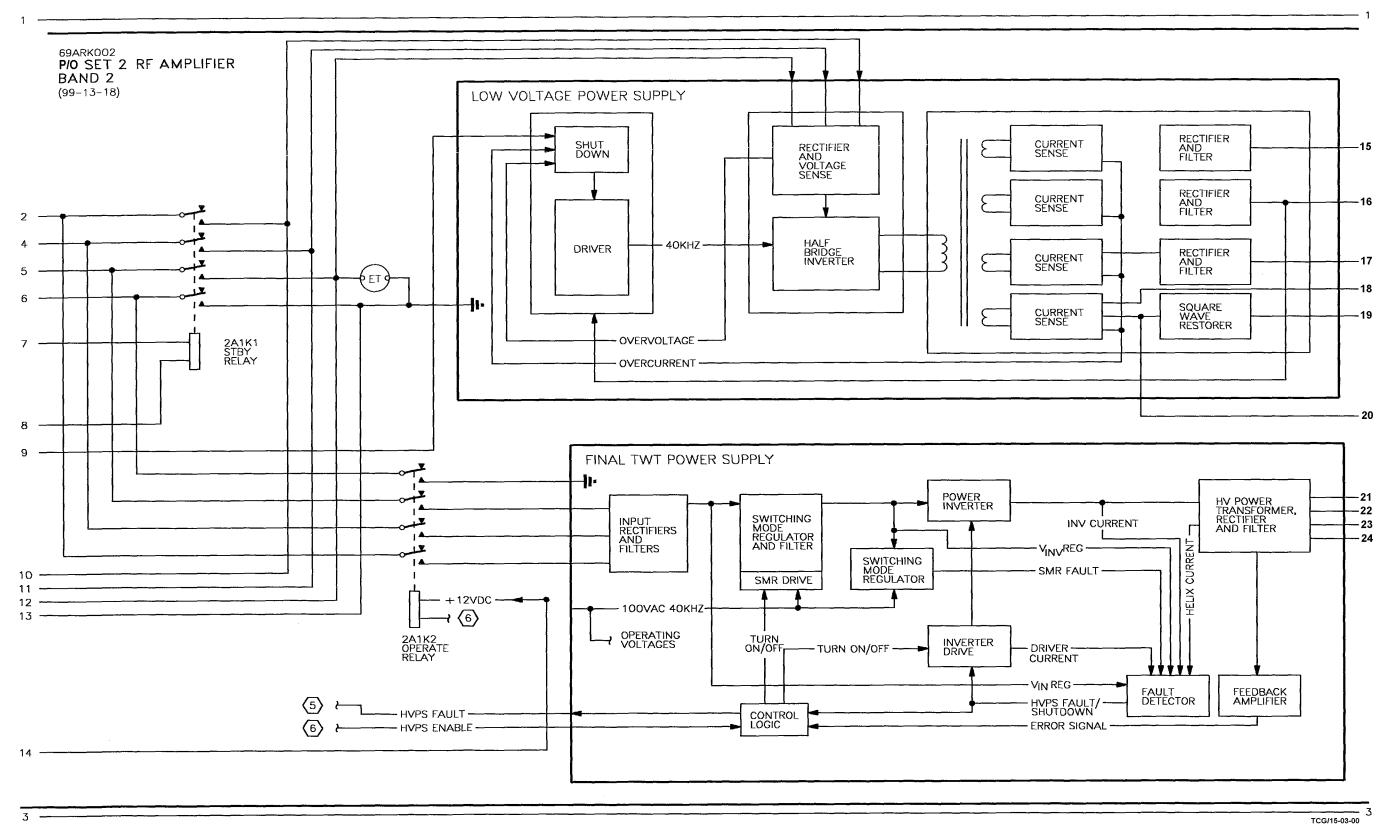

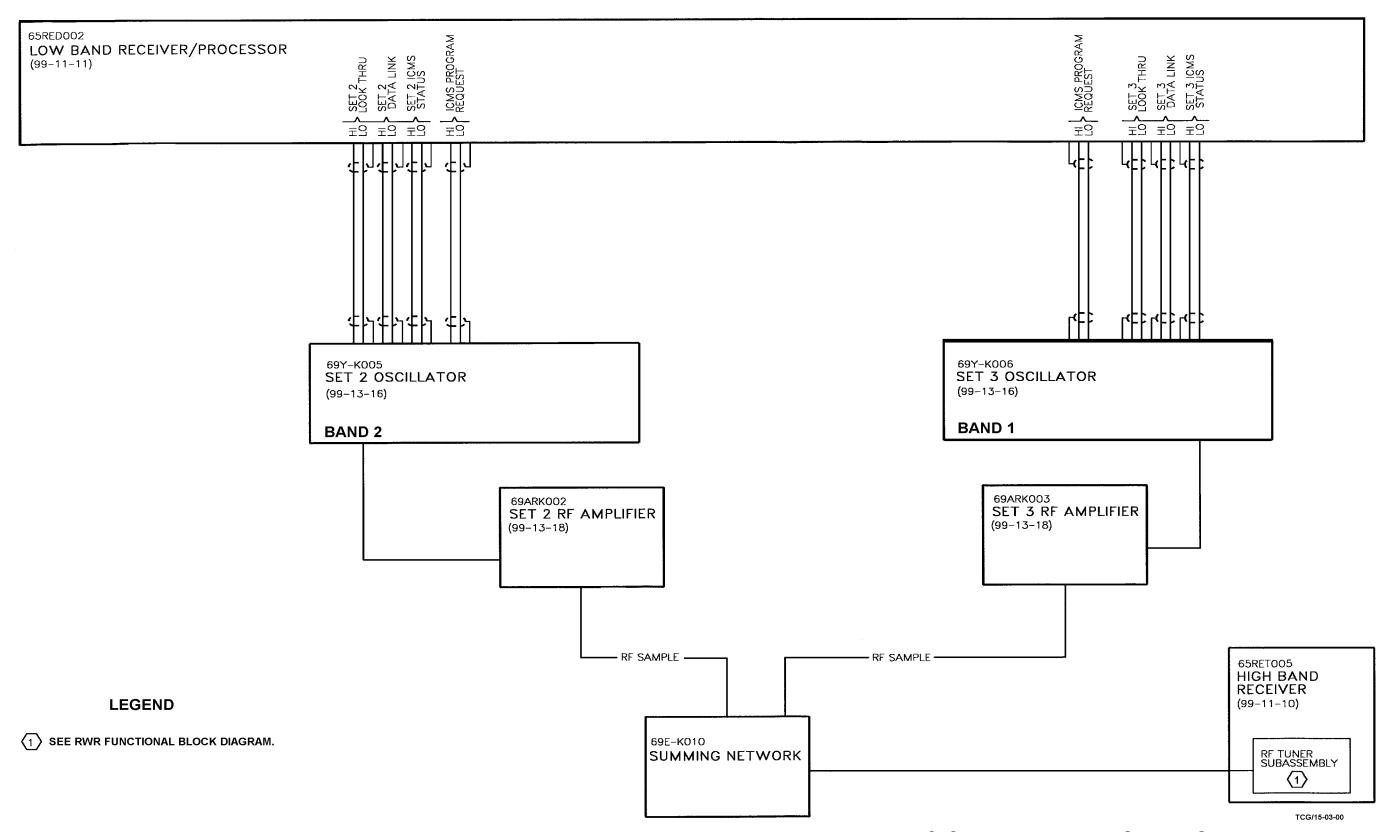

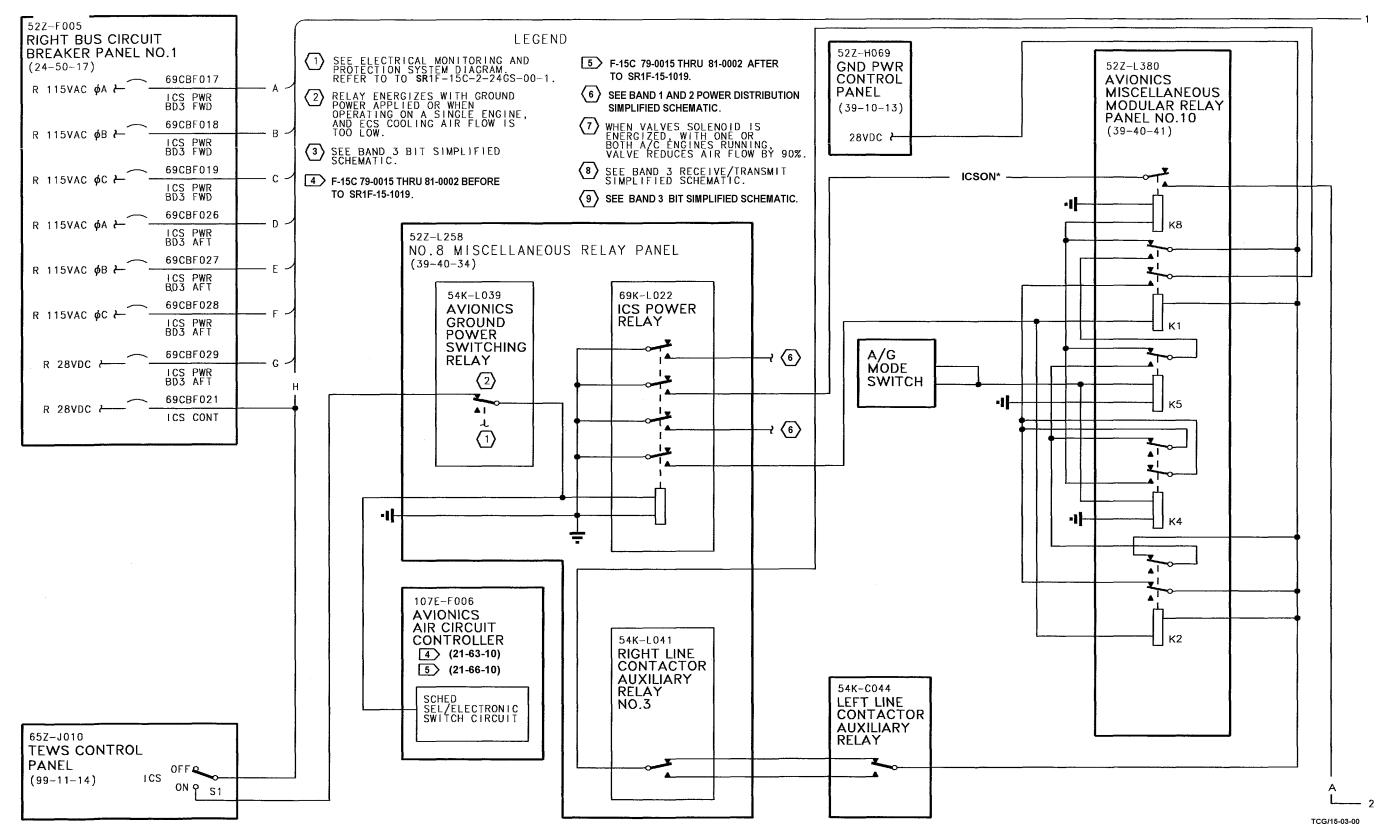

| 13-4      | ICMS Band 1 and 2 Power Distribution Simplified Schematic  | 13-31 |

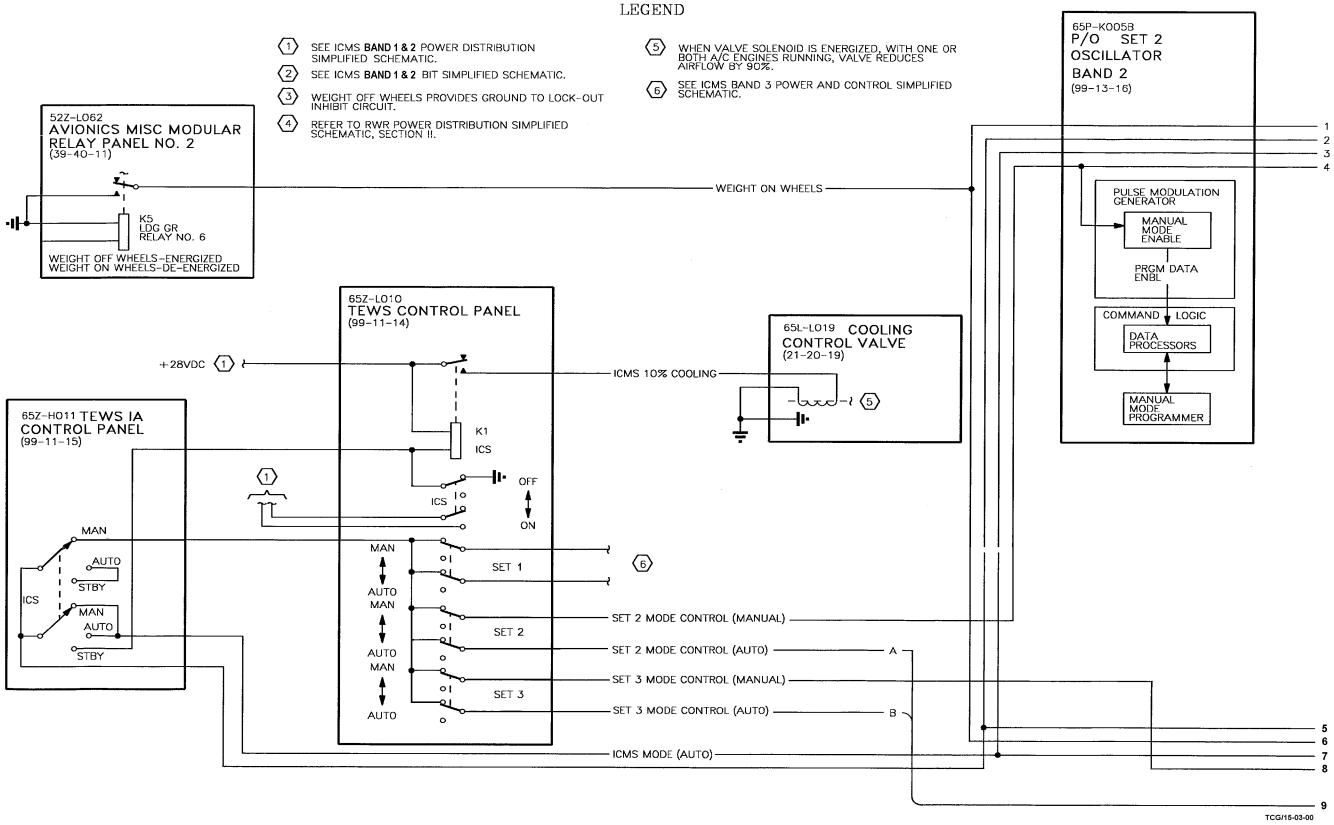

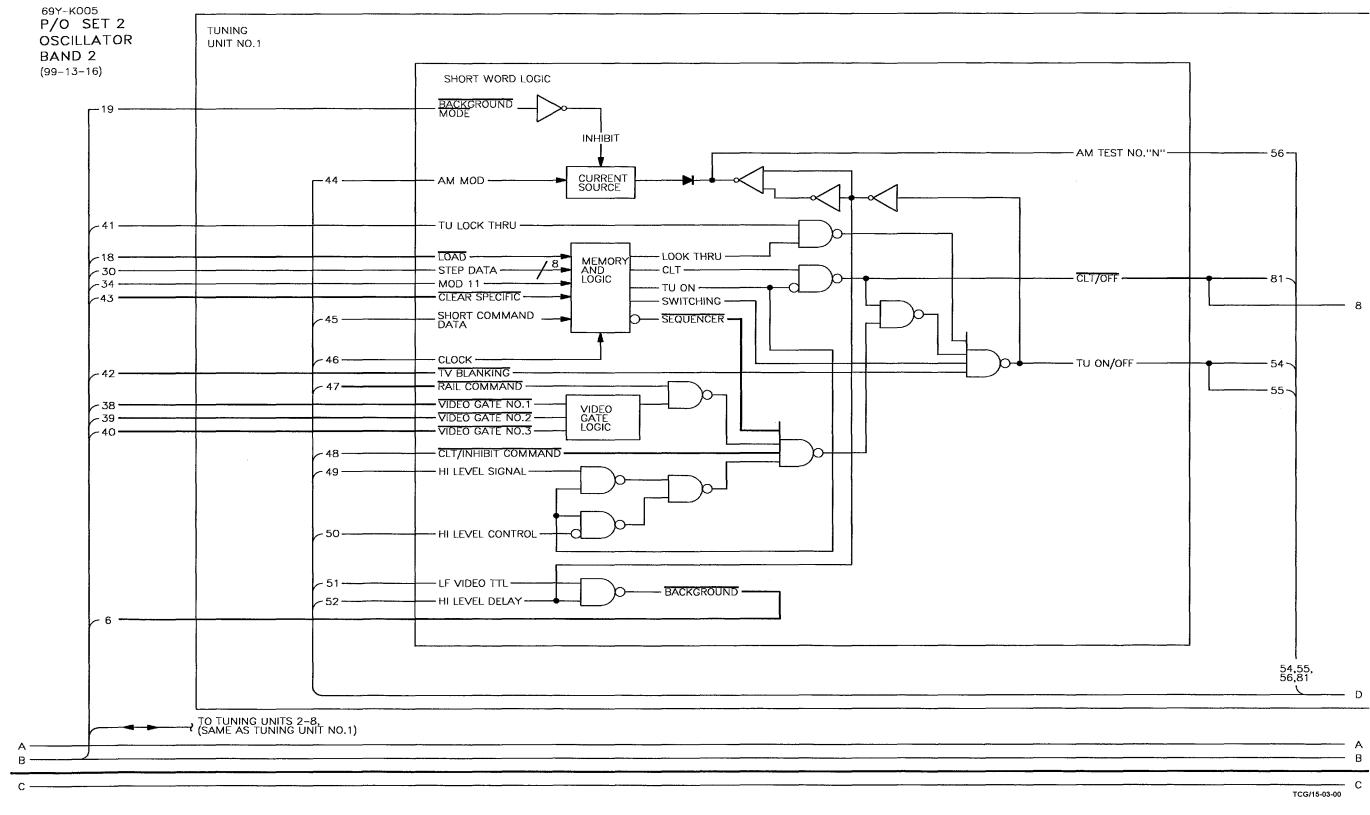

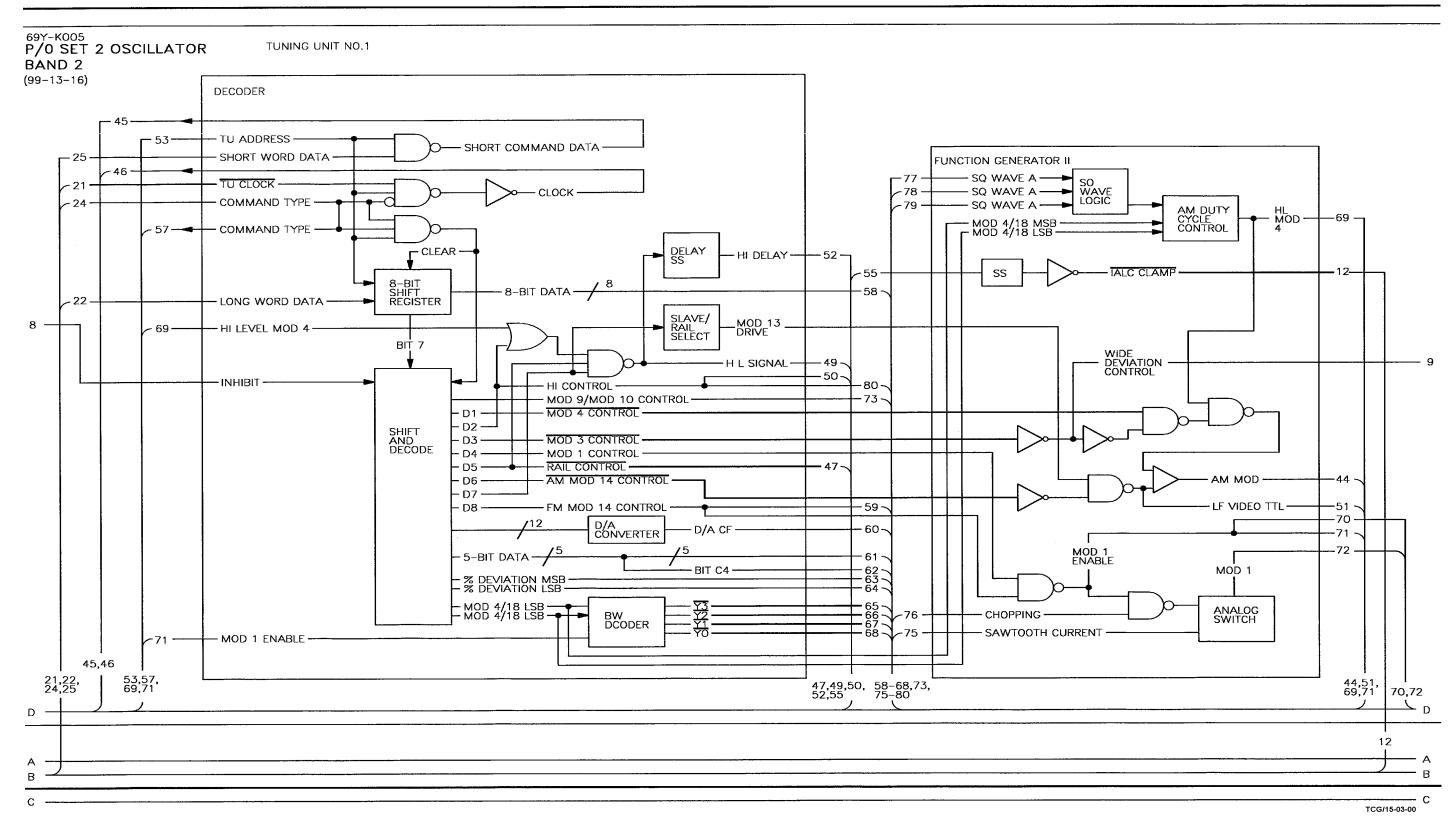

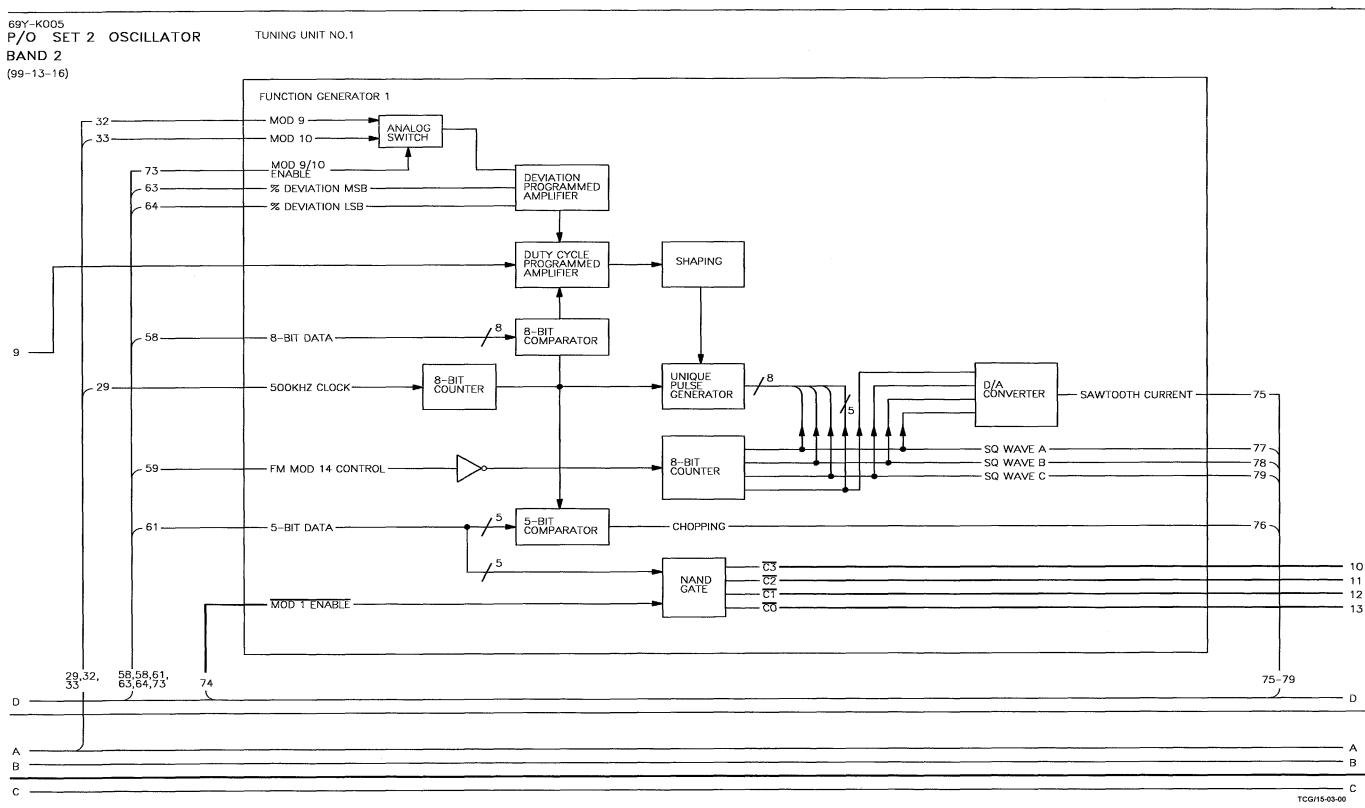

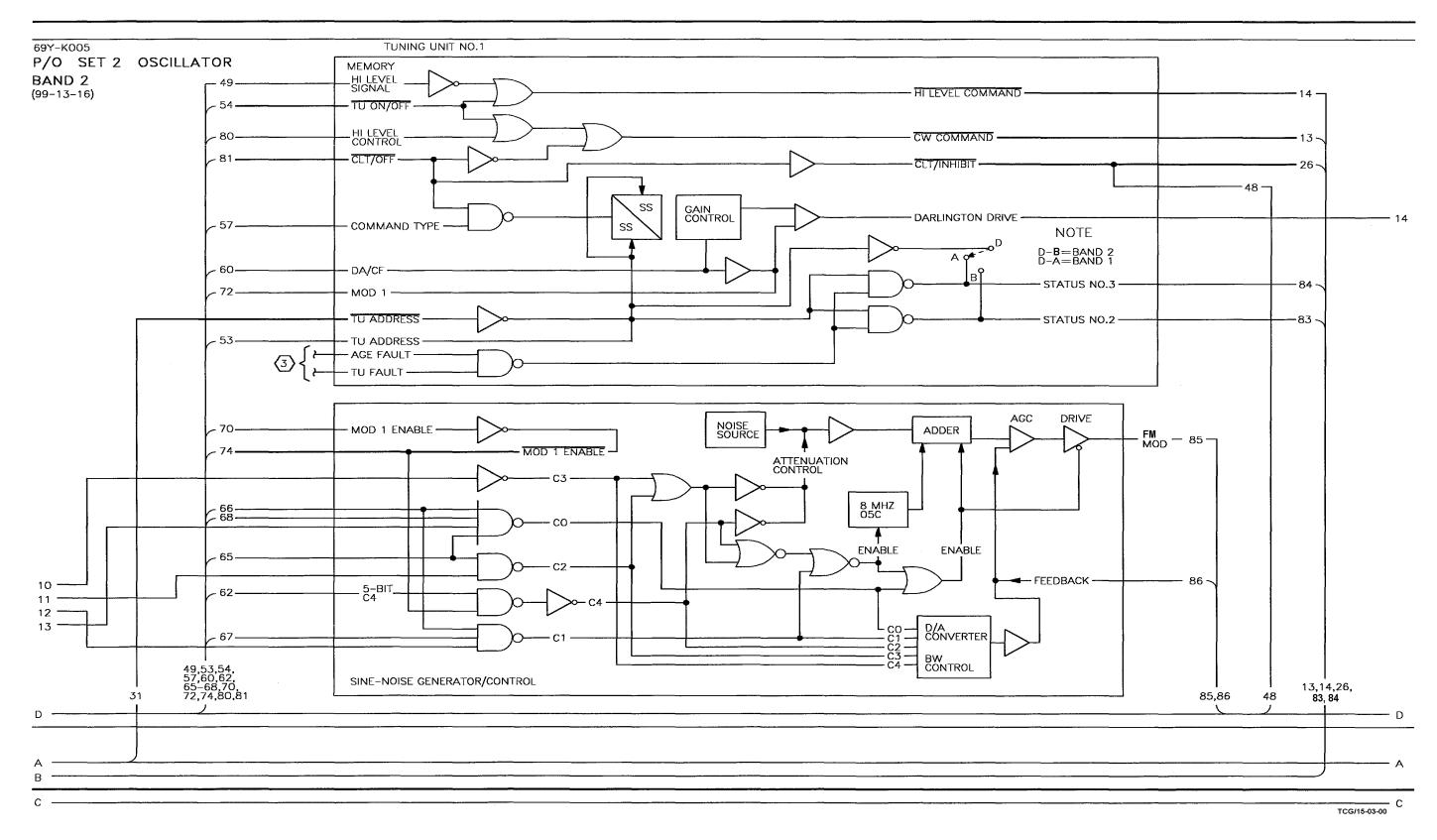

| 13-5      | ICMS Band 1 and 2 Control Circuits Simplified Schematic    | 13-36 |

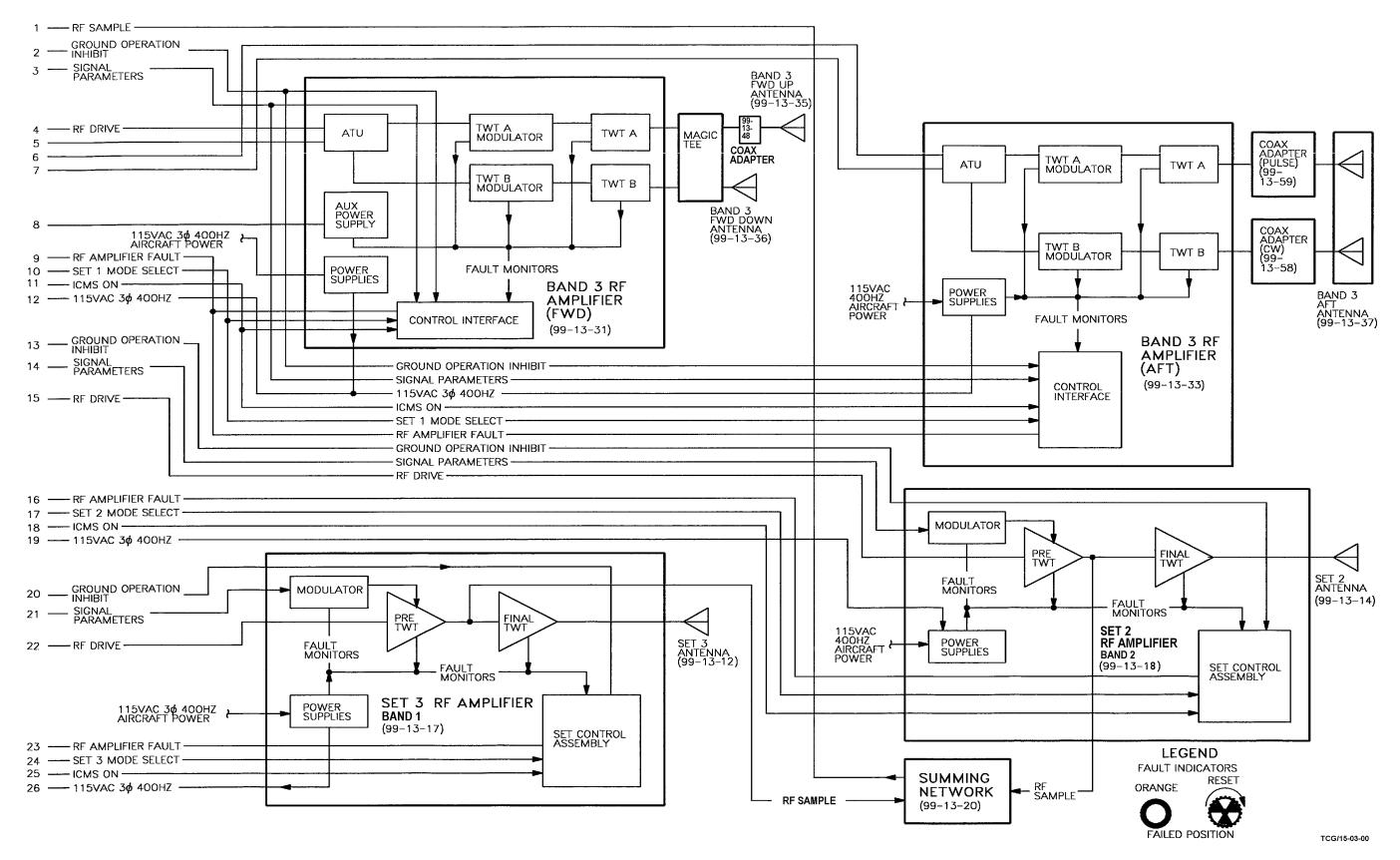

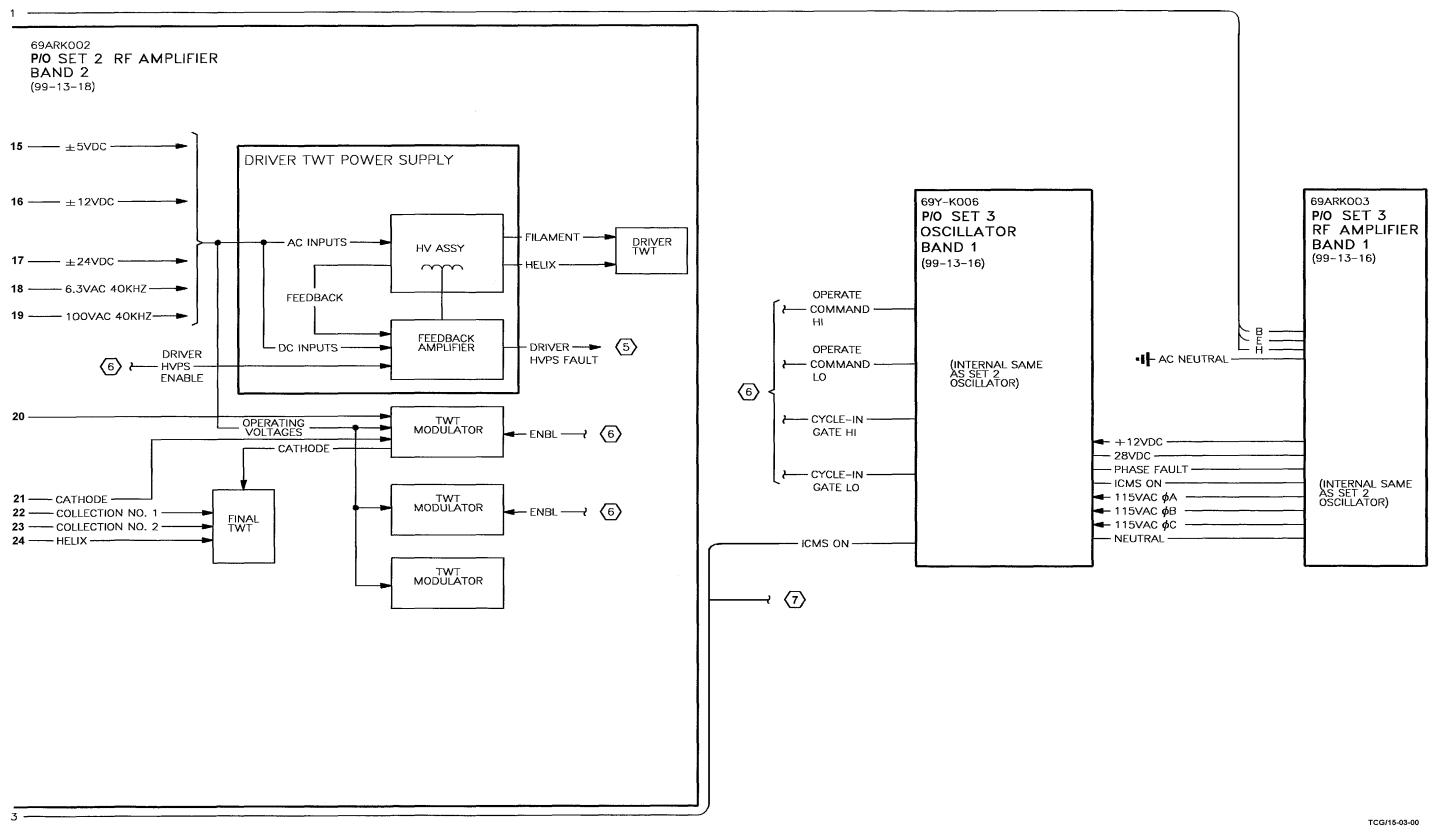

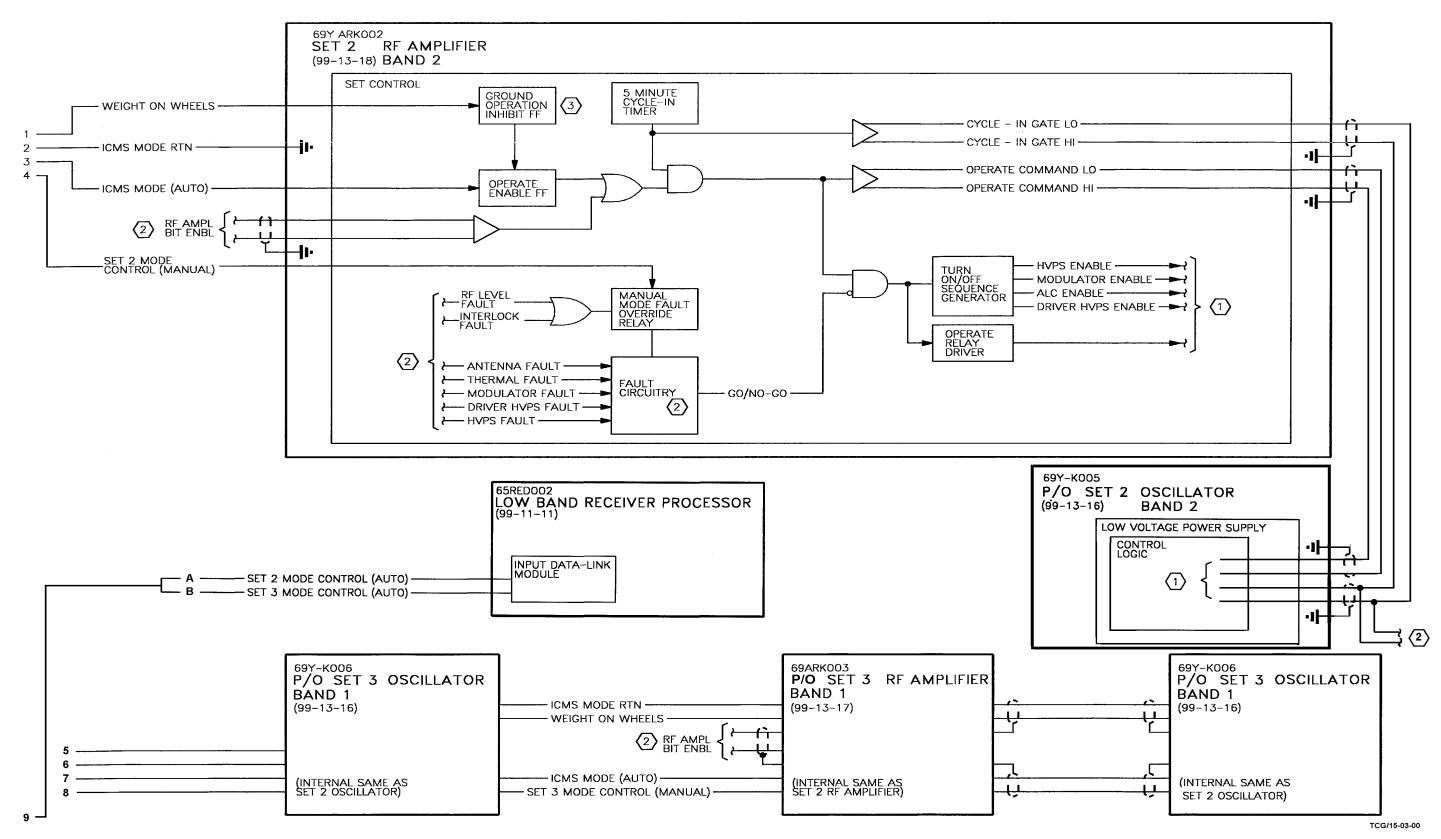

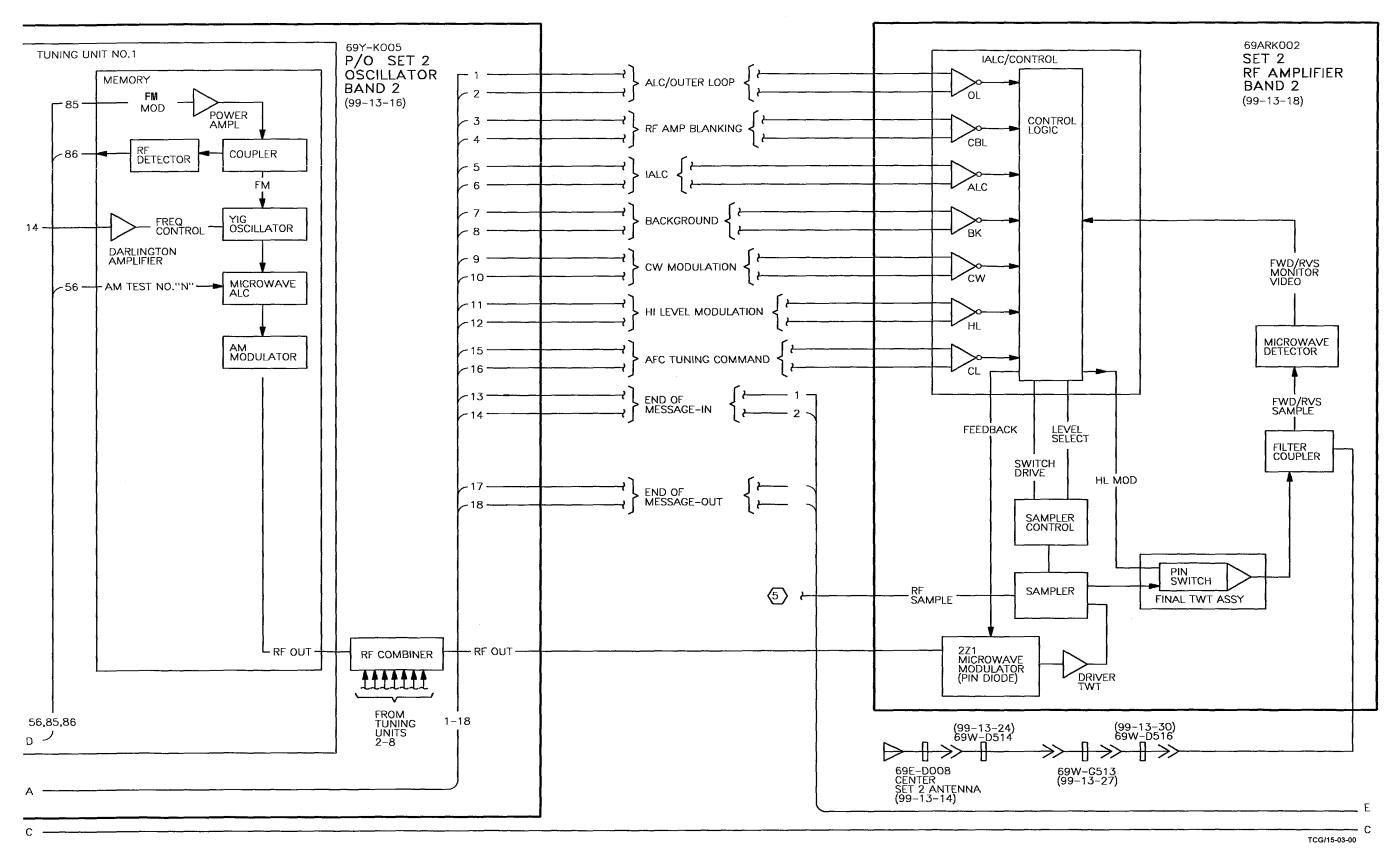

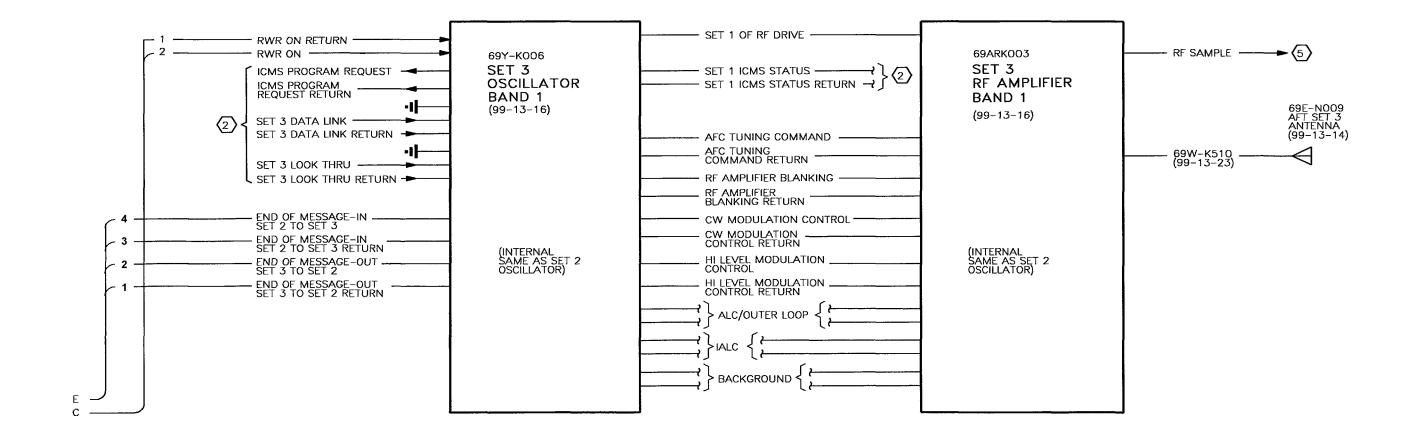

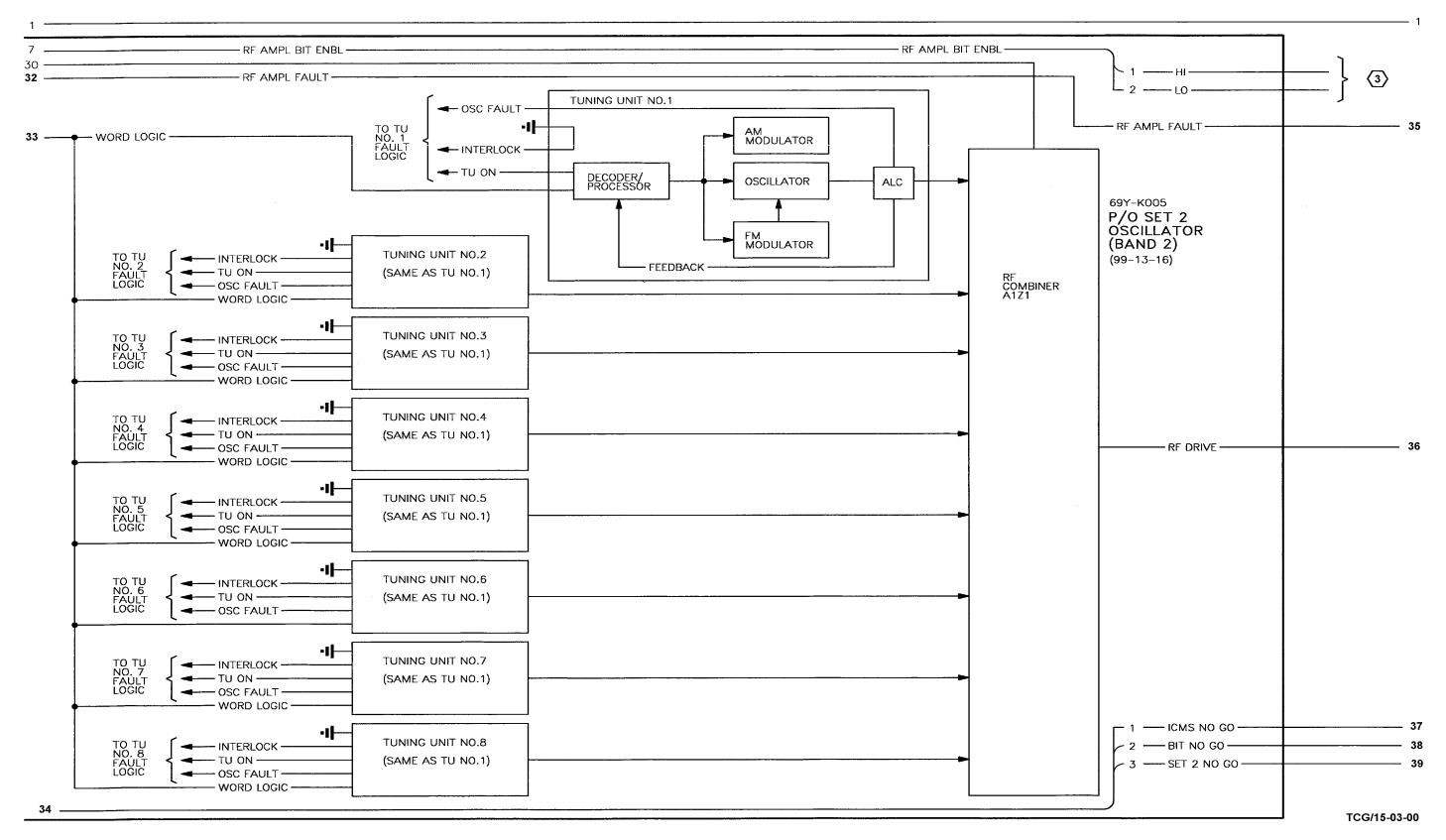

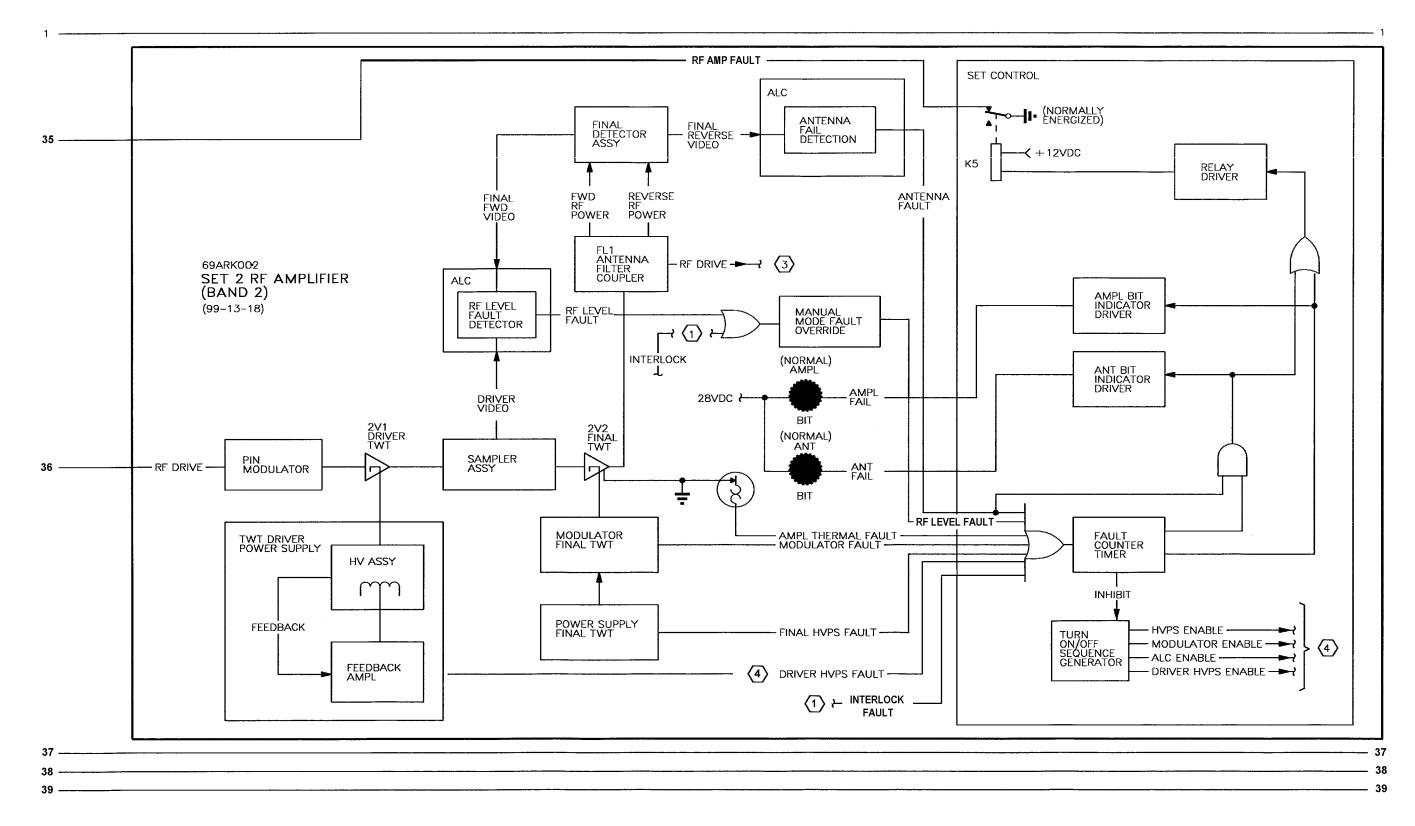

| 13-6      | ICMS Band 1 and 2 Transmit Circuits Simplified Schematic   | 13-38 |

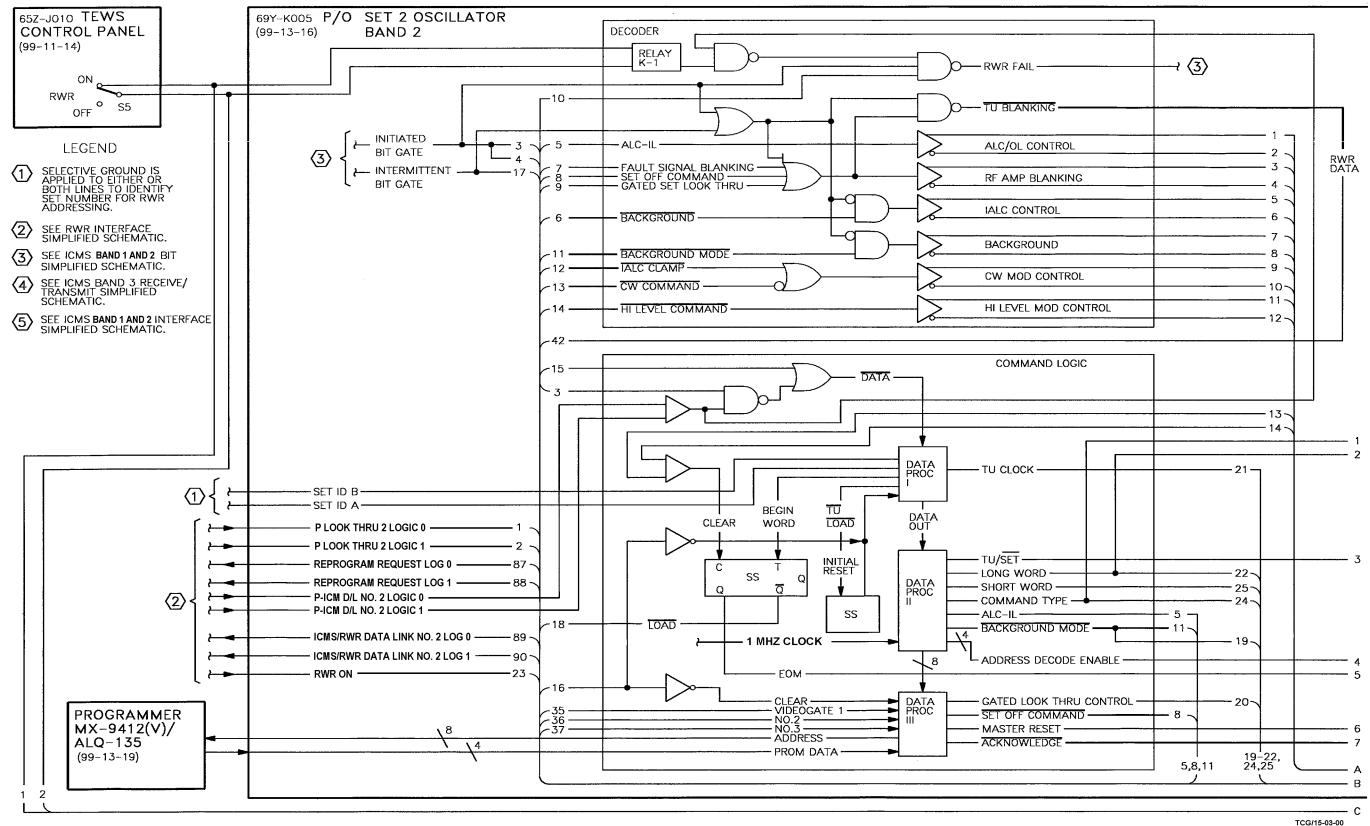

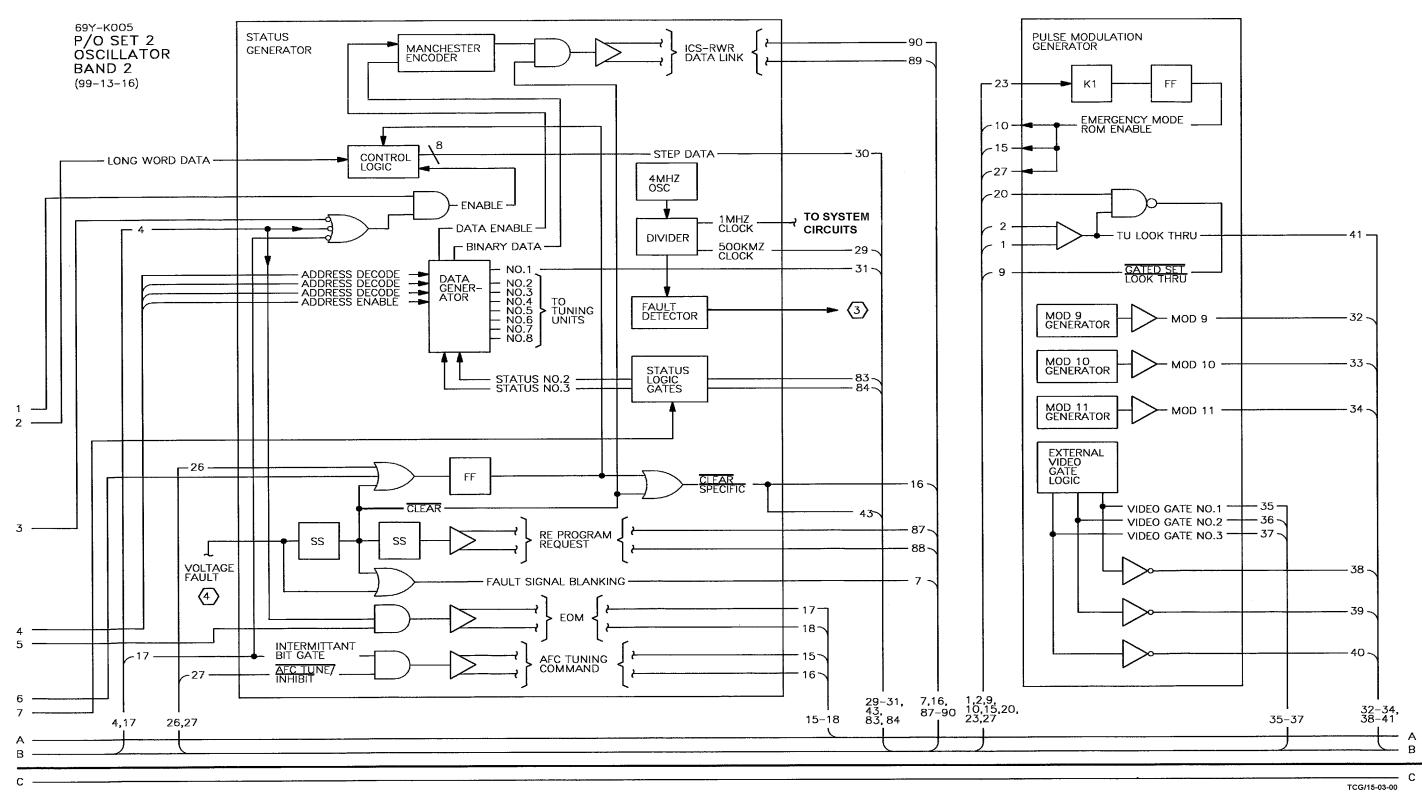

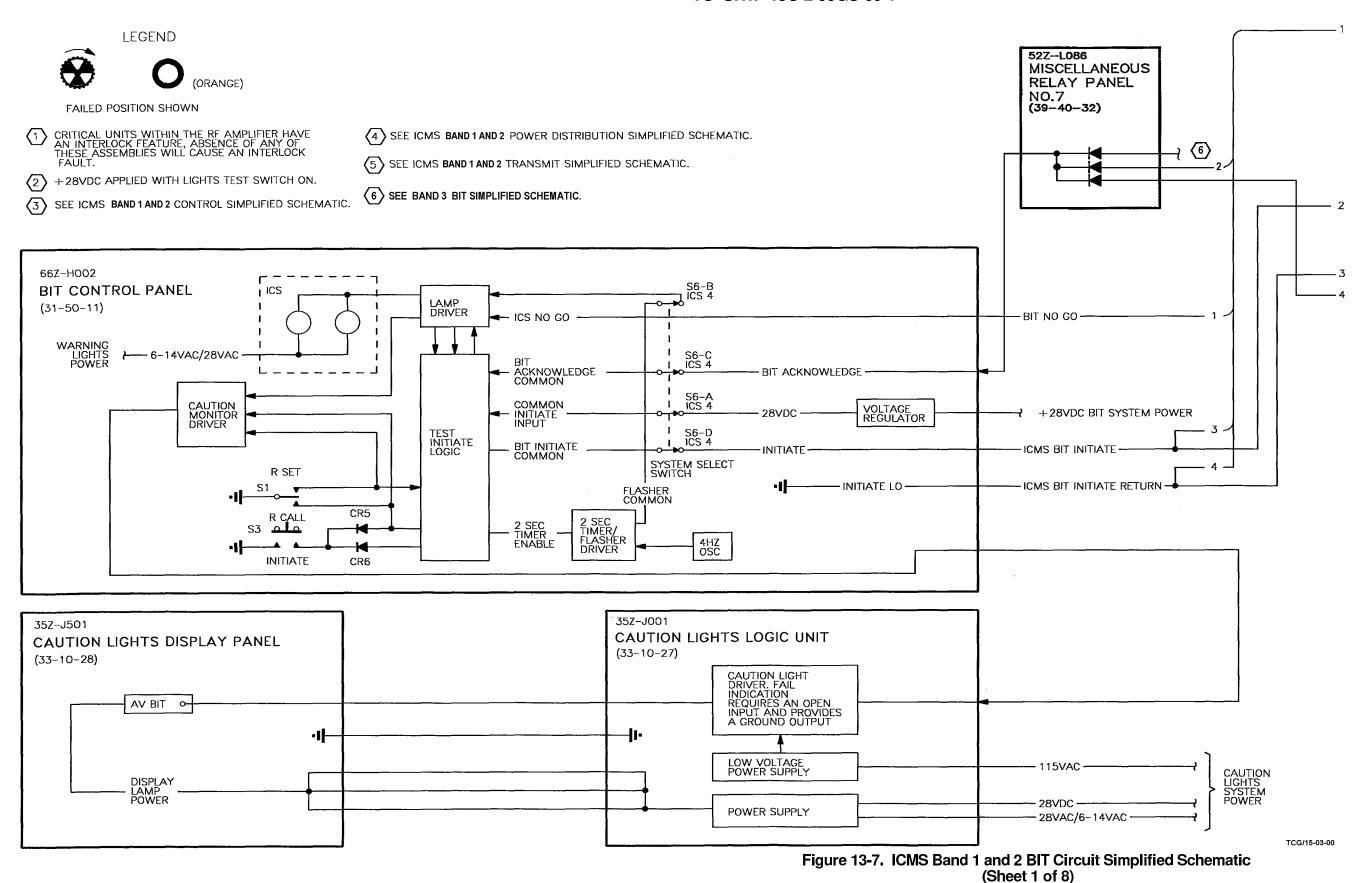

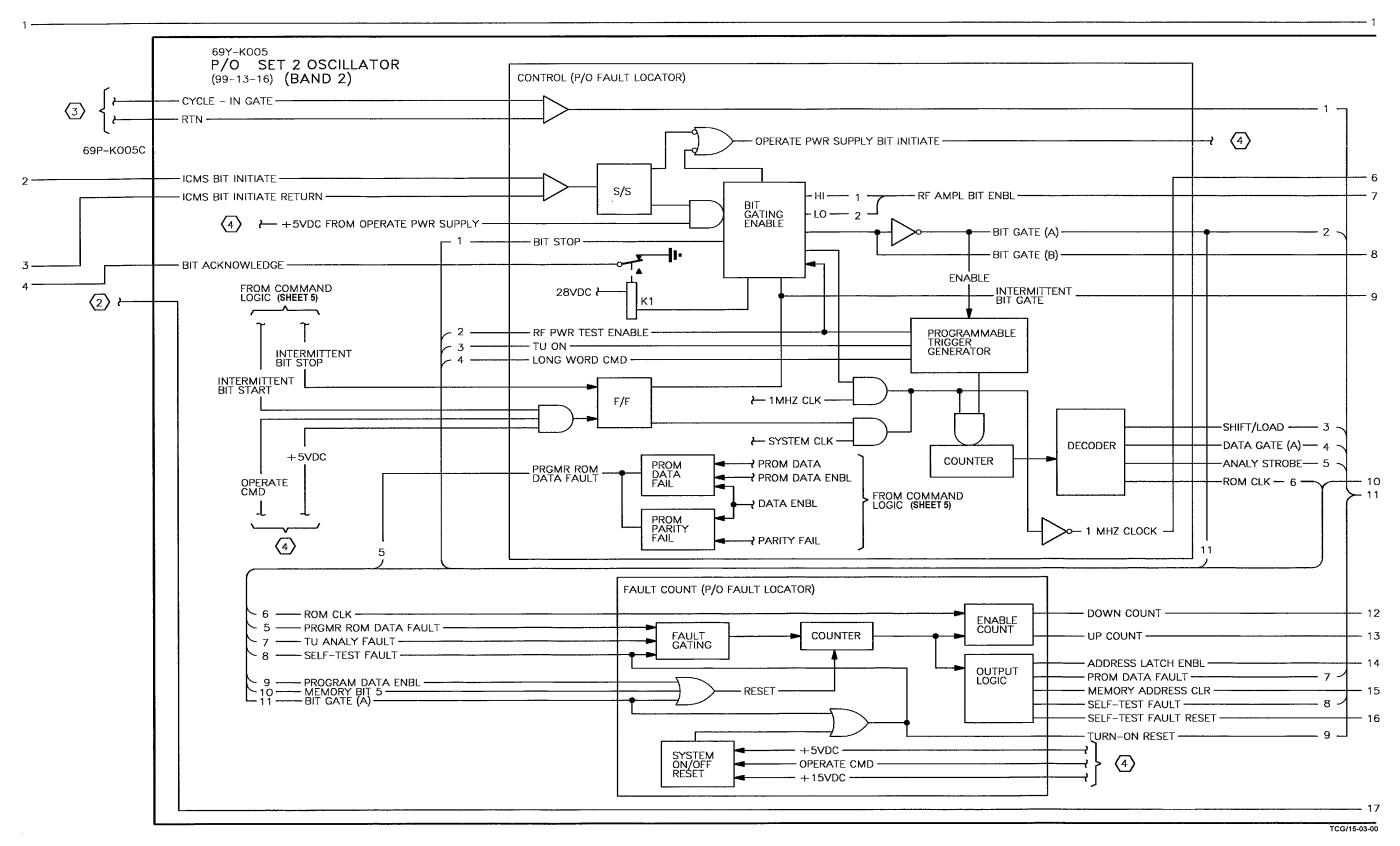

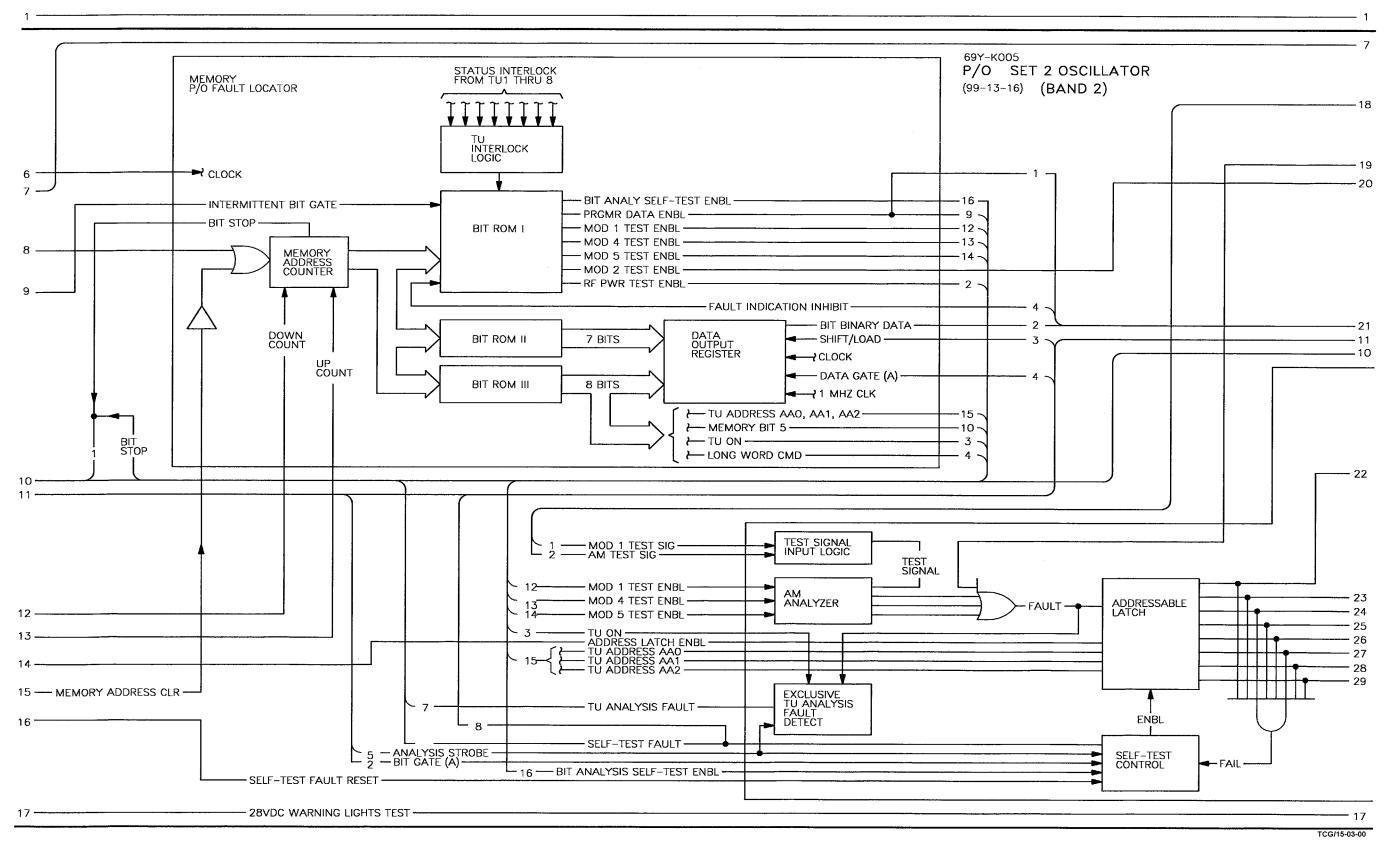

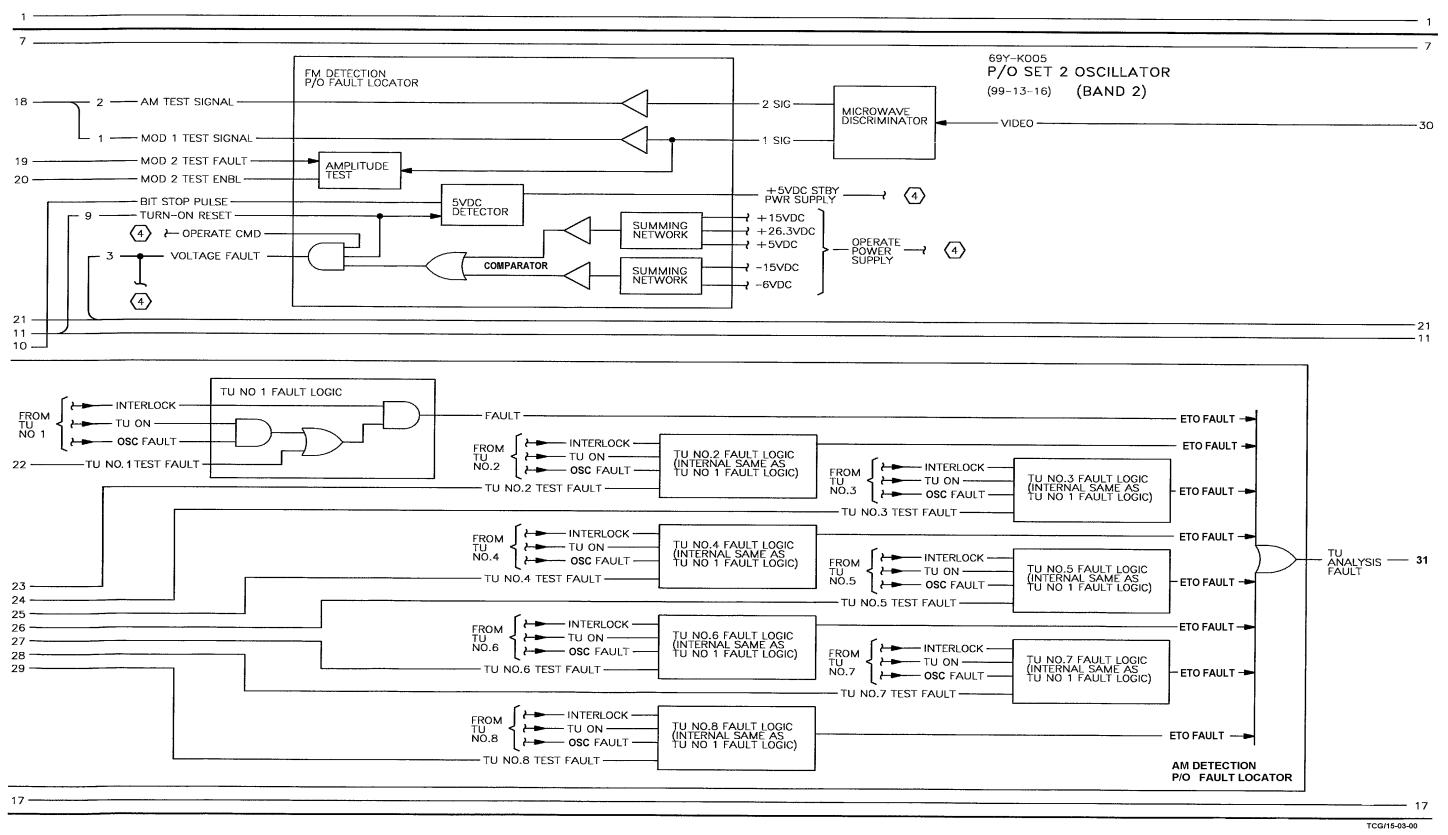

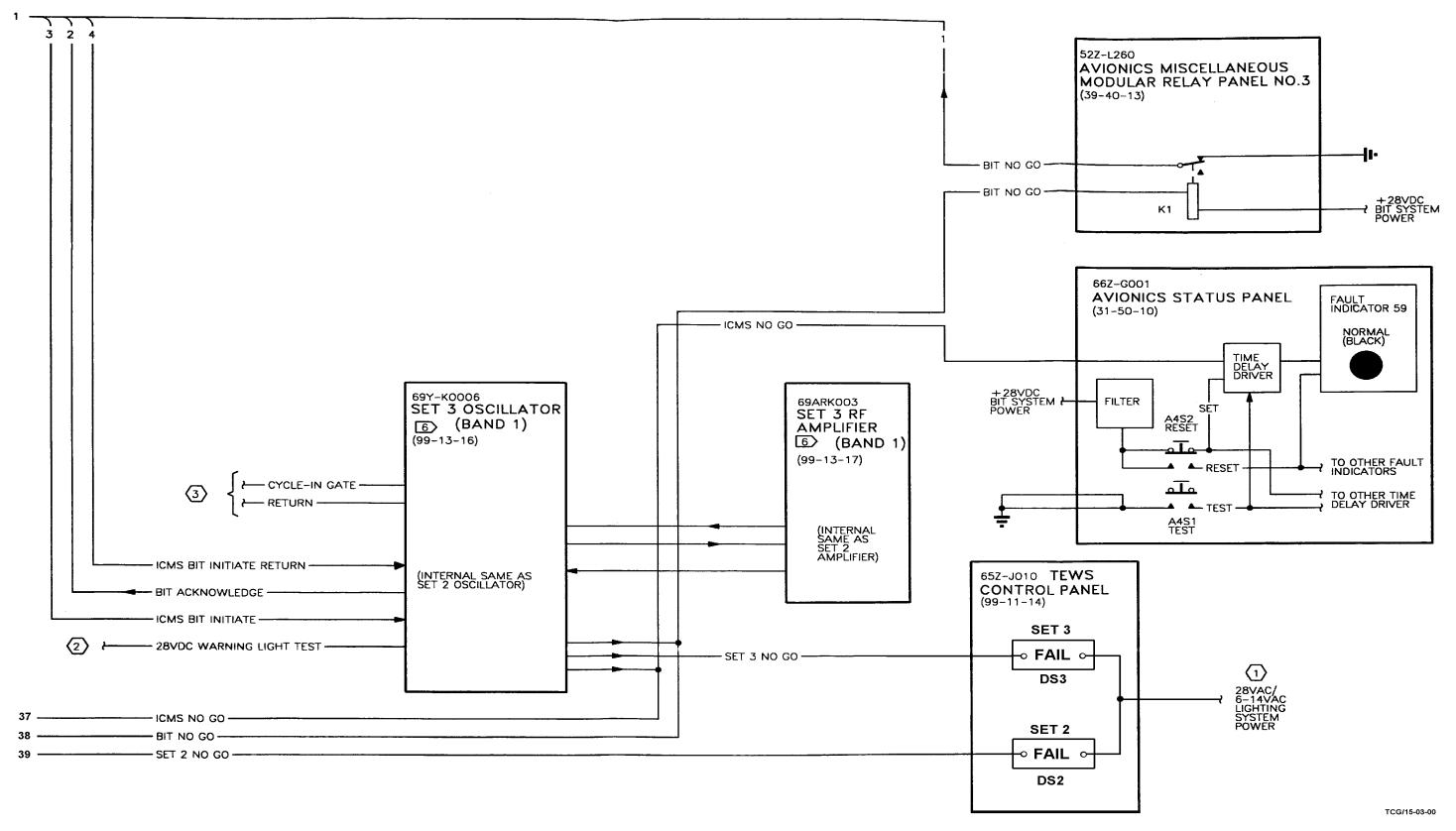

| 13-7      | ICMS Band 1 and 2 BIT Circuit Simplified Schematic         | 13-46 |

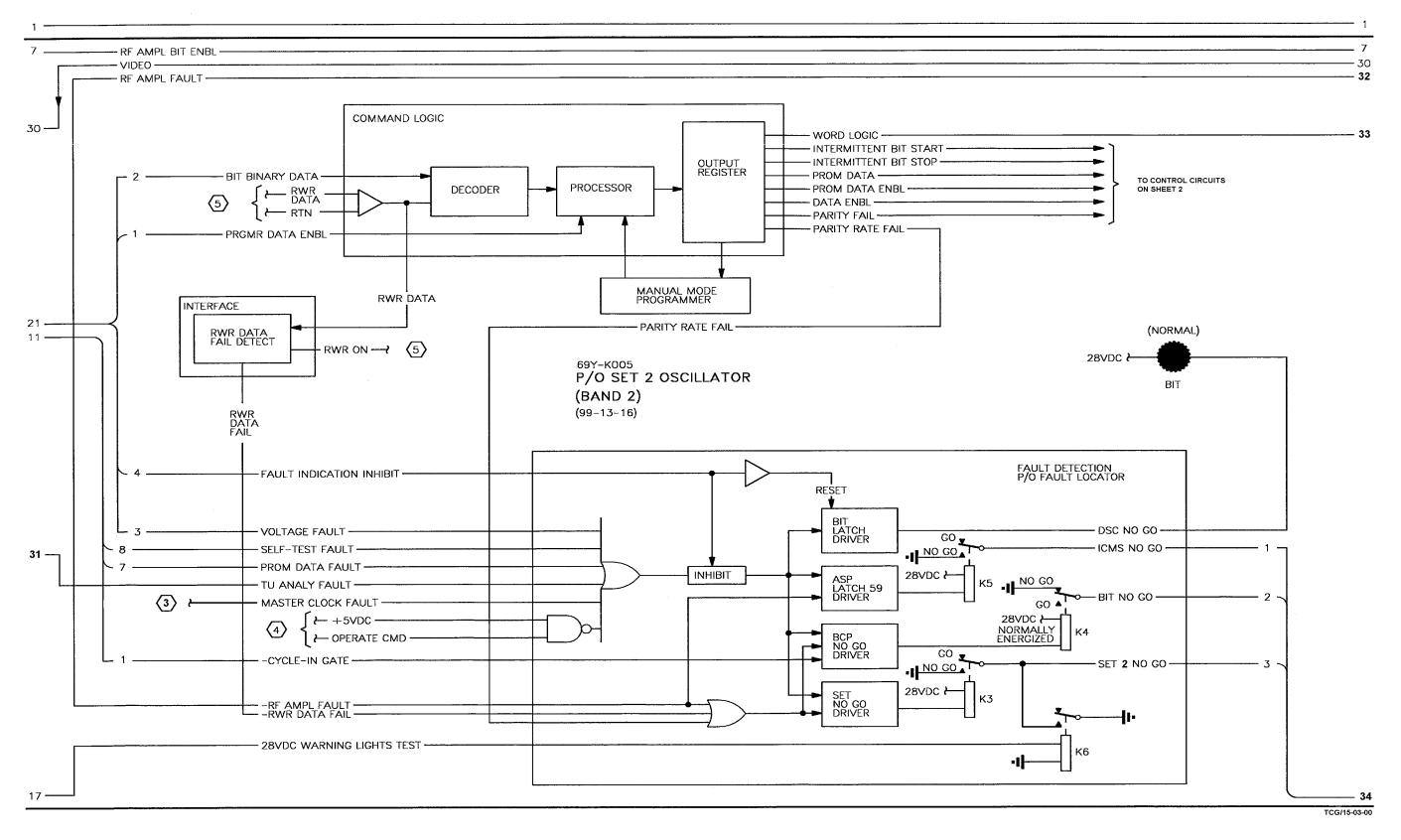

| 13-8      | ICMS Band 1 and 2 Interface Simplified Schematic           | 13-54 |

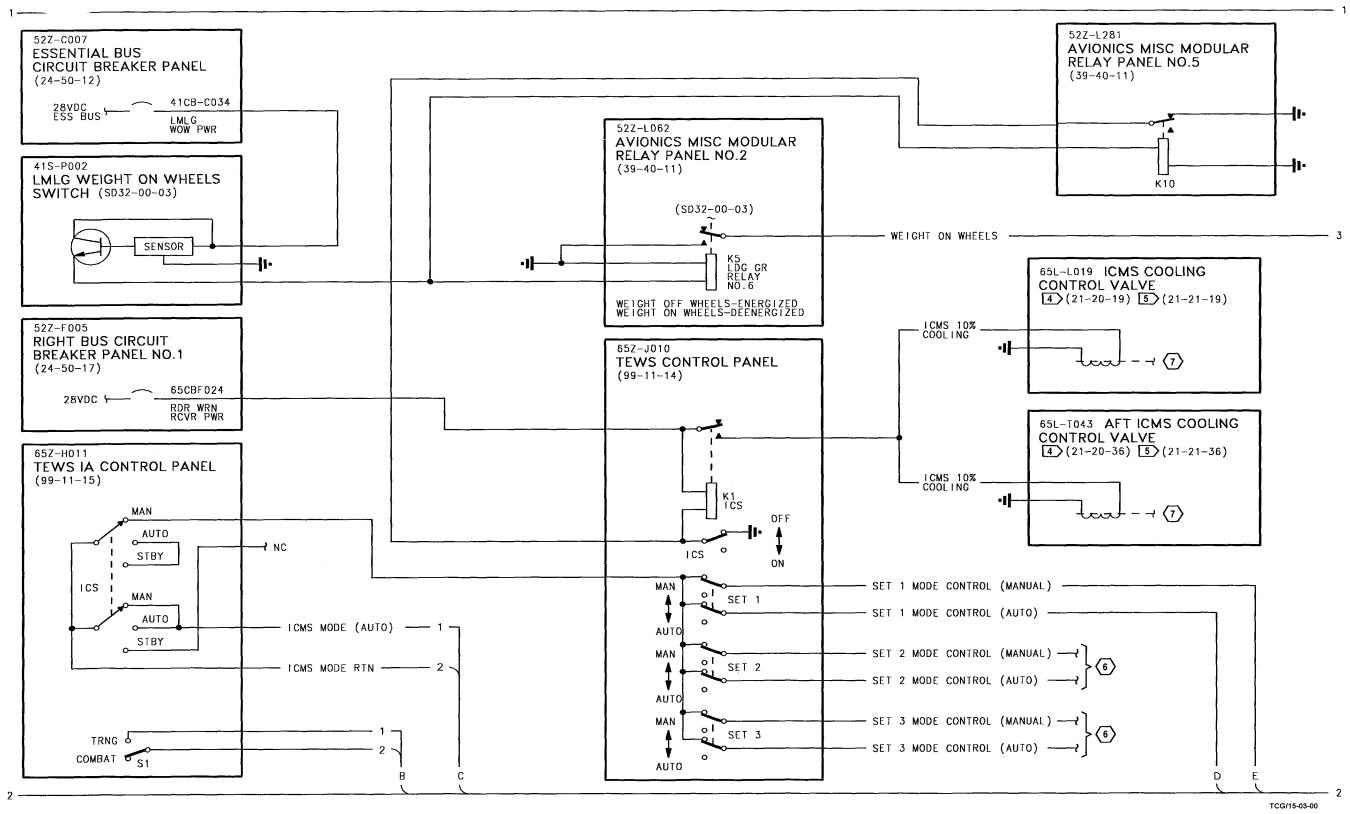

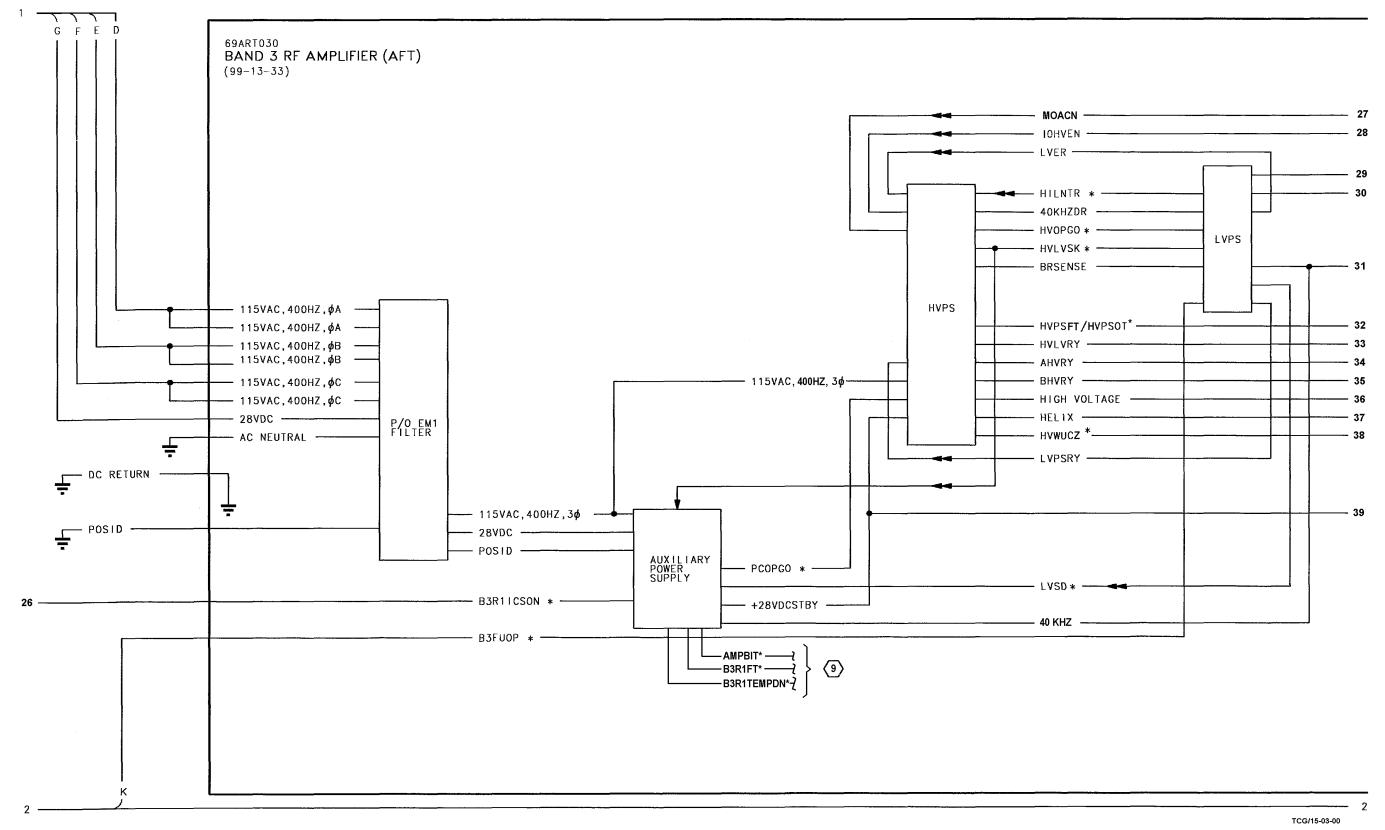

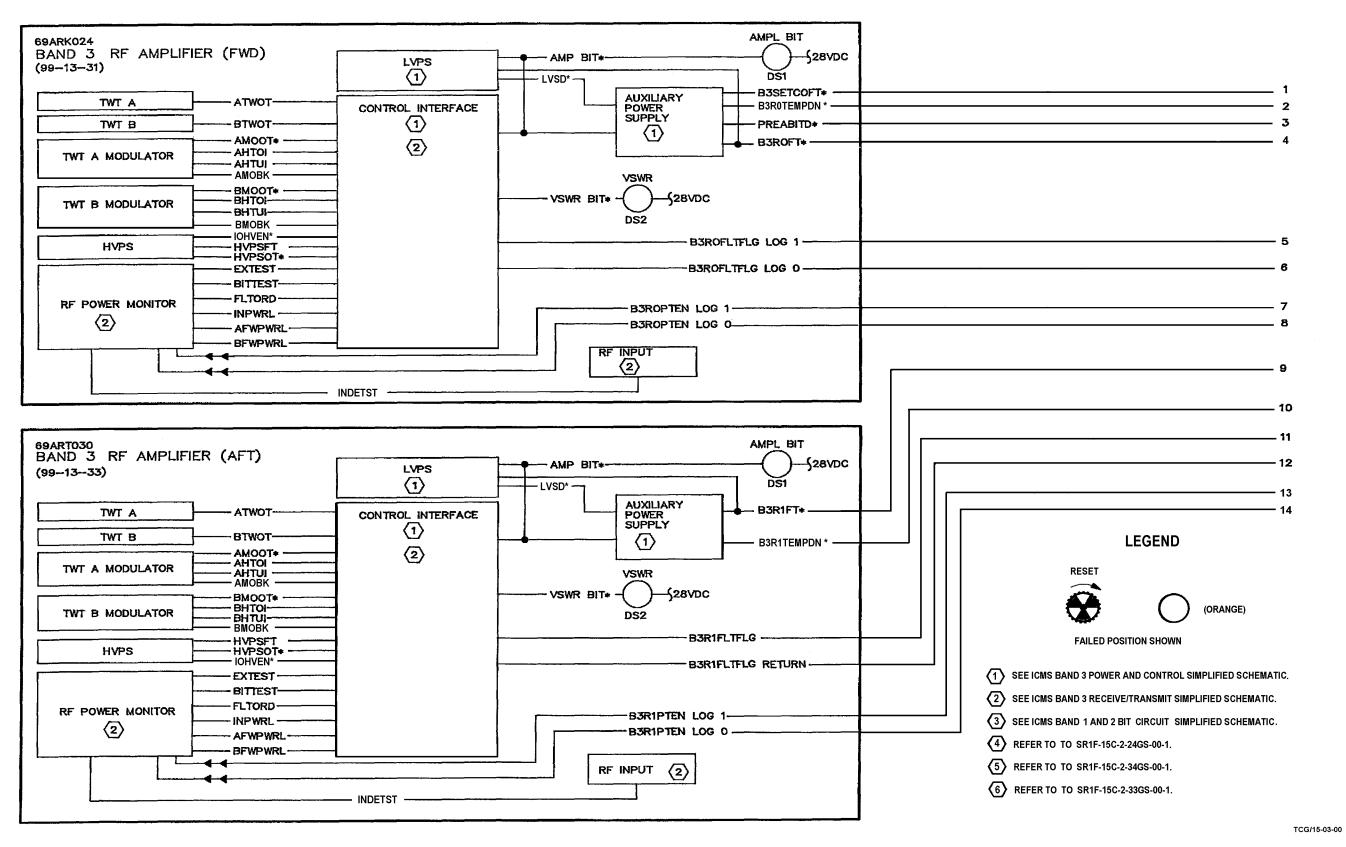

| 13-9      | ICMS Band 3 Power and Control Simplified Schematic         | 13-61 |

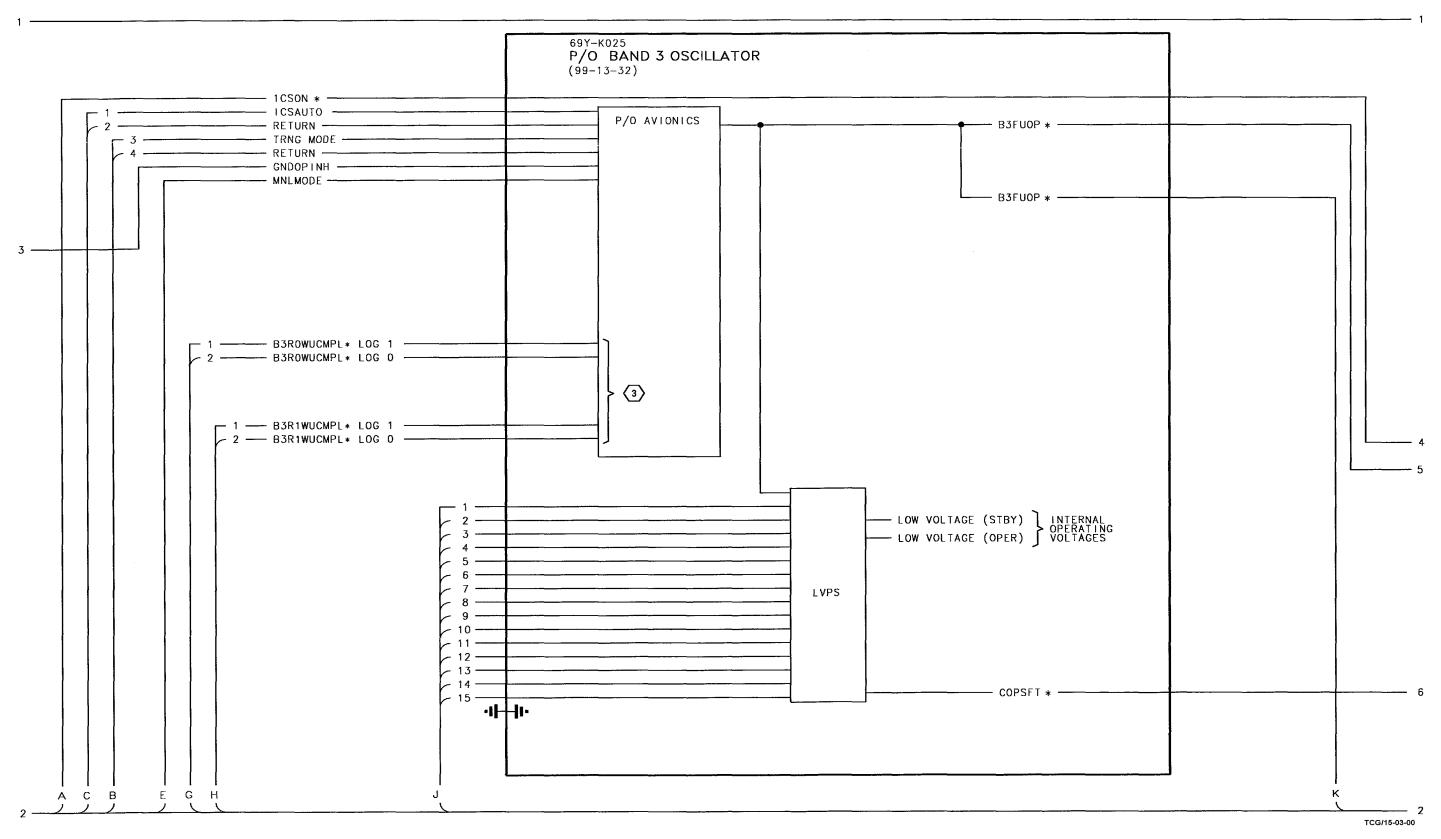

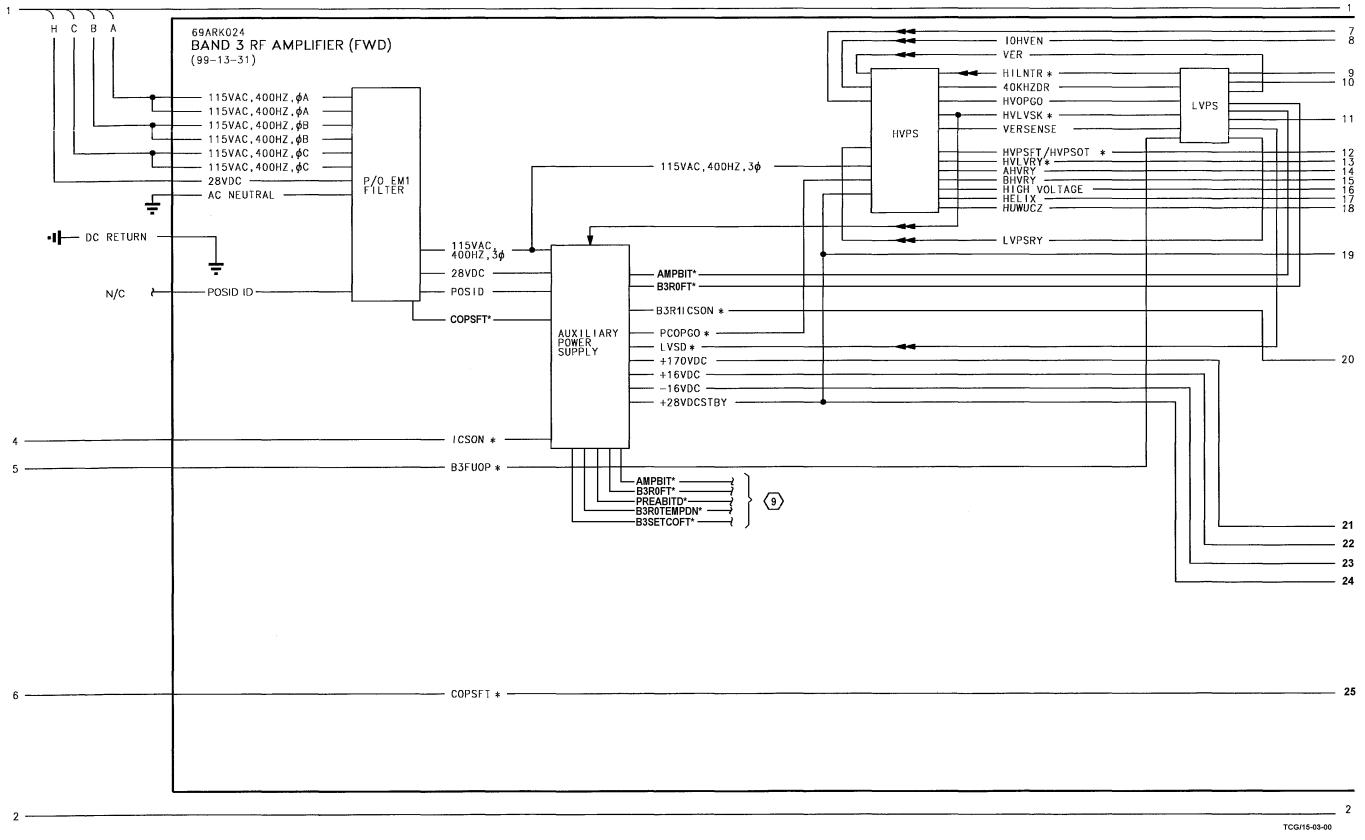

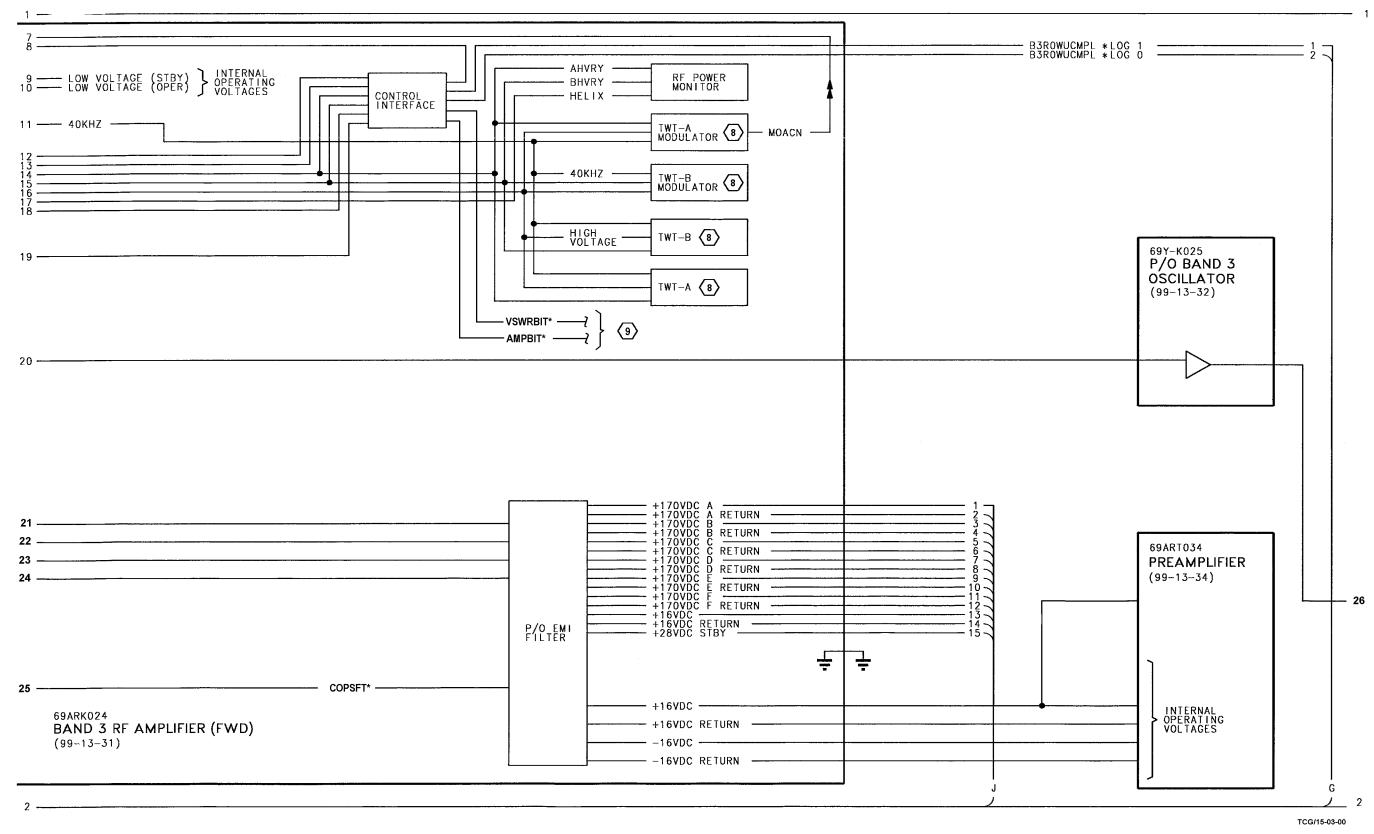

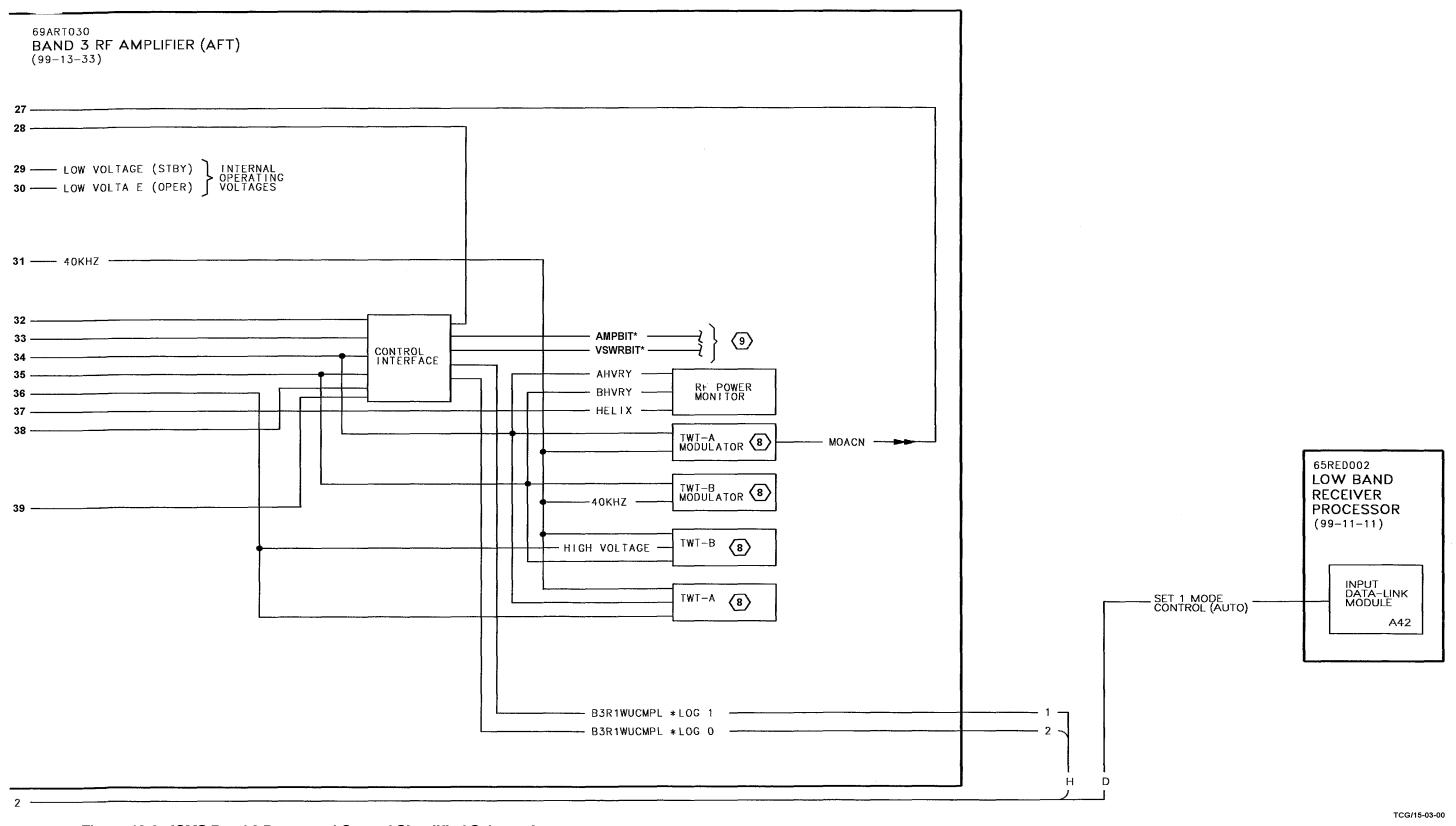

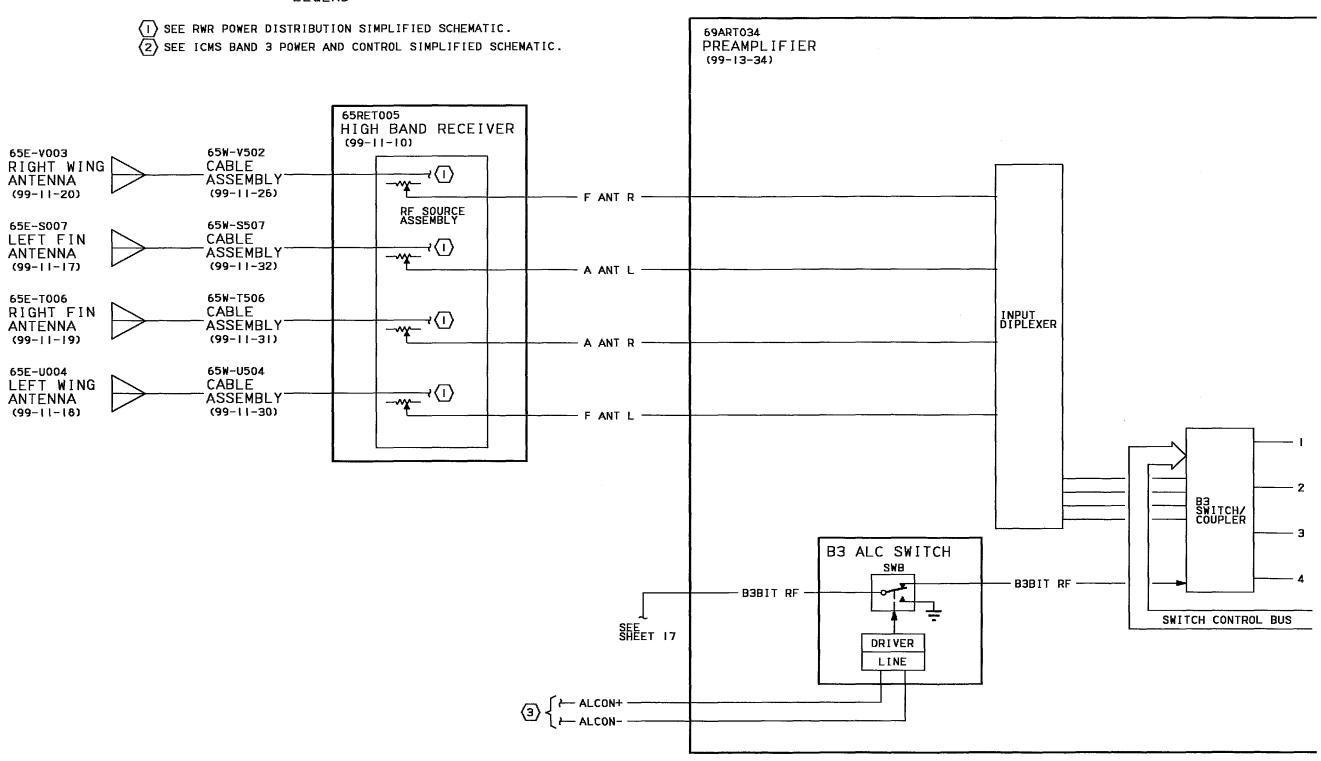

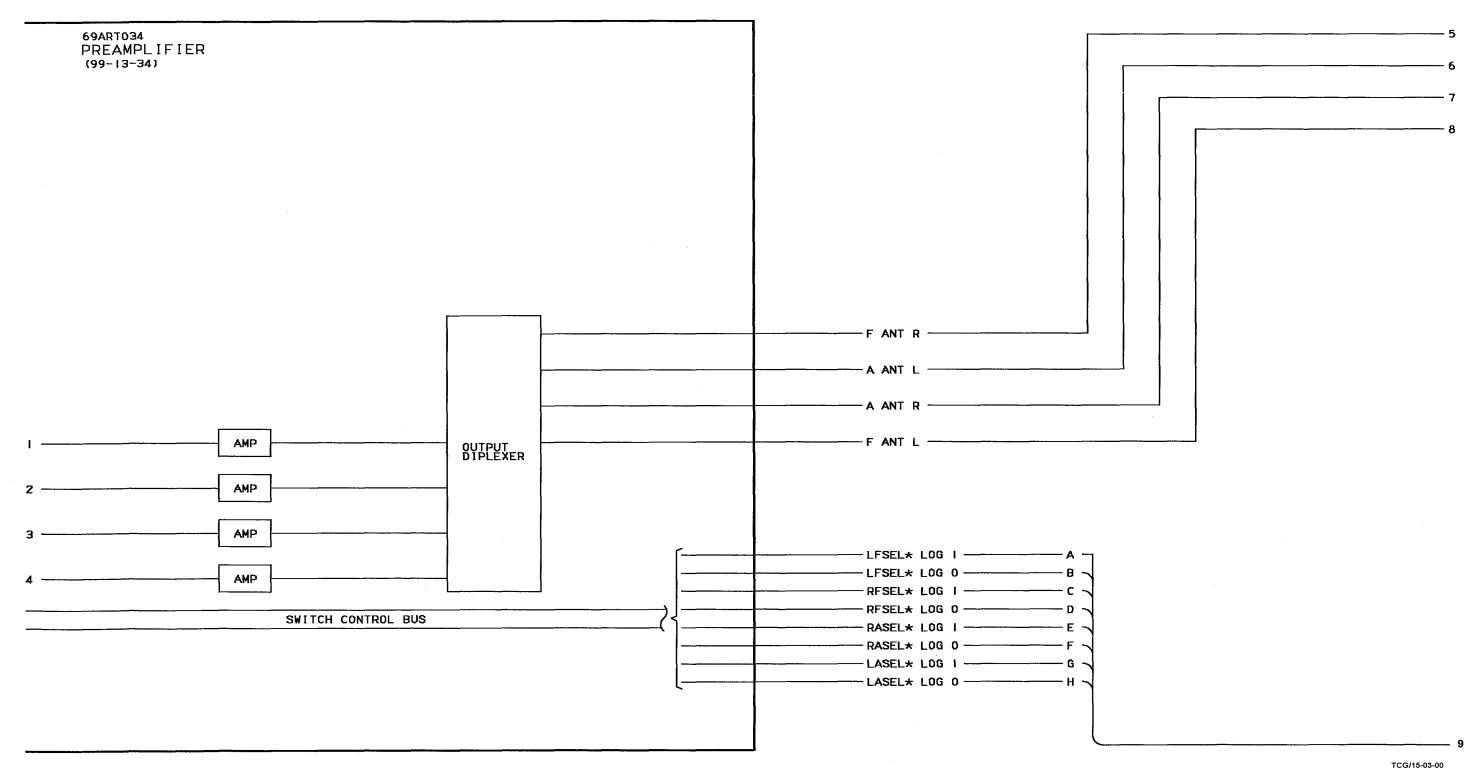

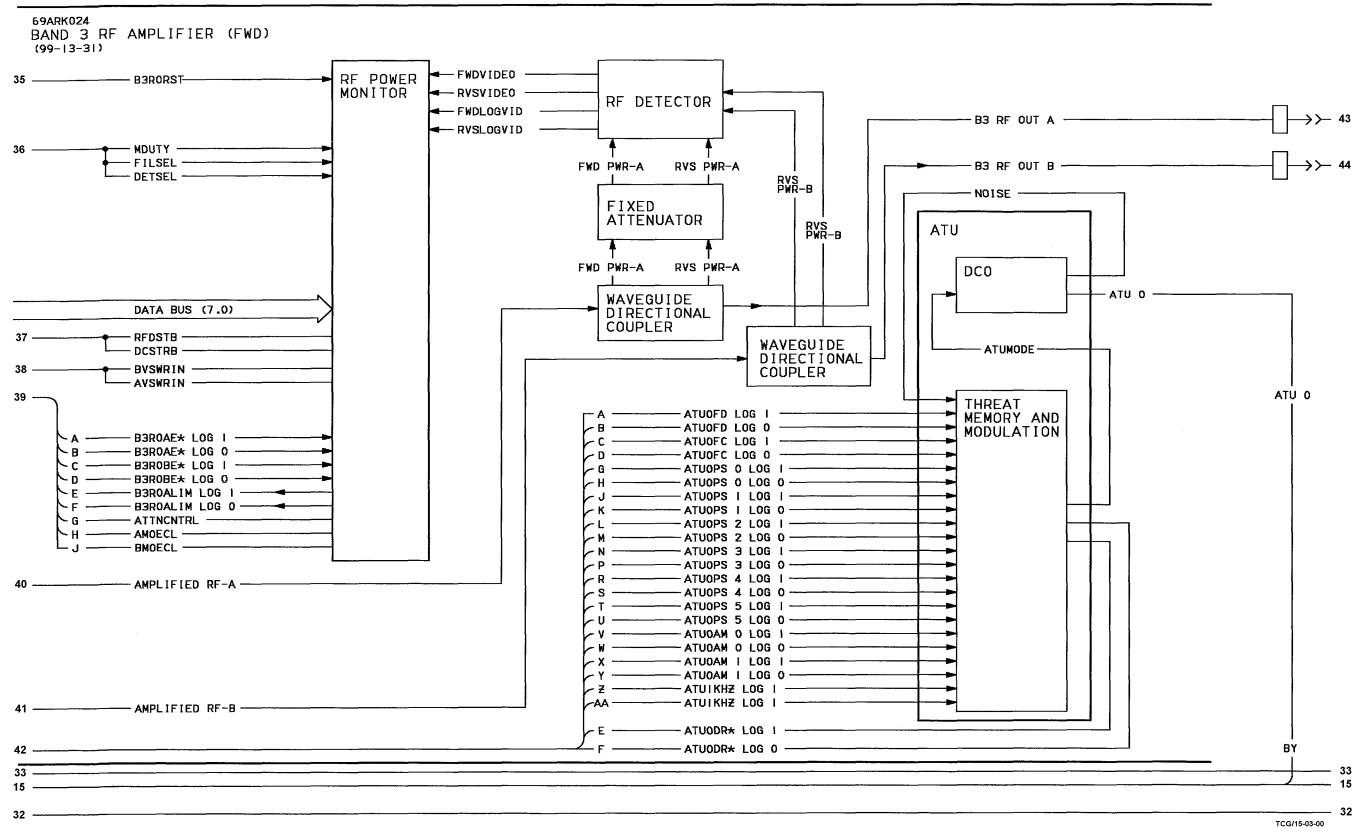

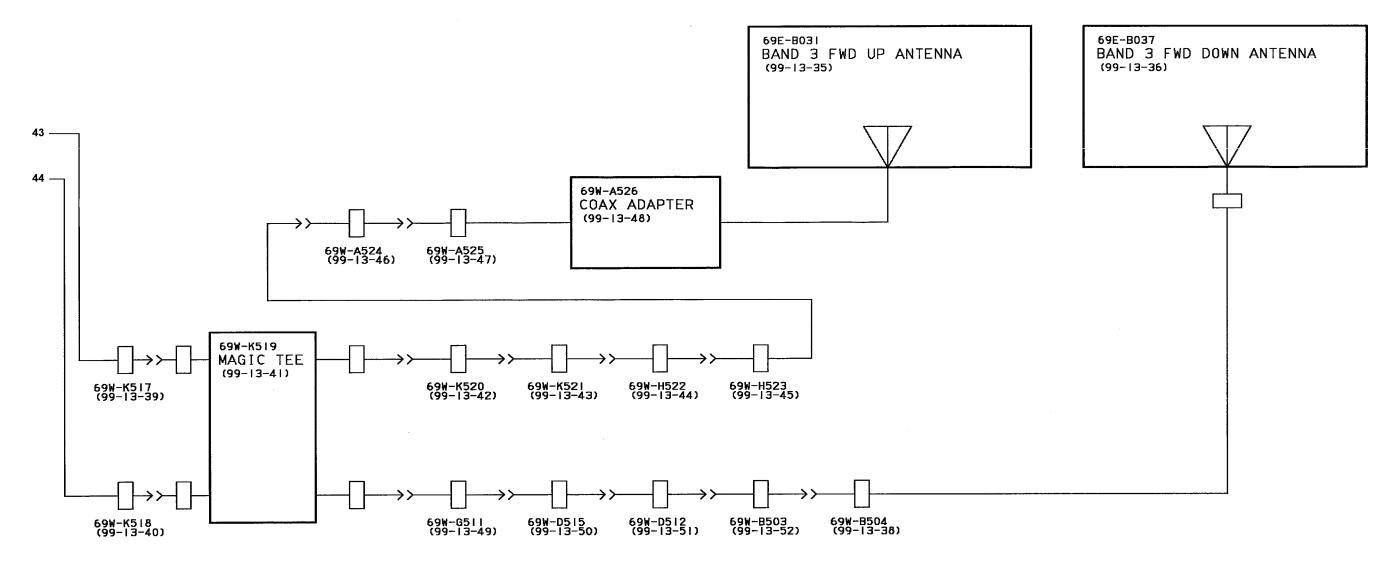

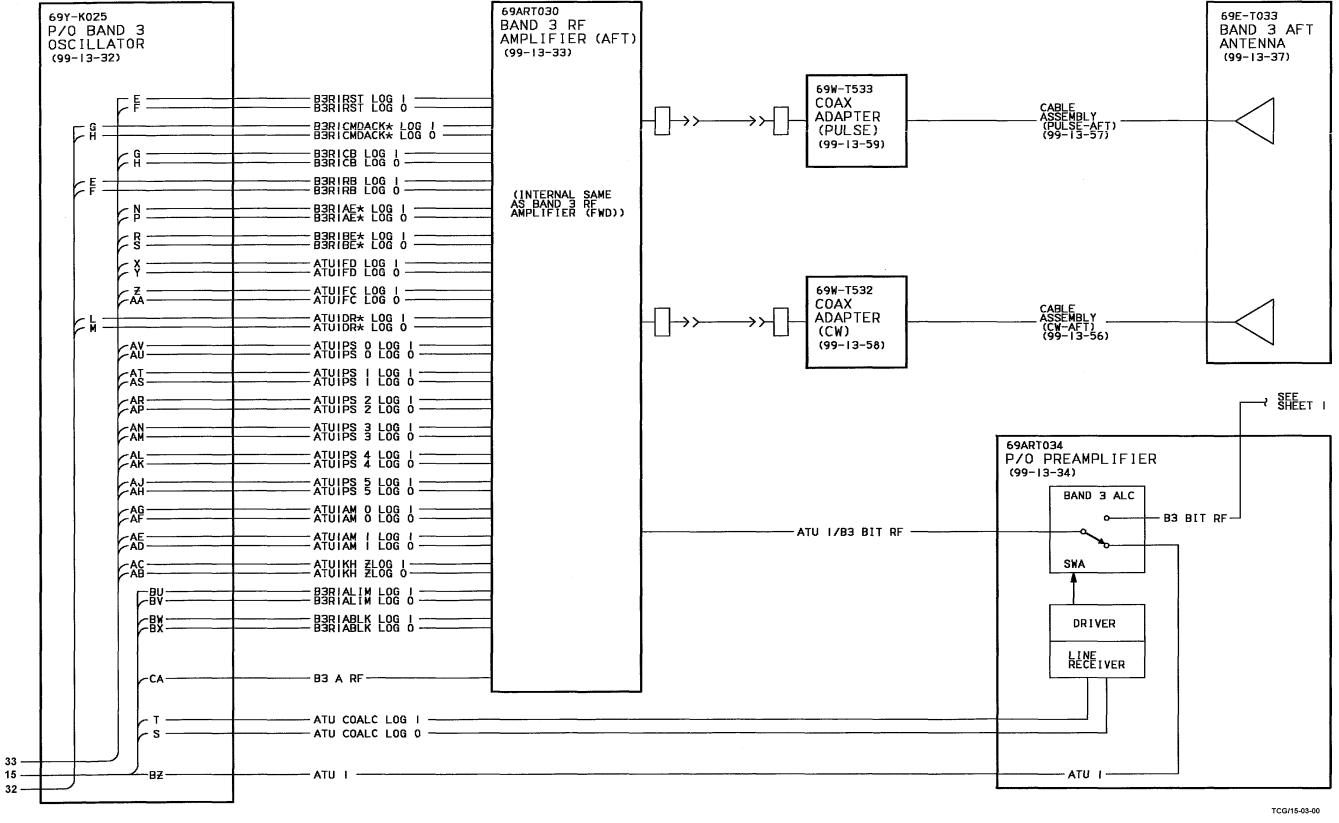

| 13-10     | ICMS Band 3 Receive/Transmit Simplified Schematic          | 13-68 |

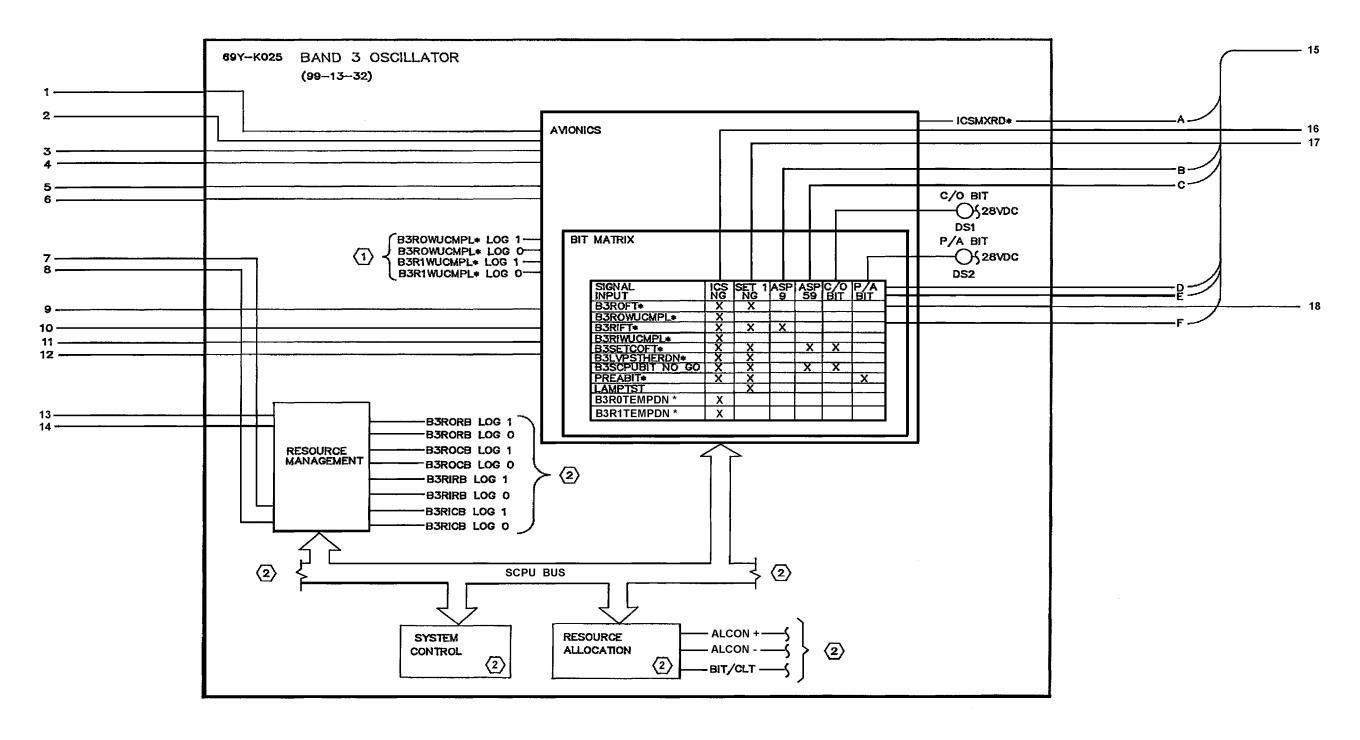

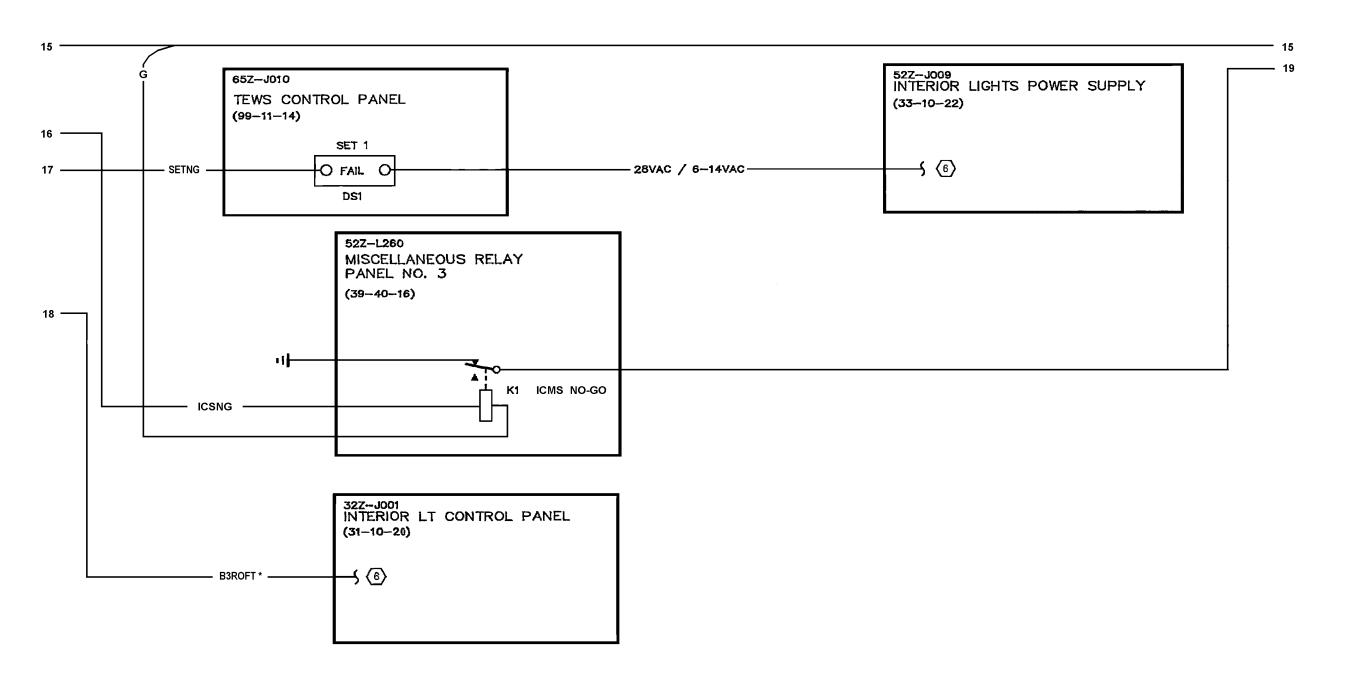

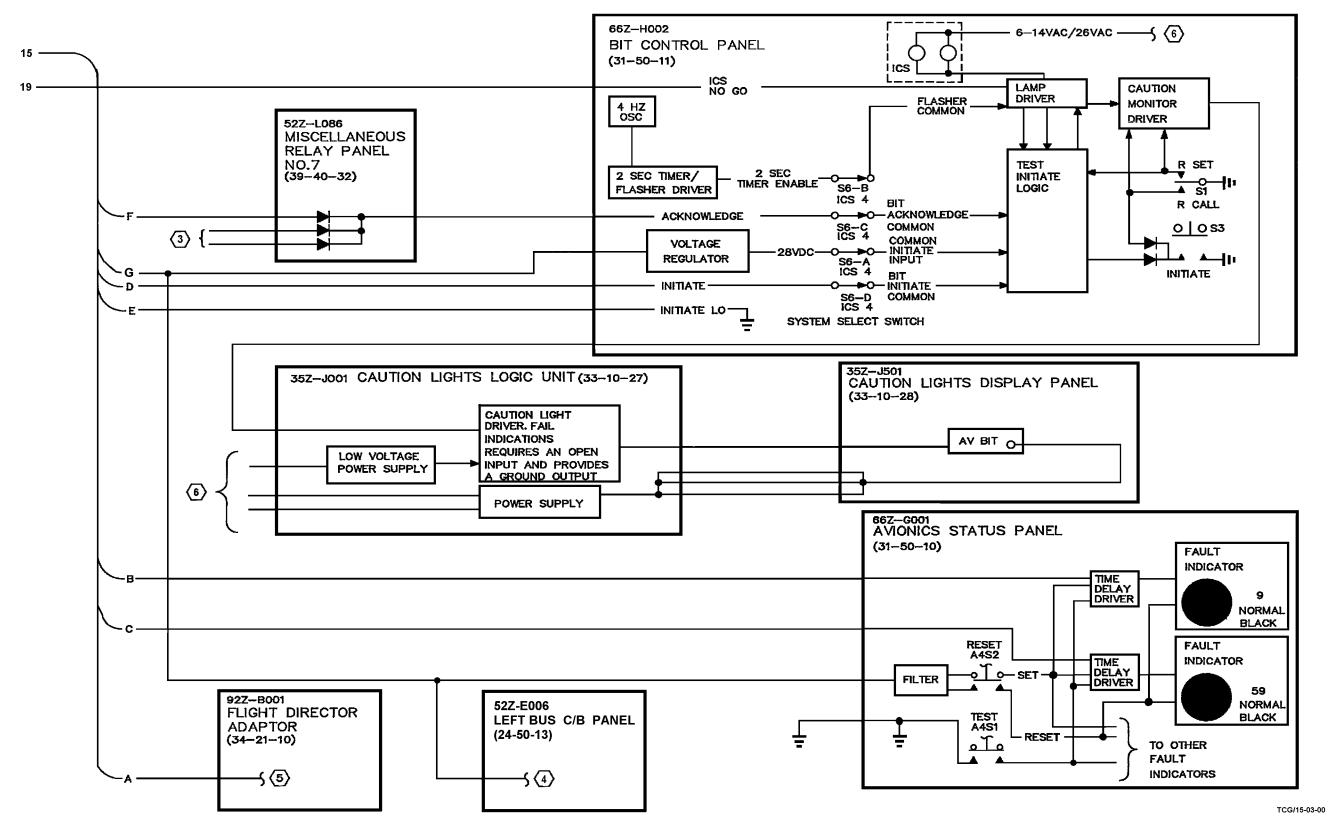

| 13-11     | ICMS Band 3 BIT Circuit Simplified Schematic               | 13-85 |

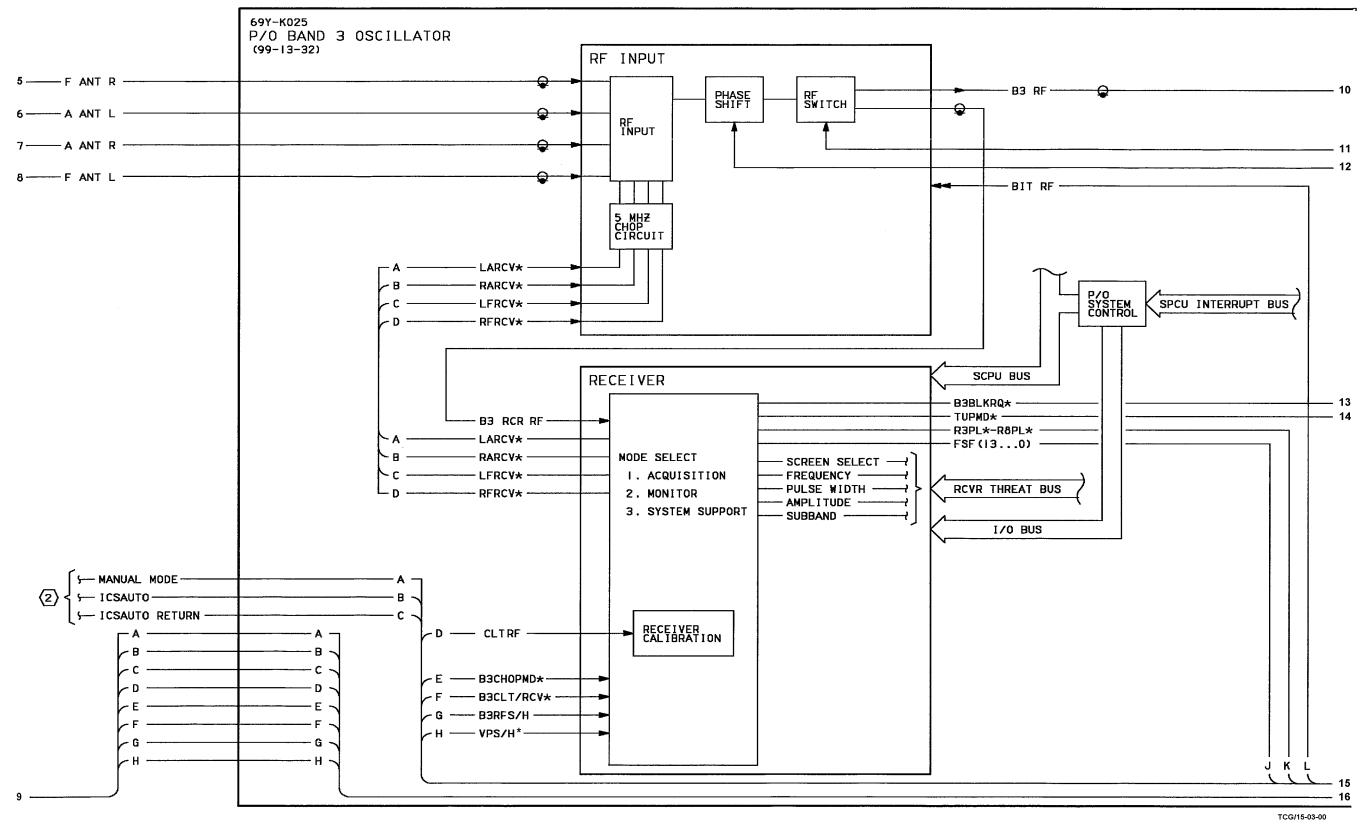

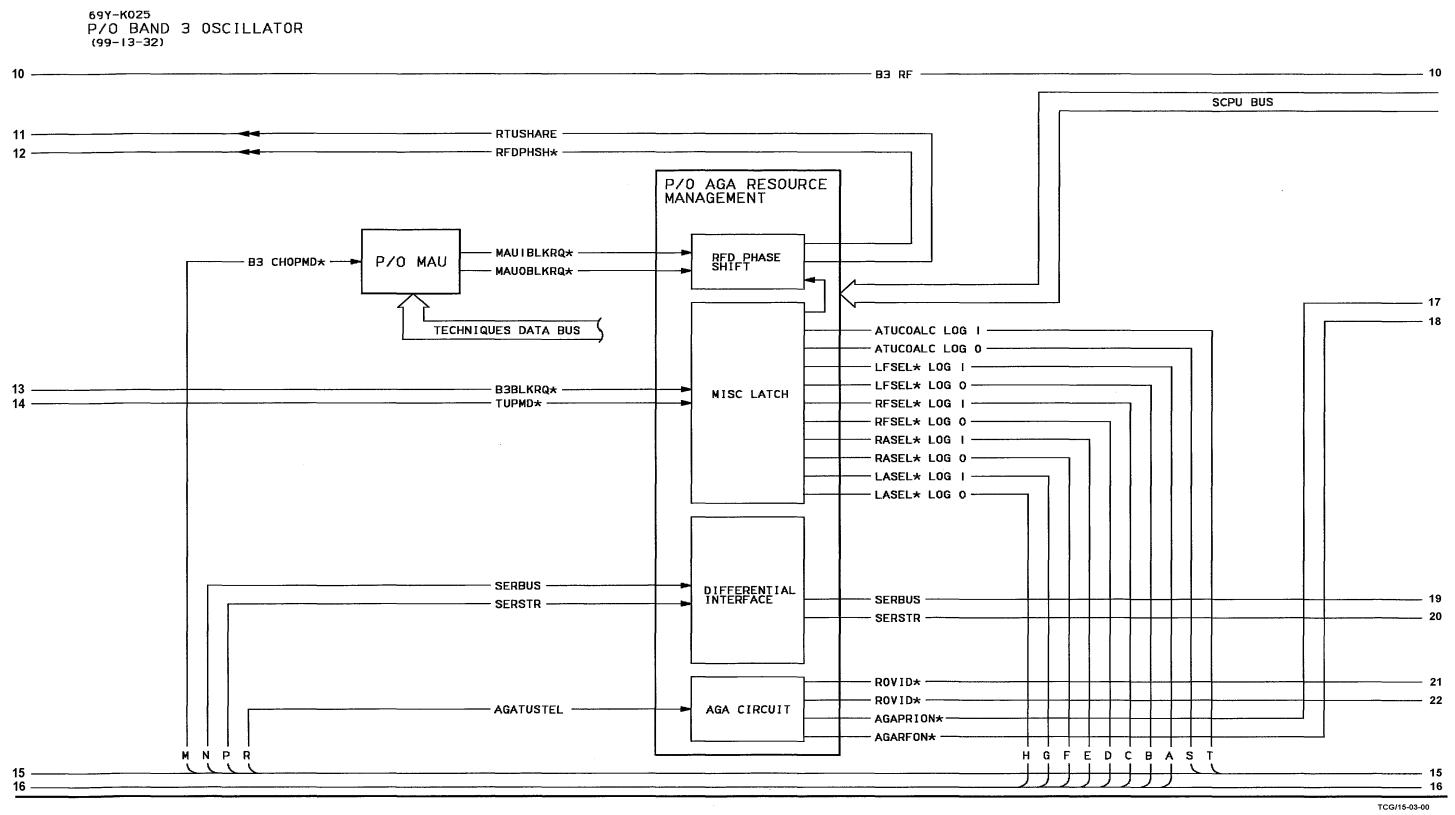

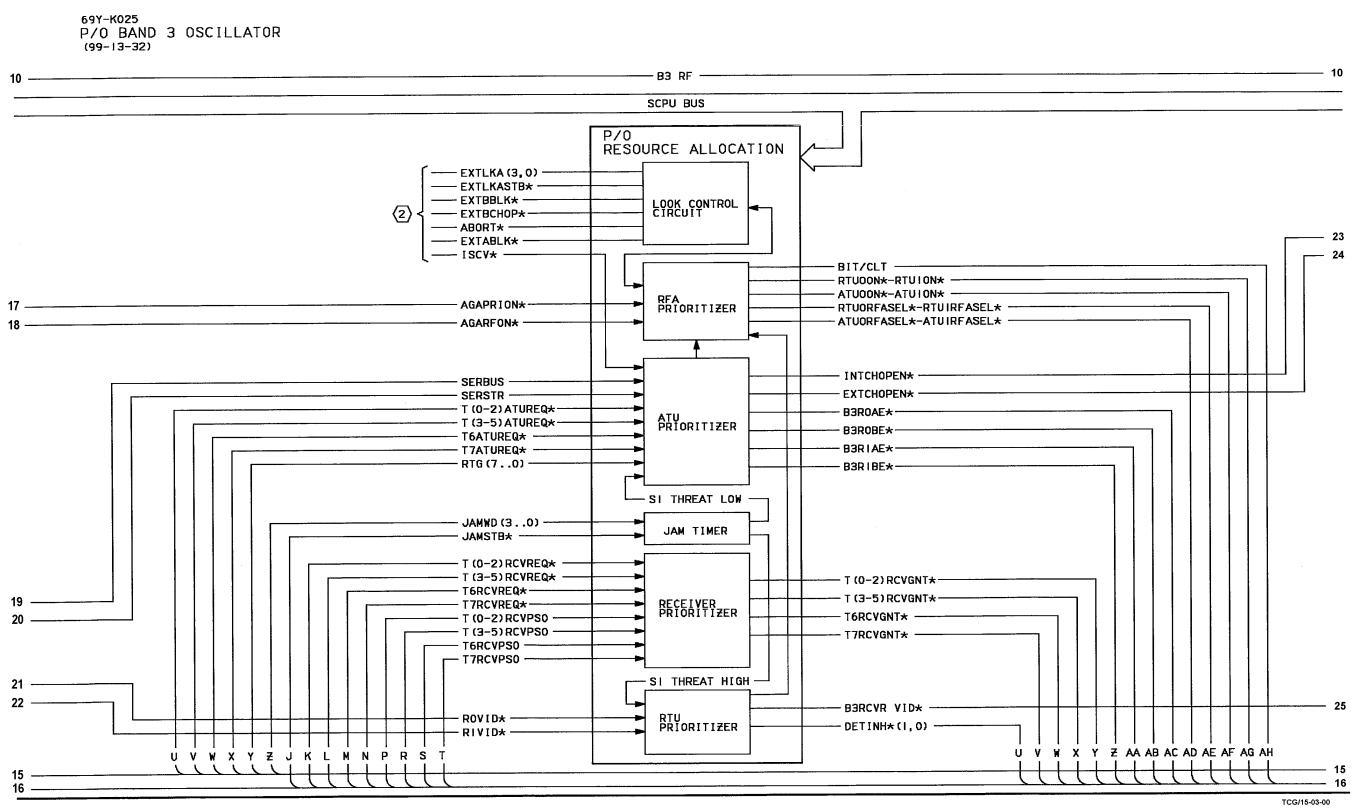

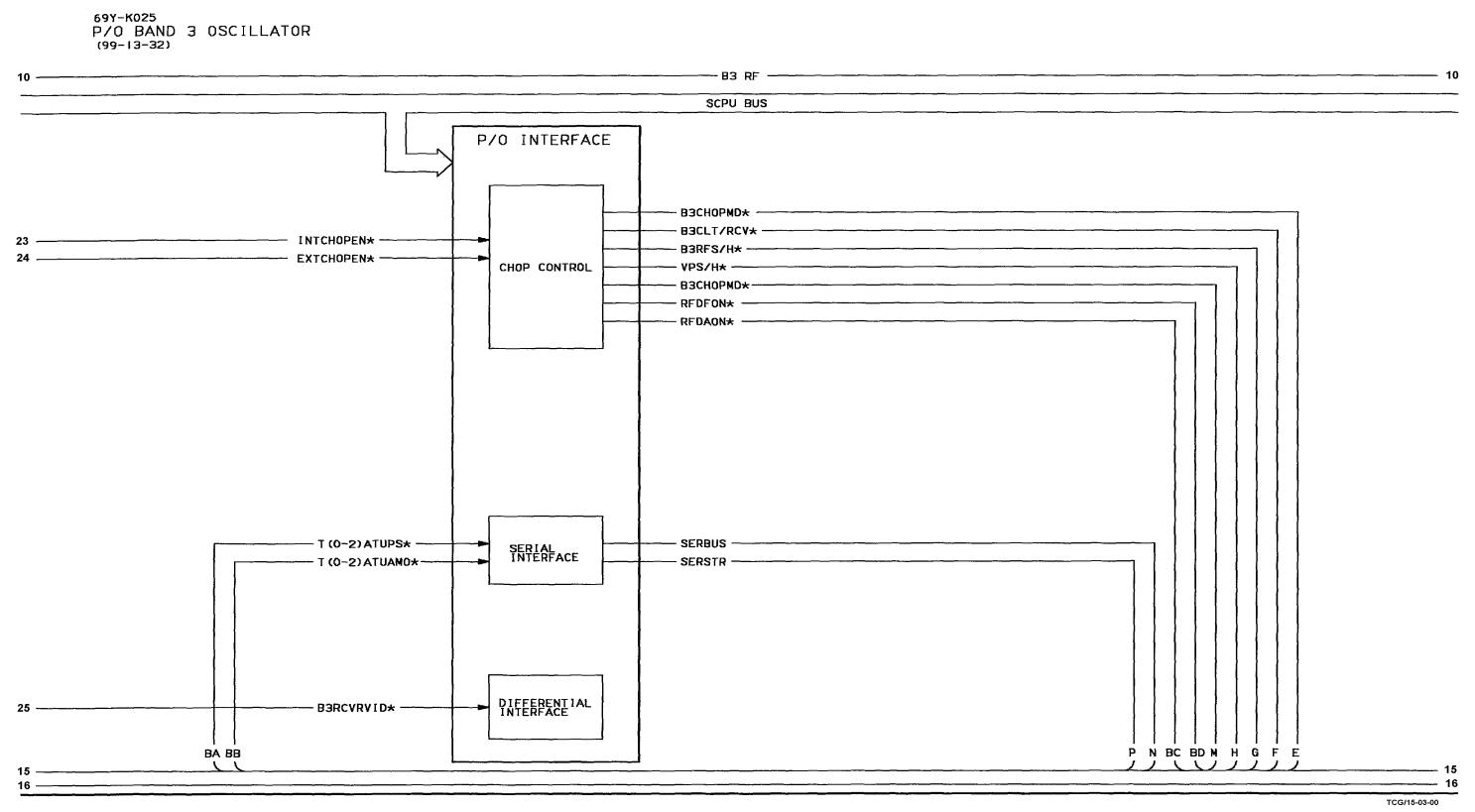

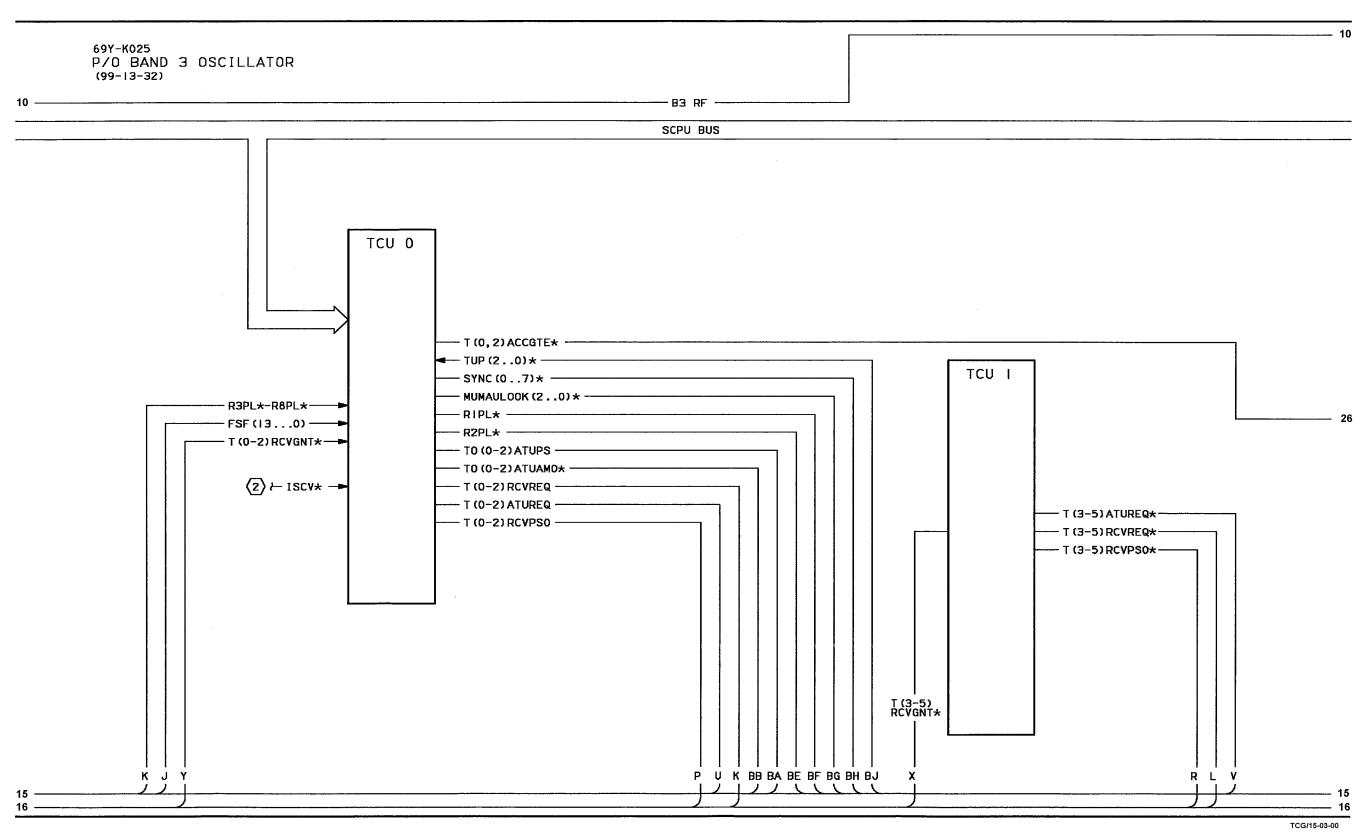

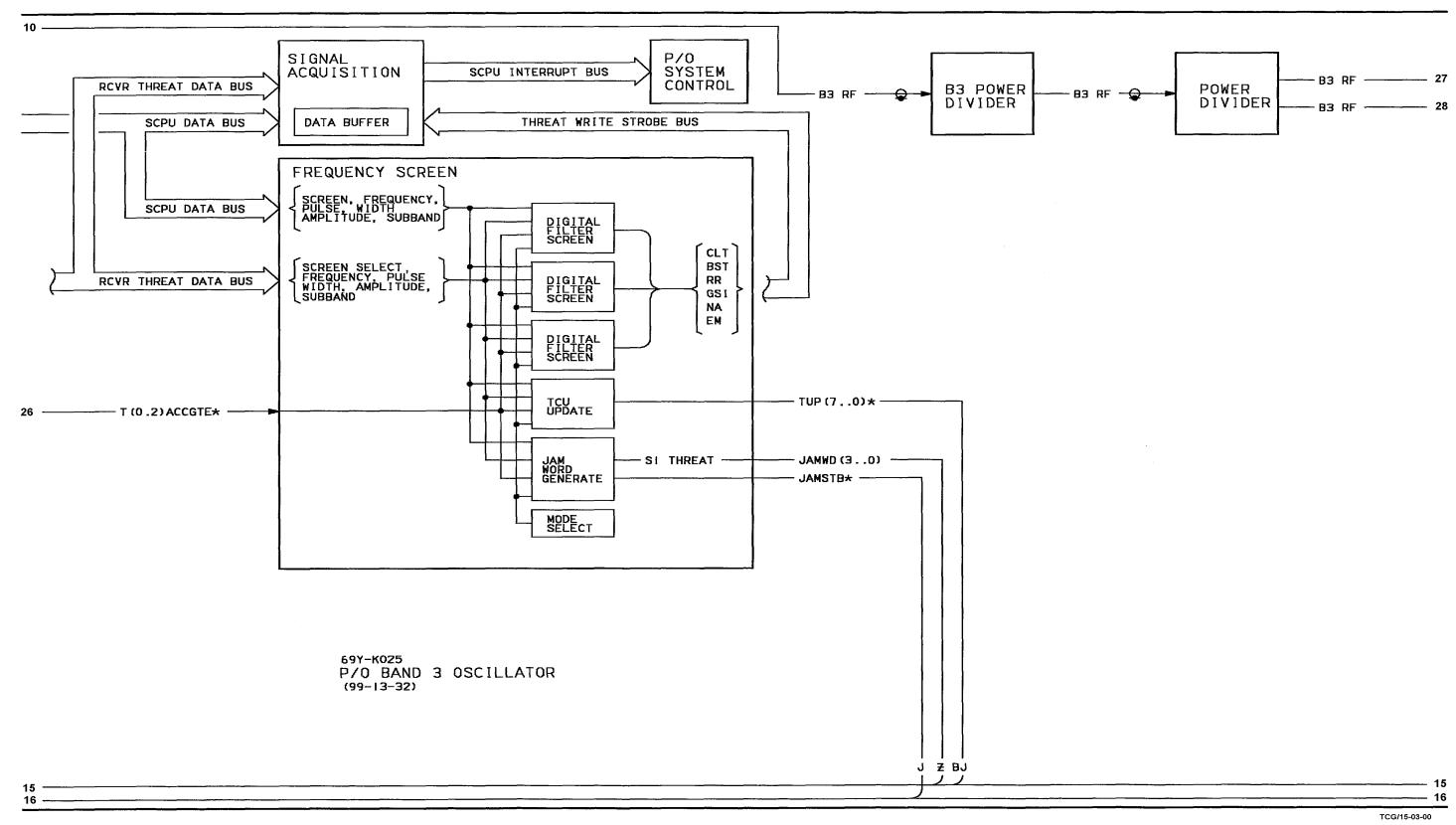

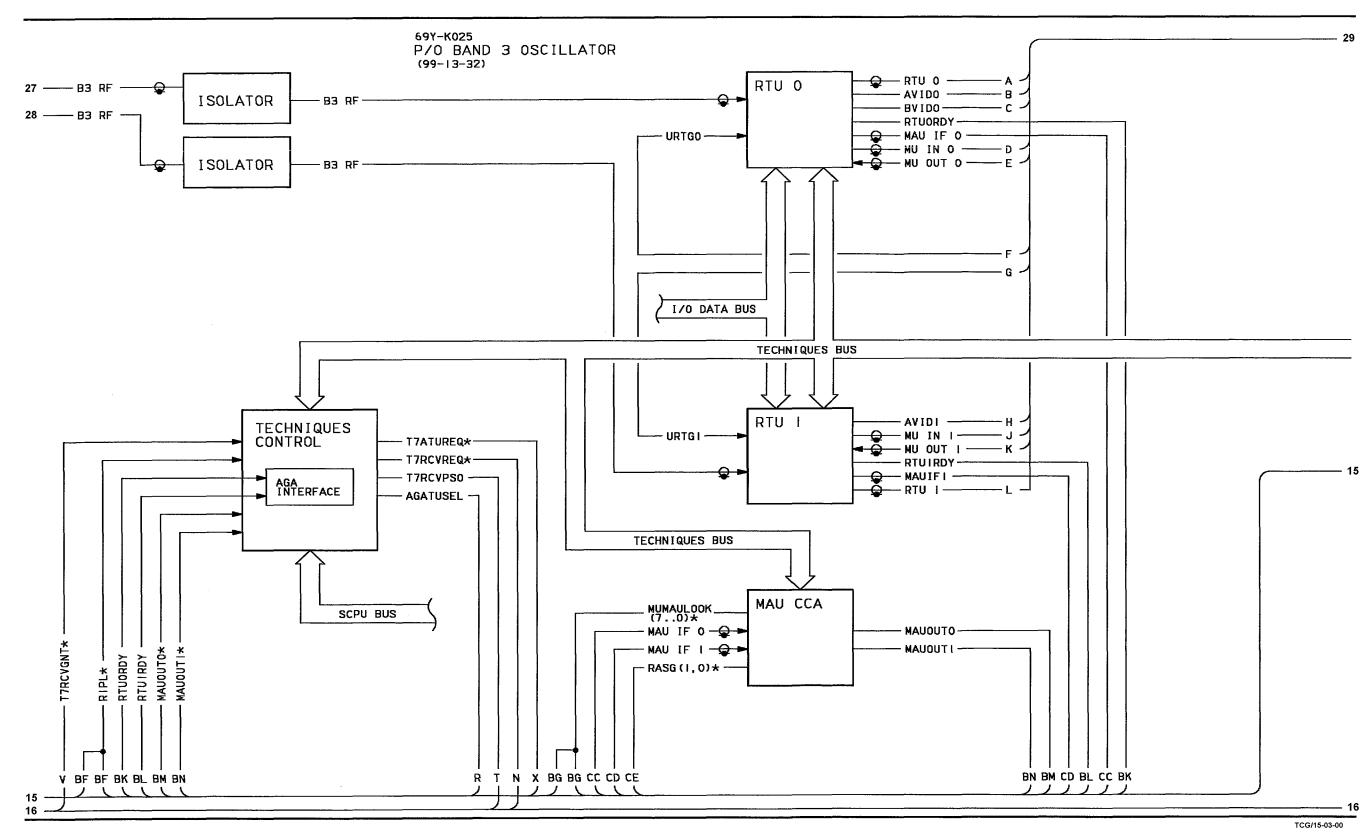

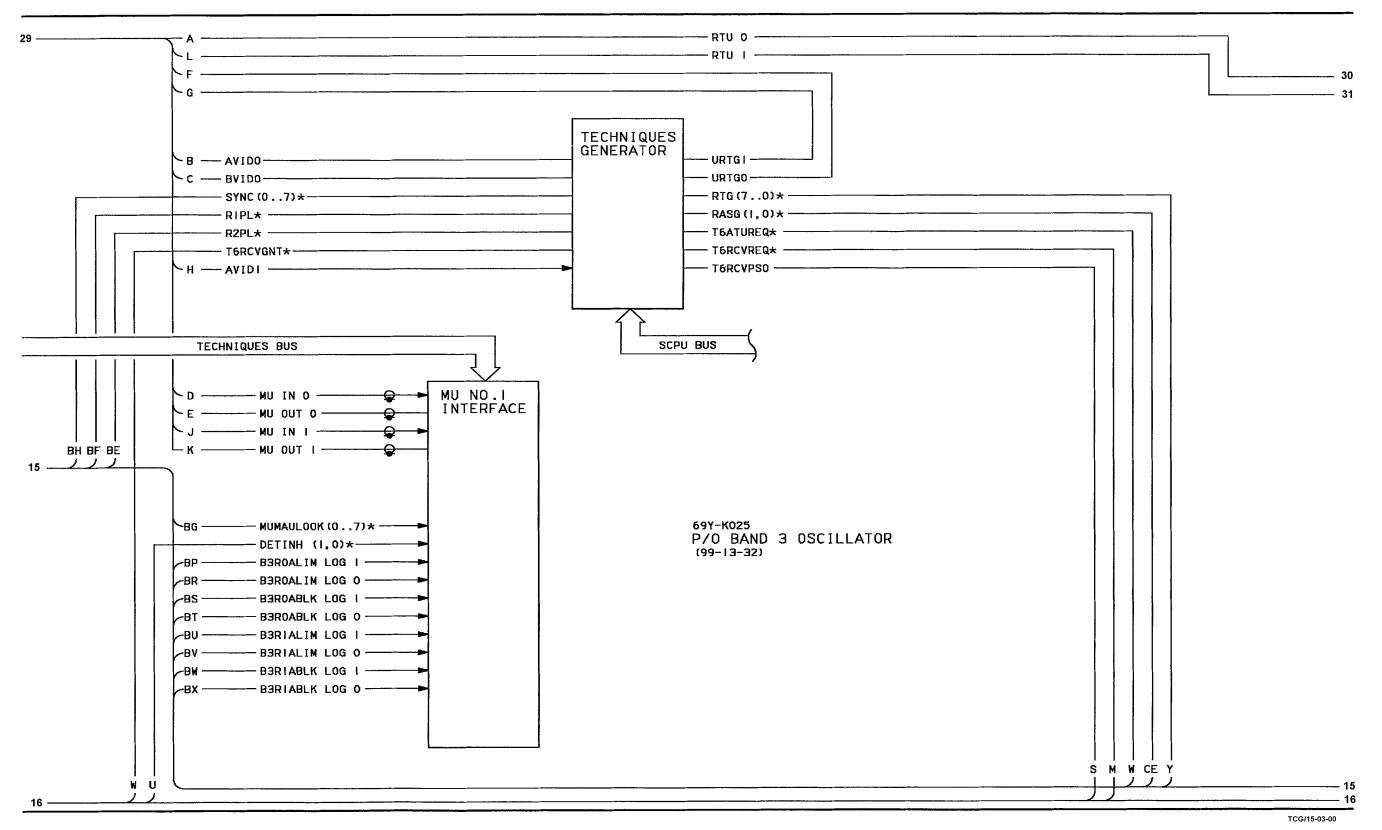

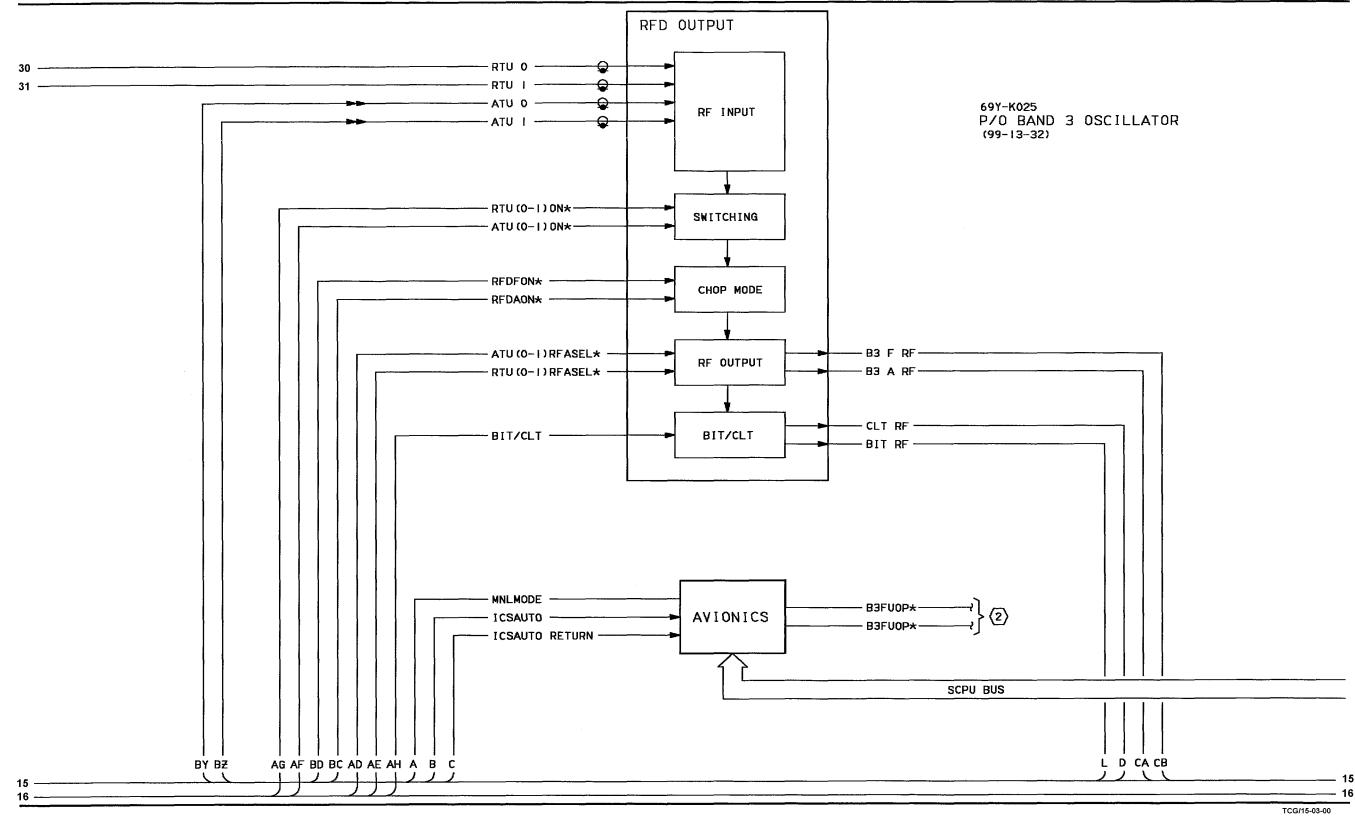

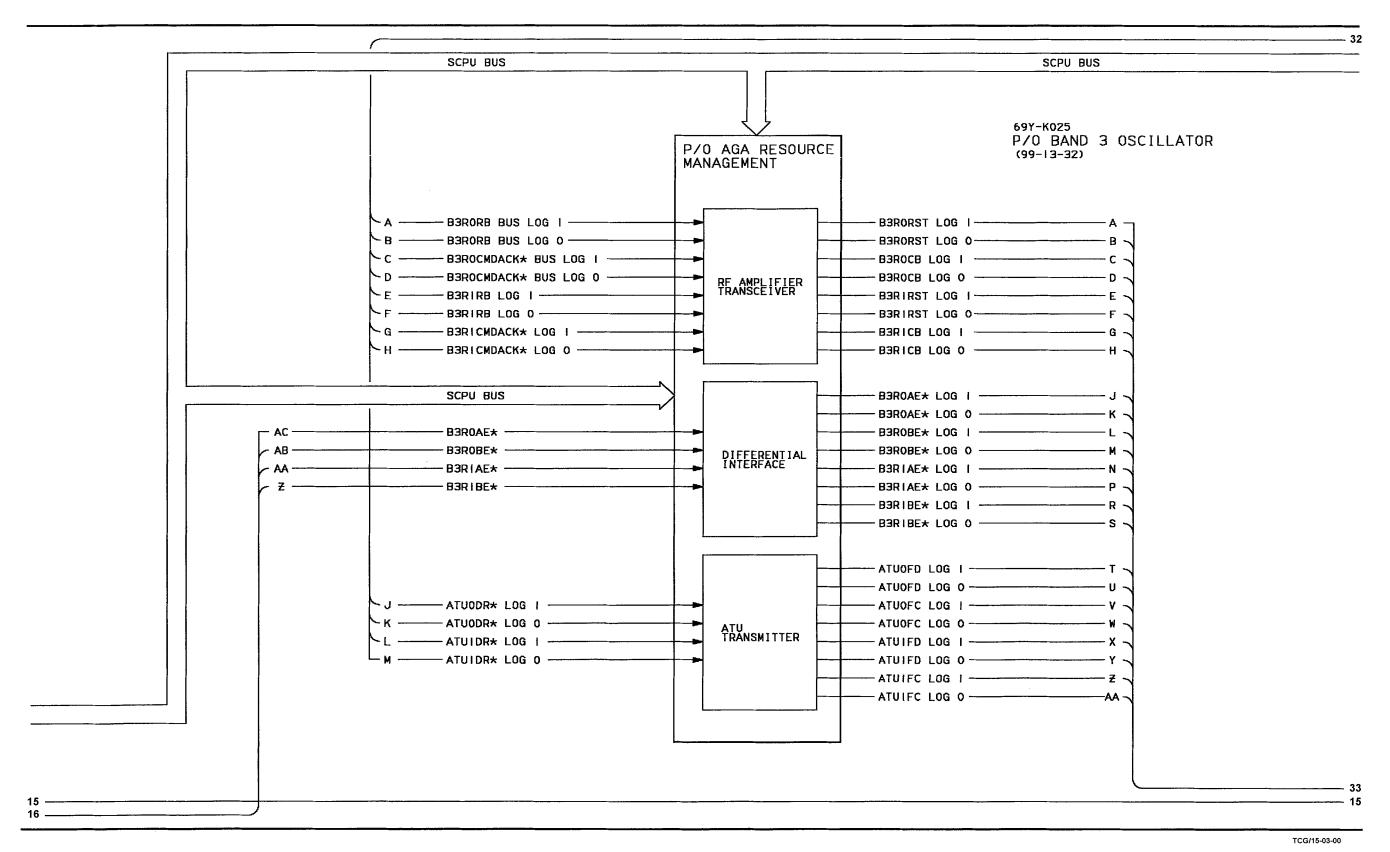

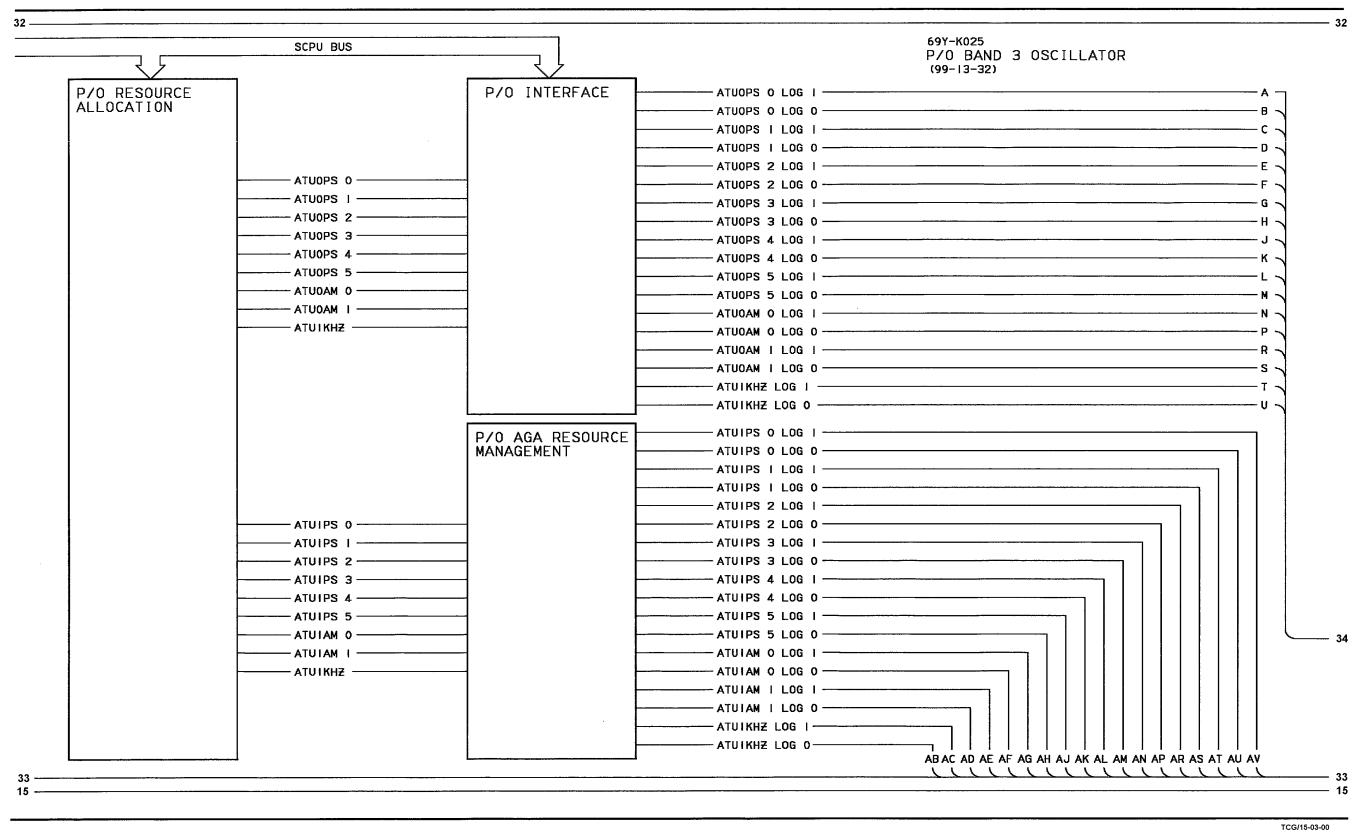

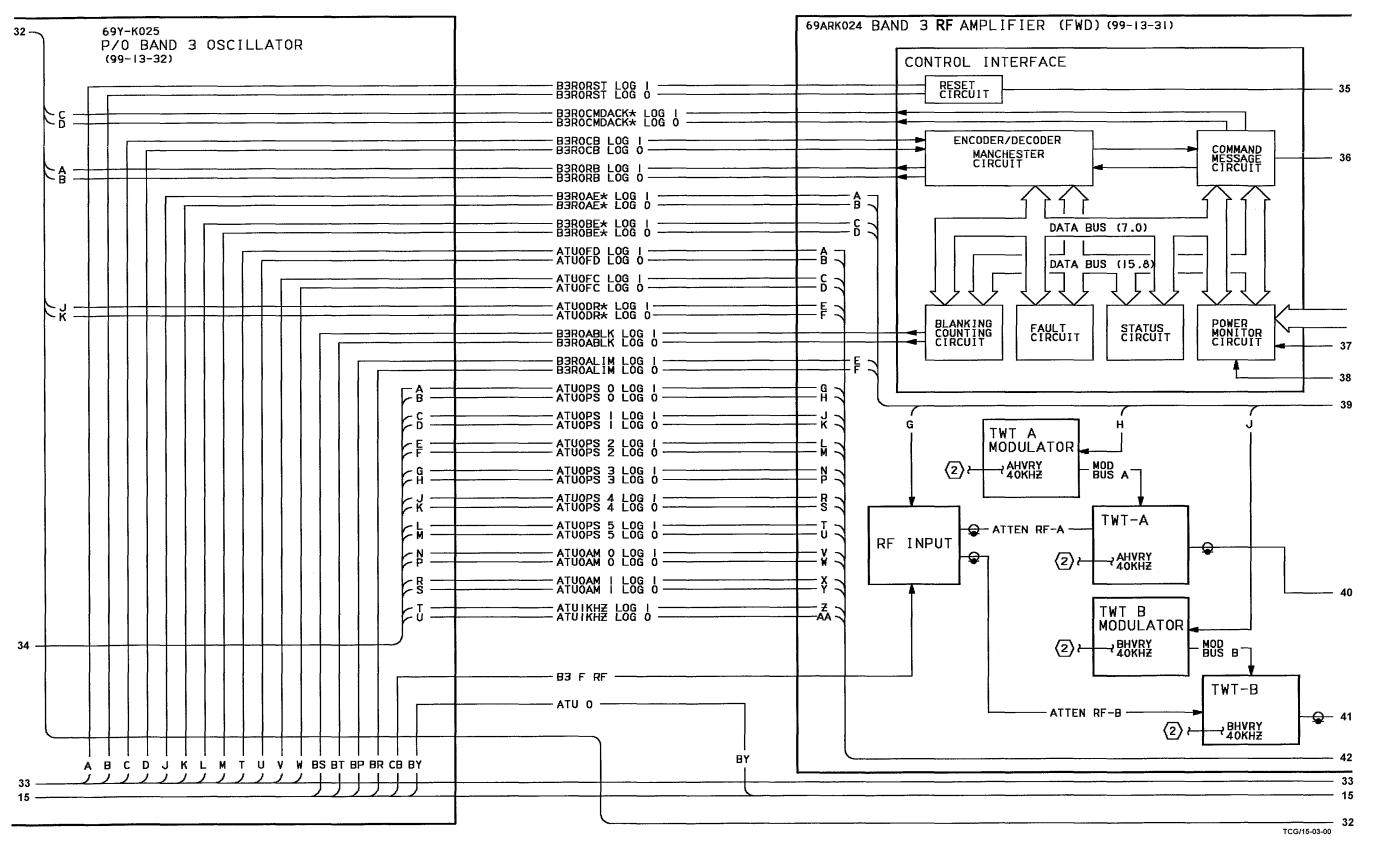

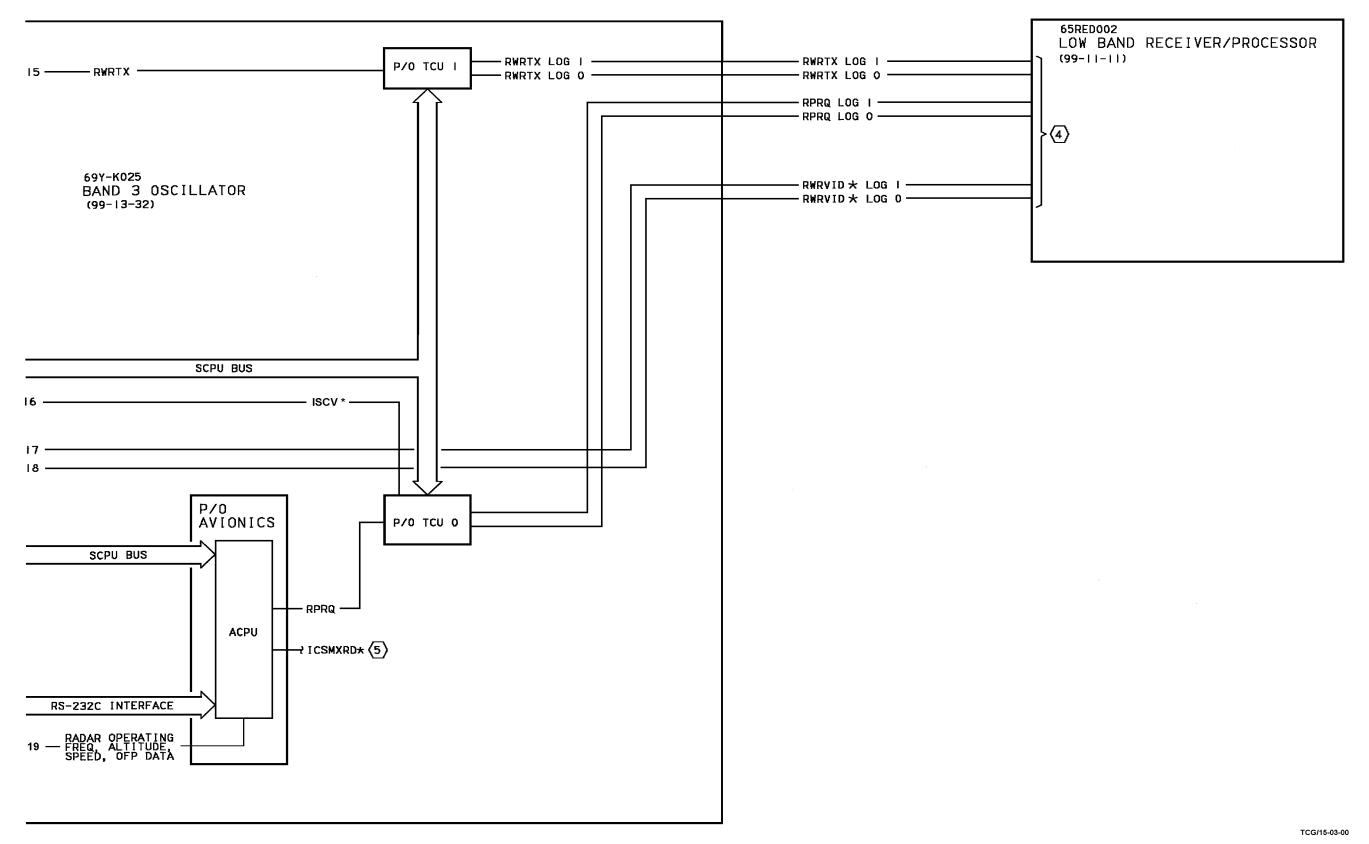

| 13-12     | ICMS Band 3 Interface Simplified Schematic                 | 13-89 |

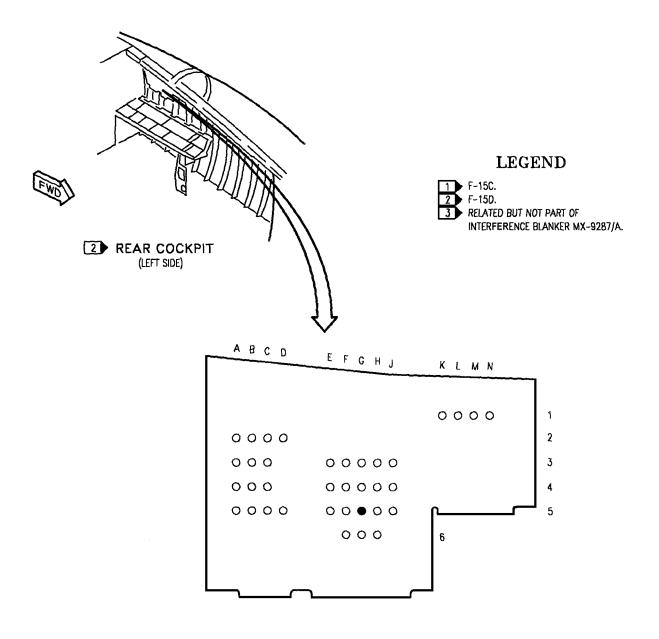

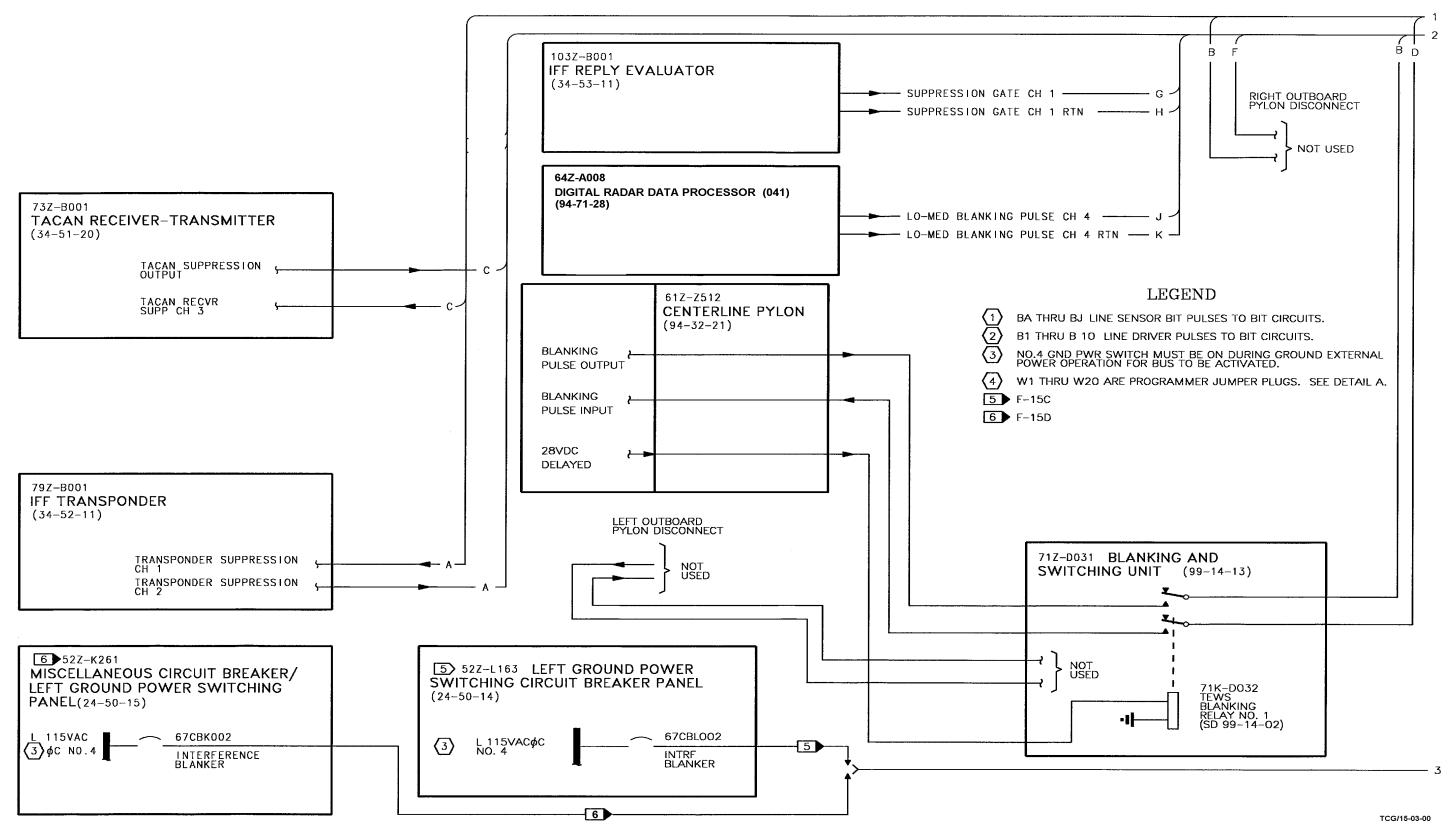

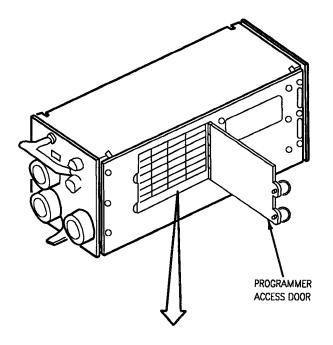

| 14-1      | Interference Blanker                                       | 14-2  |

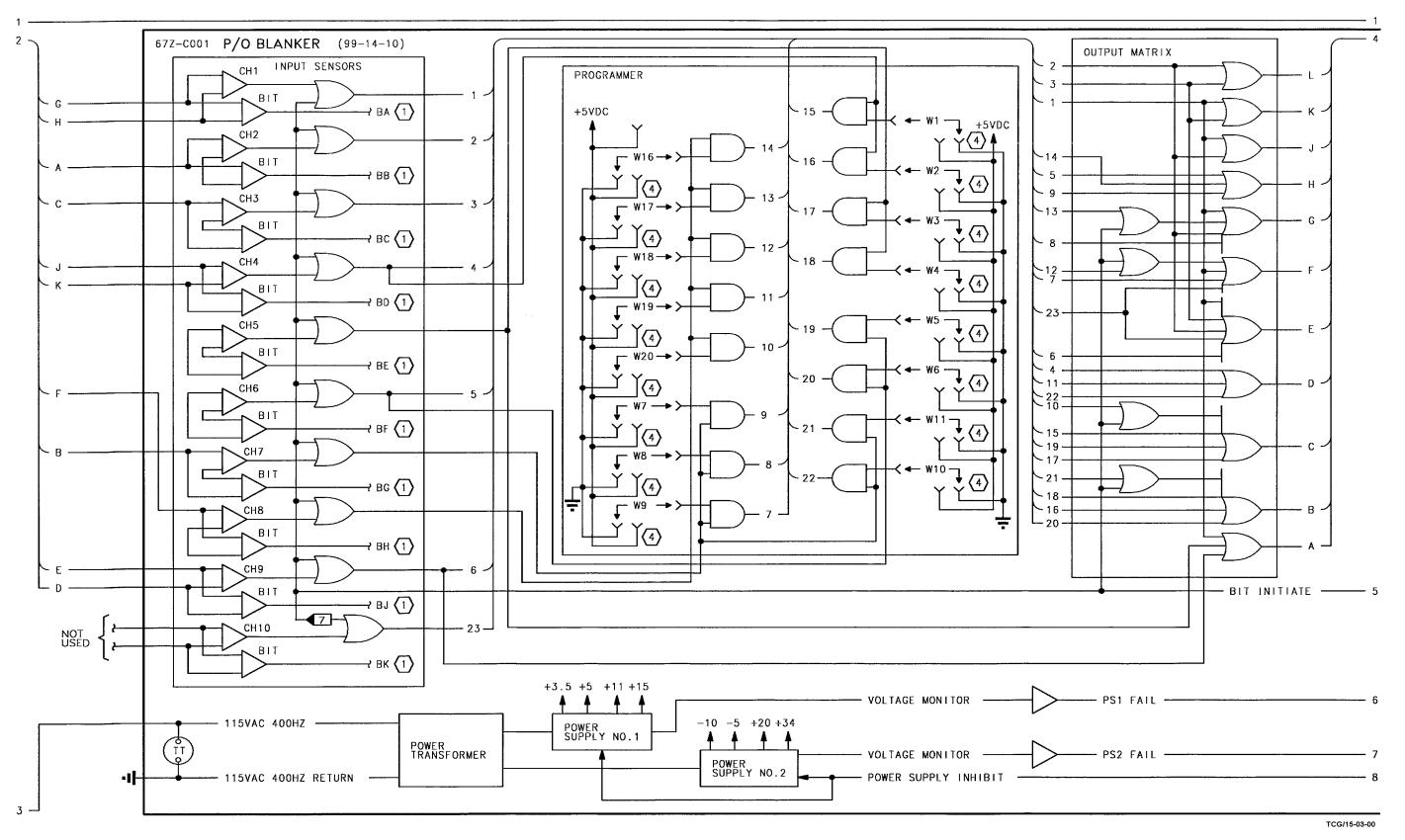

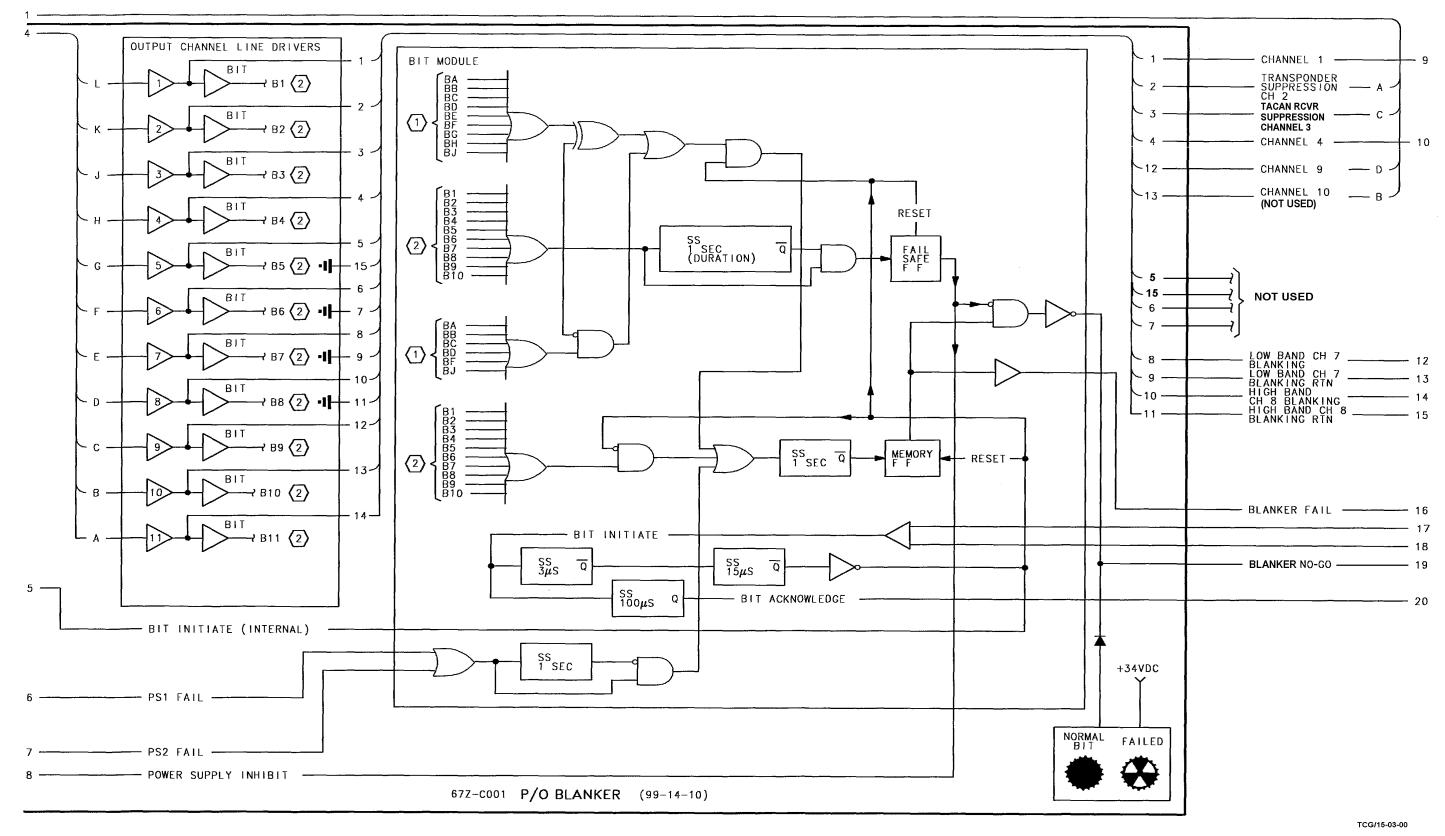

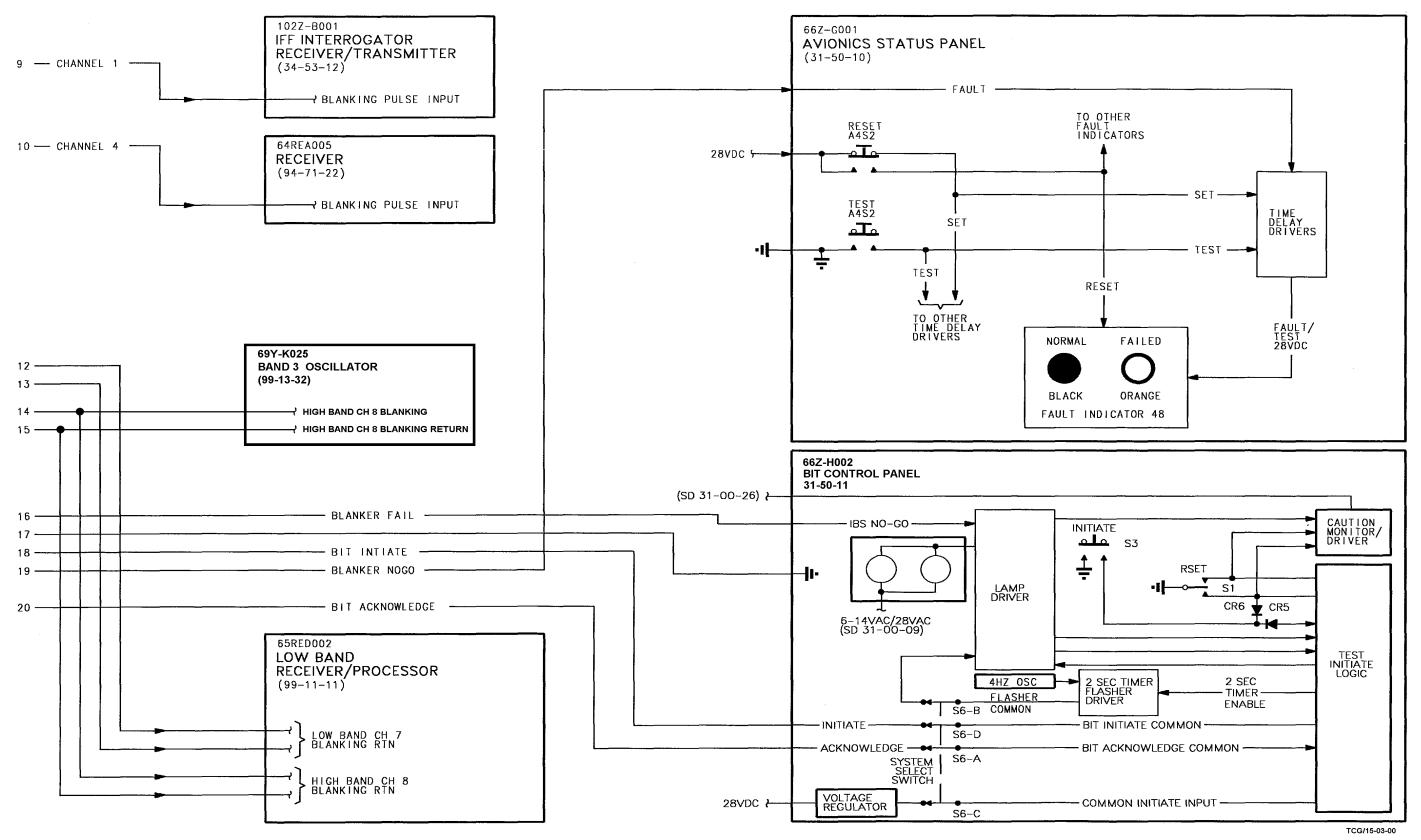

| 14-2      | Blanker Simplified Schematic                               | 14-5  |

| 15-1      | Countermeasures Dispenser Set AN/ALE-45                    | 15-3  |

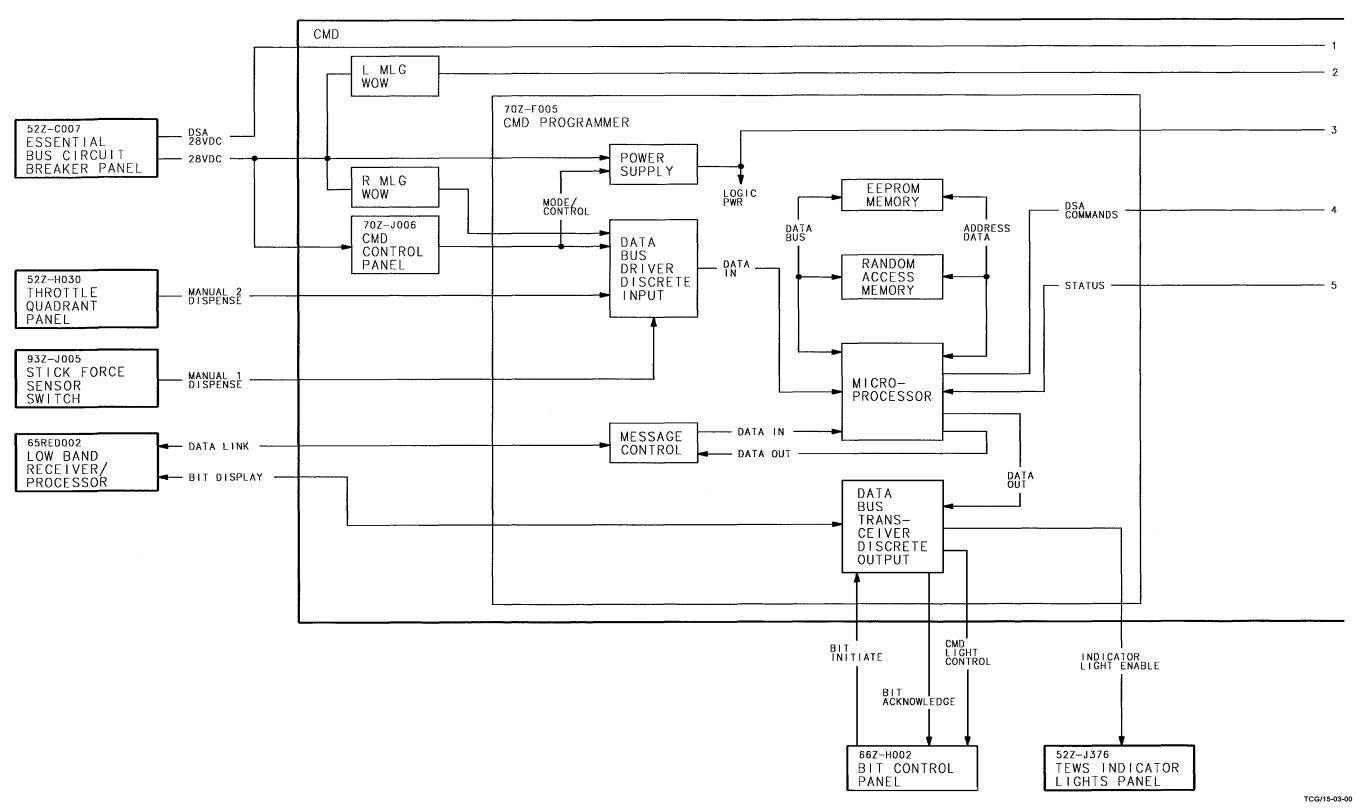

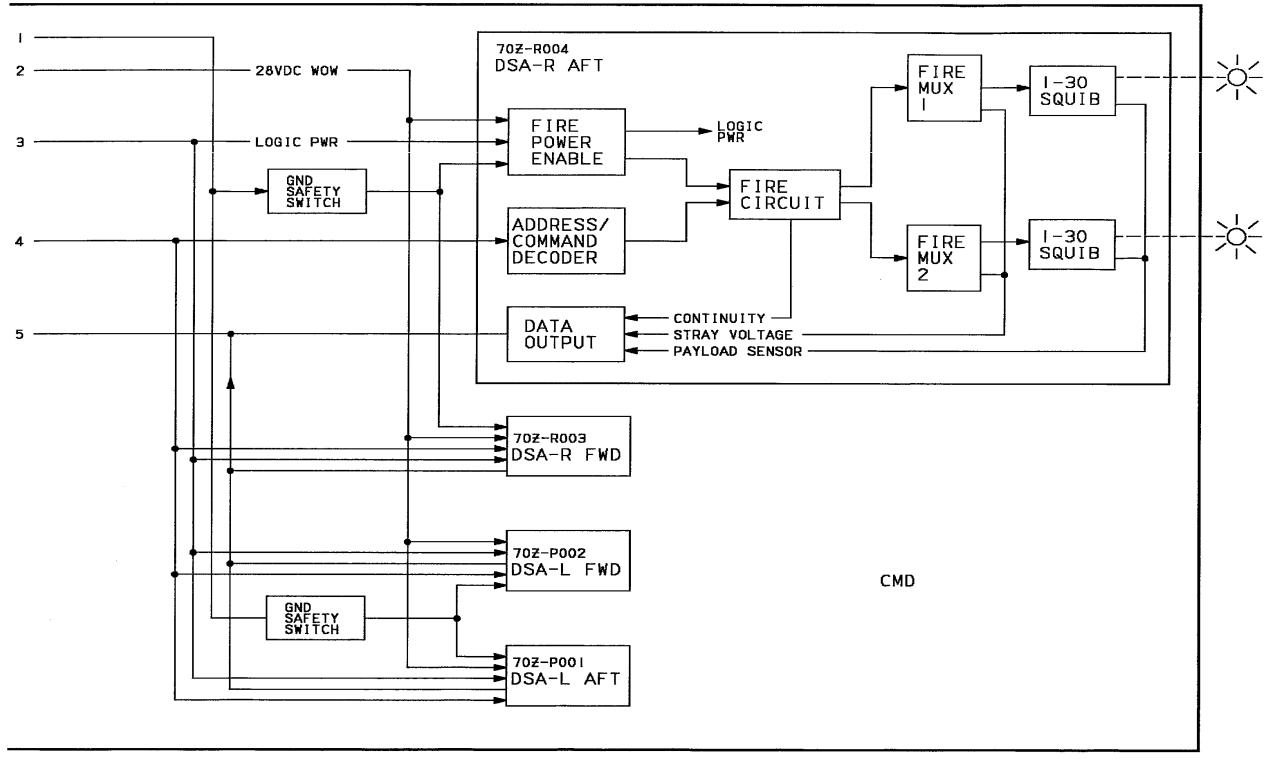

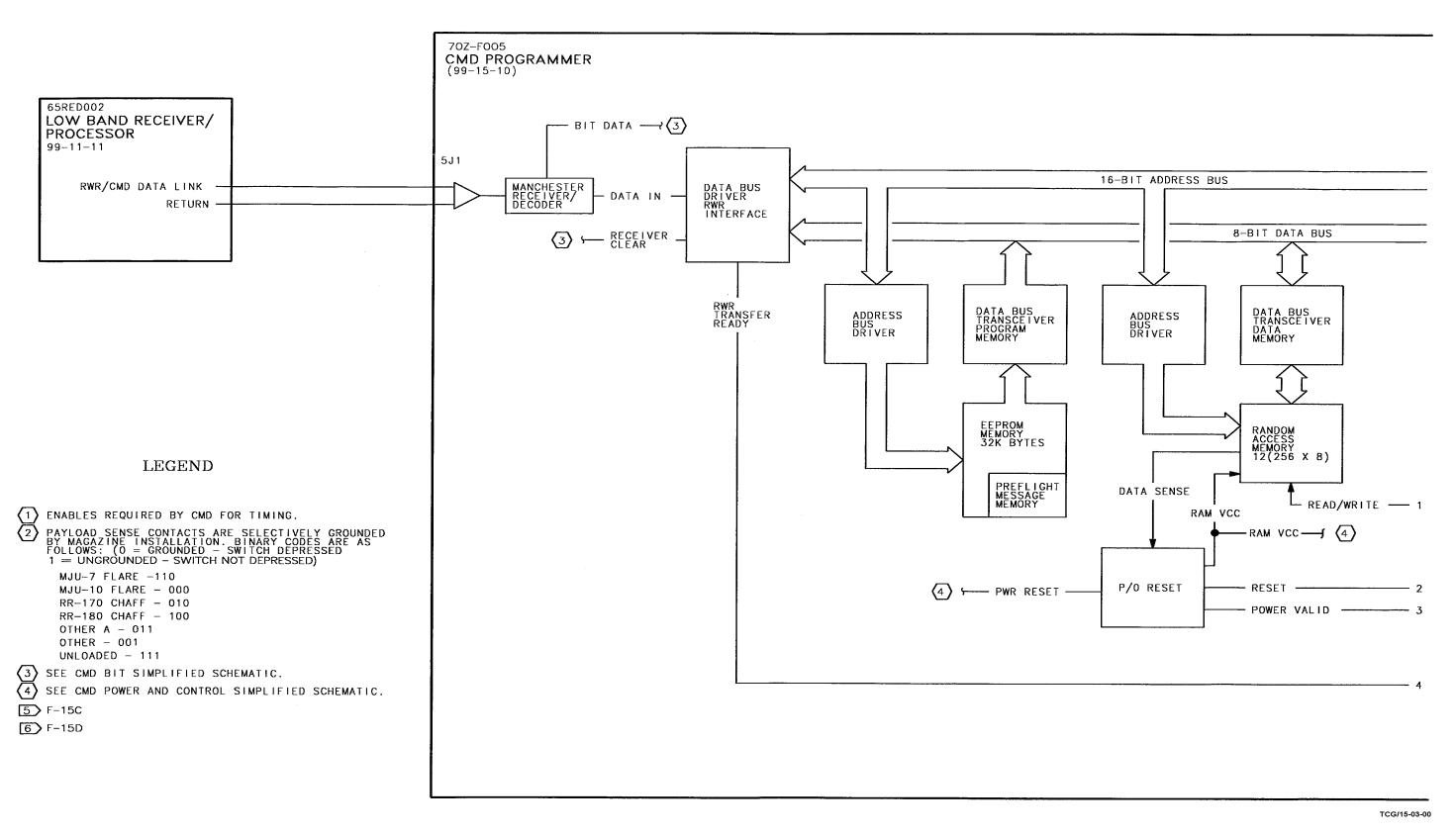

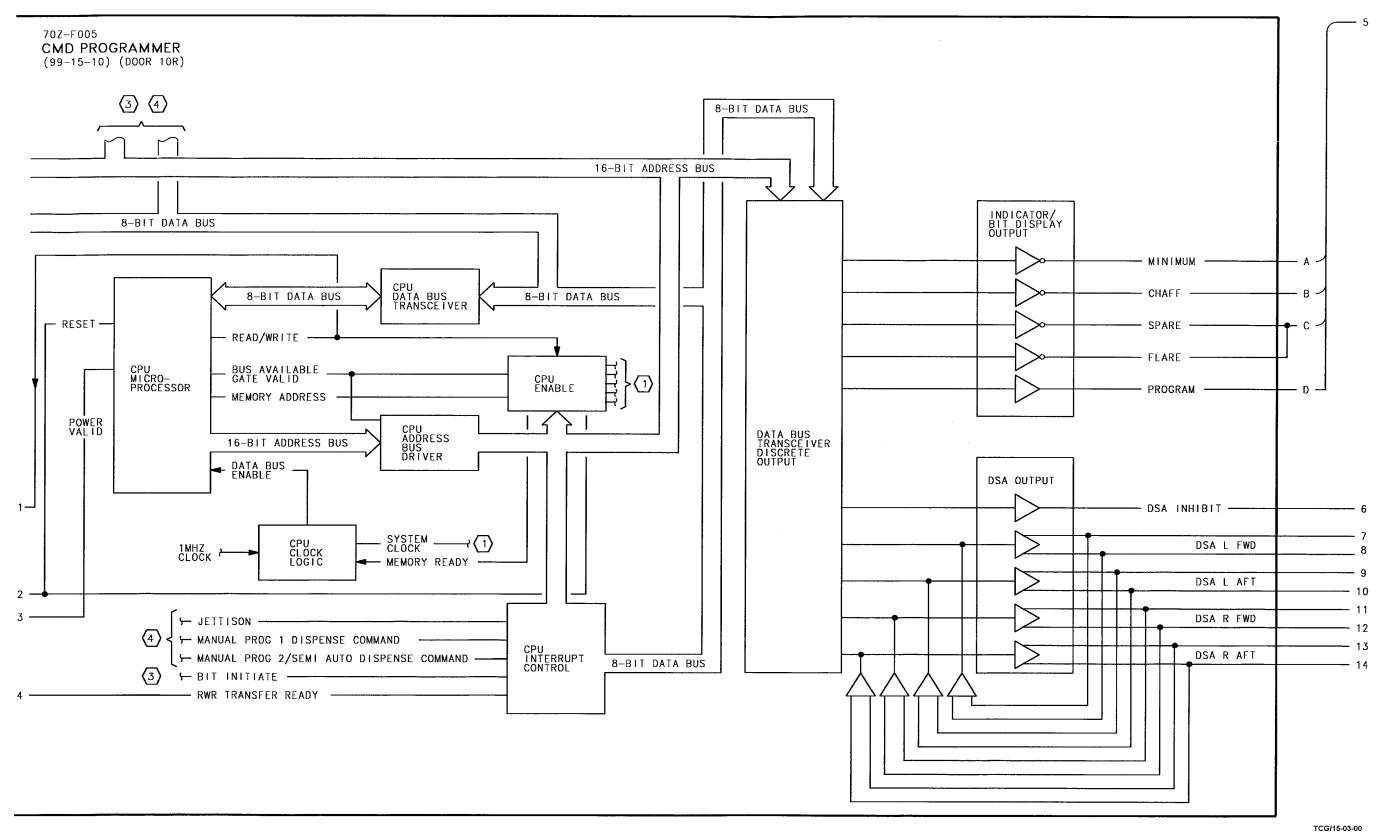

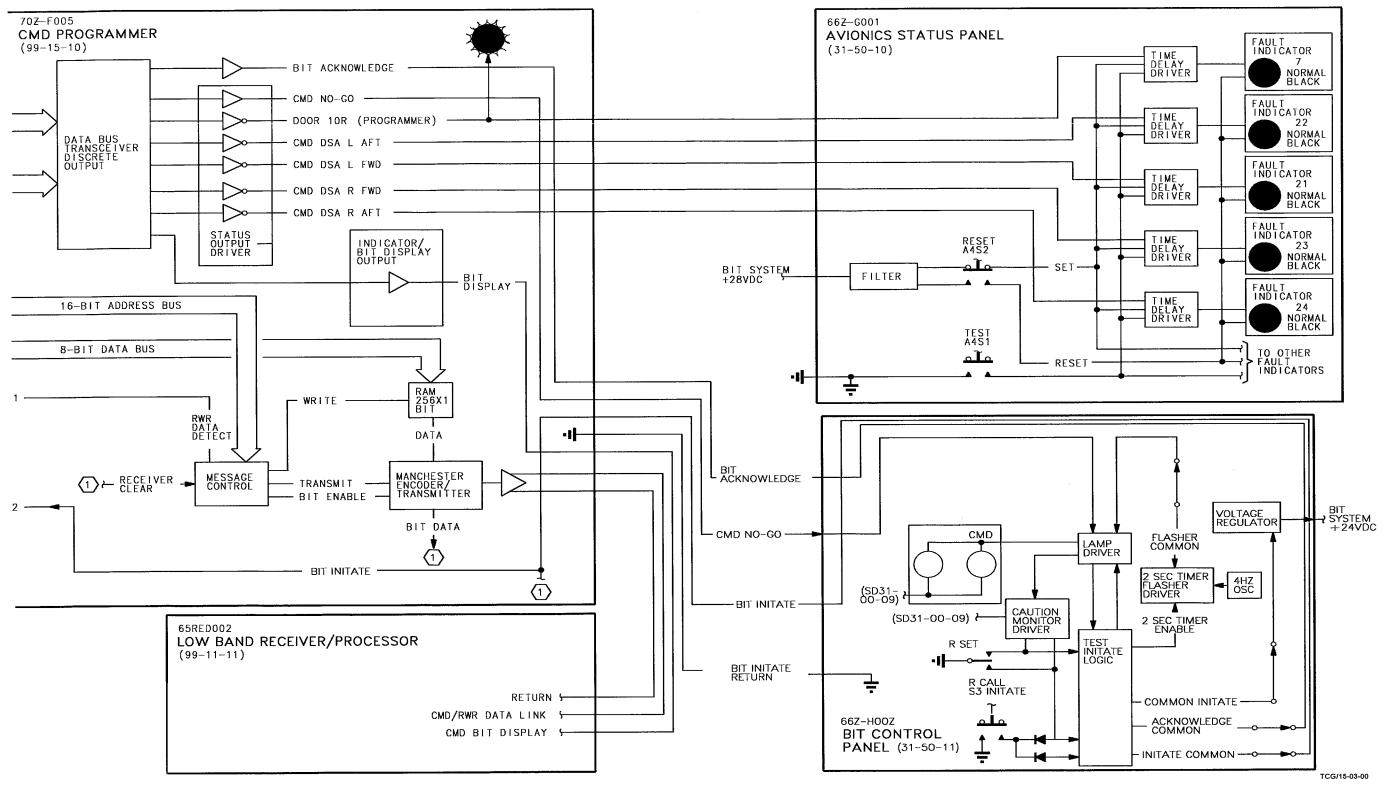

| 15-2      | CMD Functional Block Diagram                               | 15-7  |

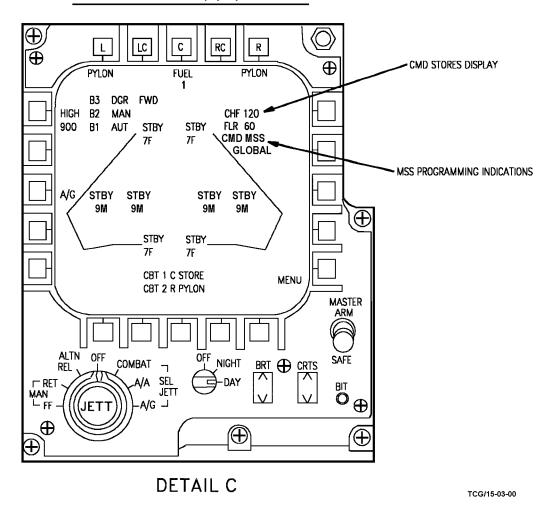

| 15-3      | Countermeasures Dispenser Set Displays                     | 15-13 |

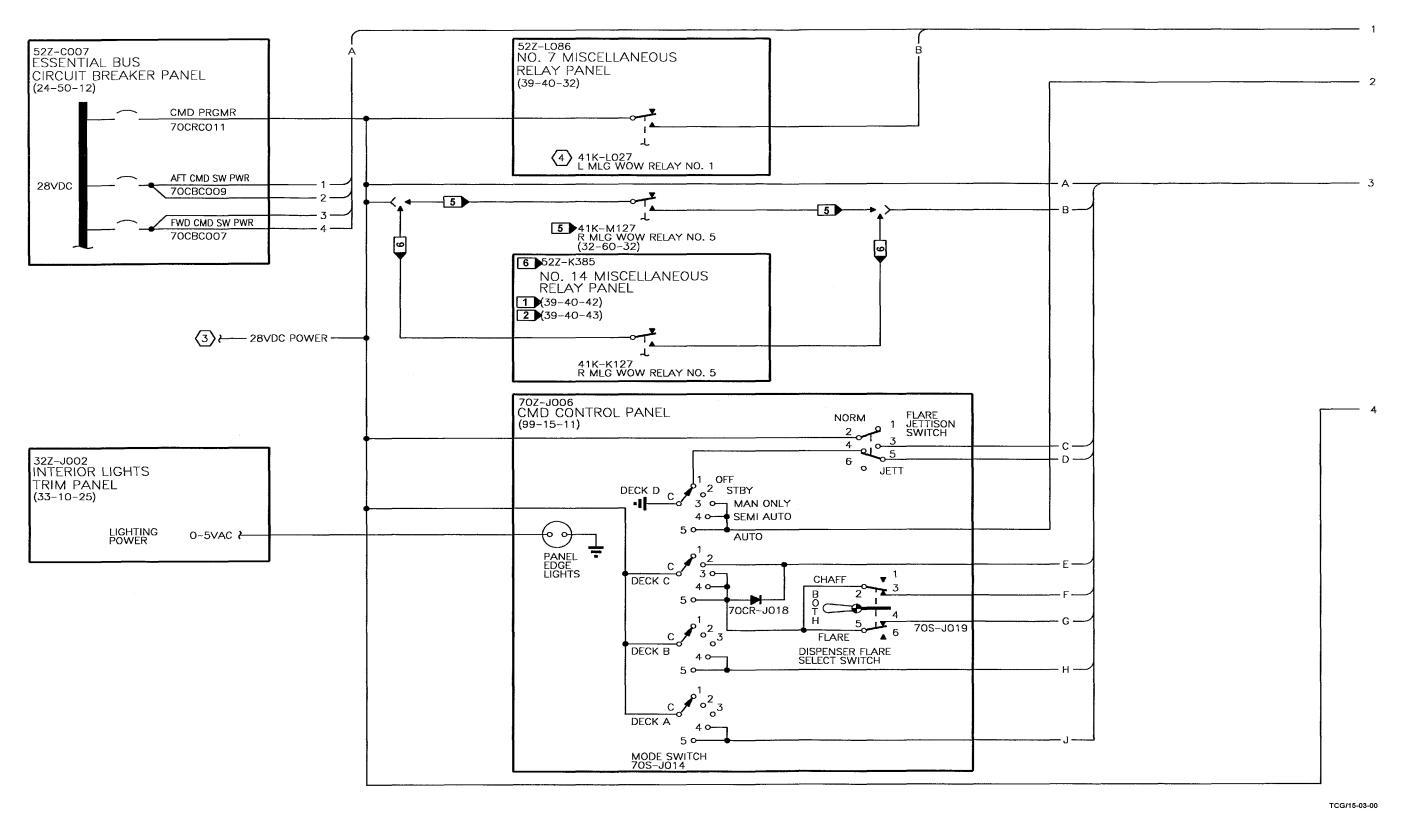

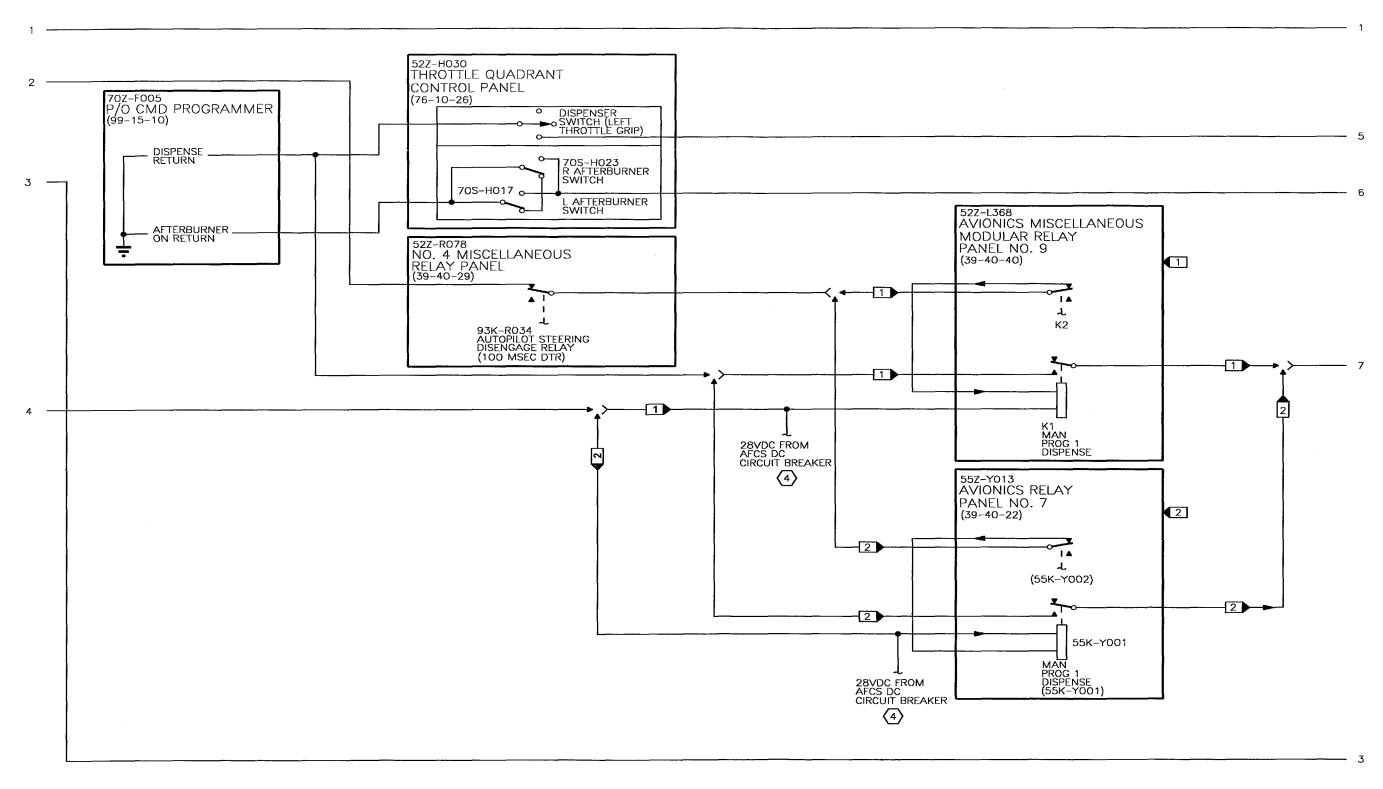

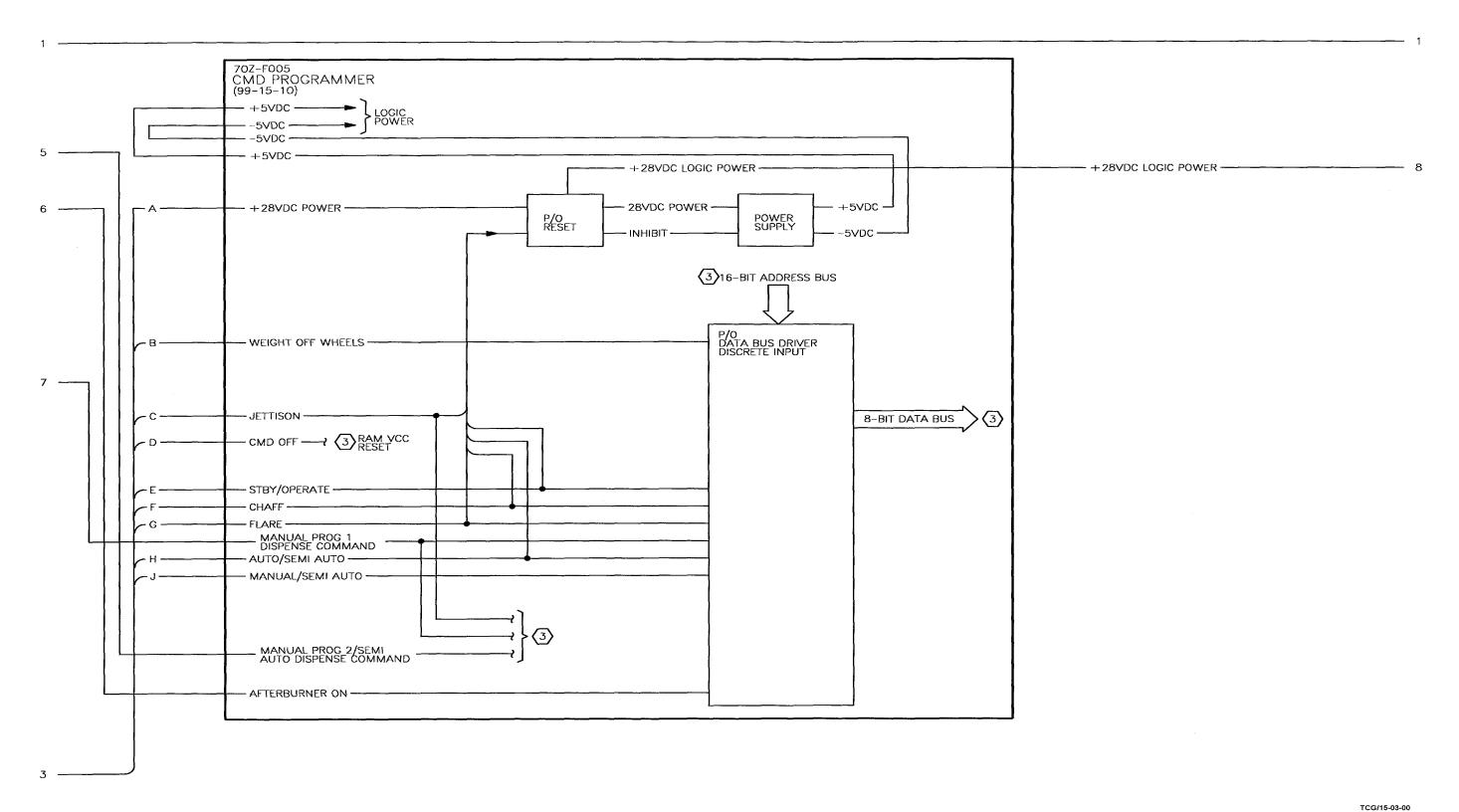

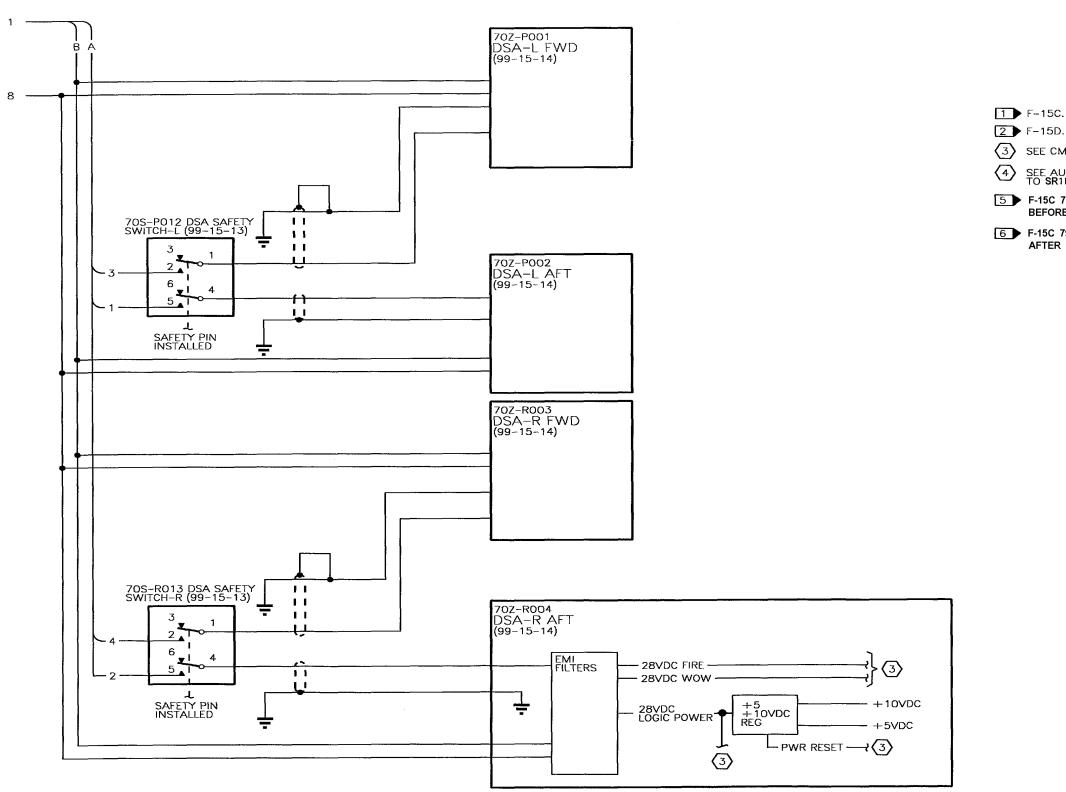

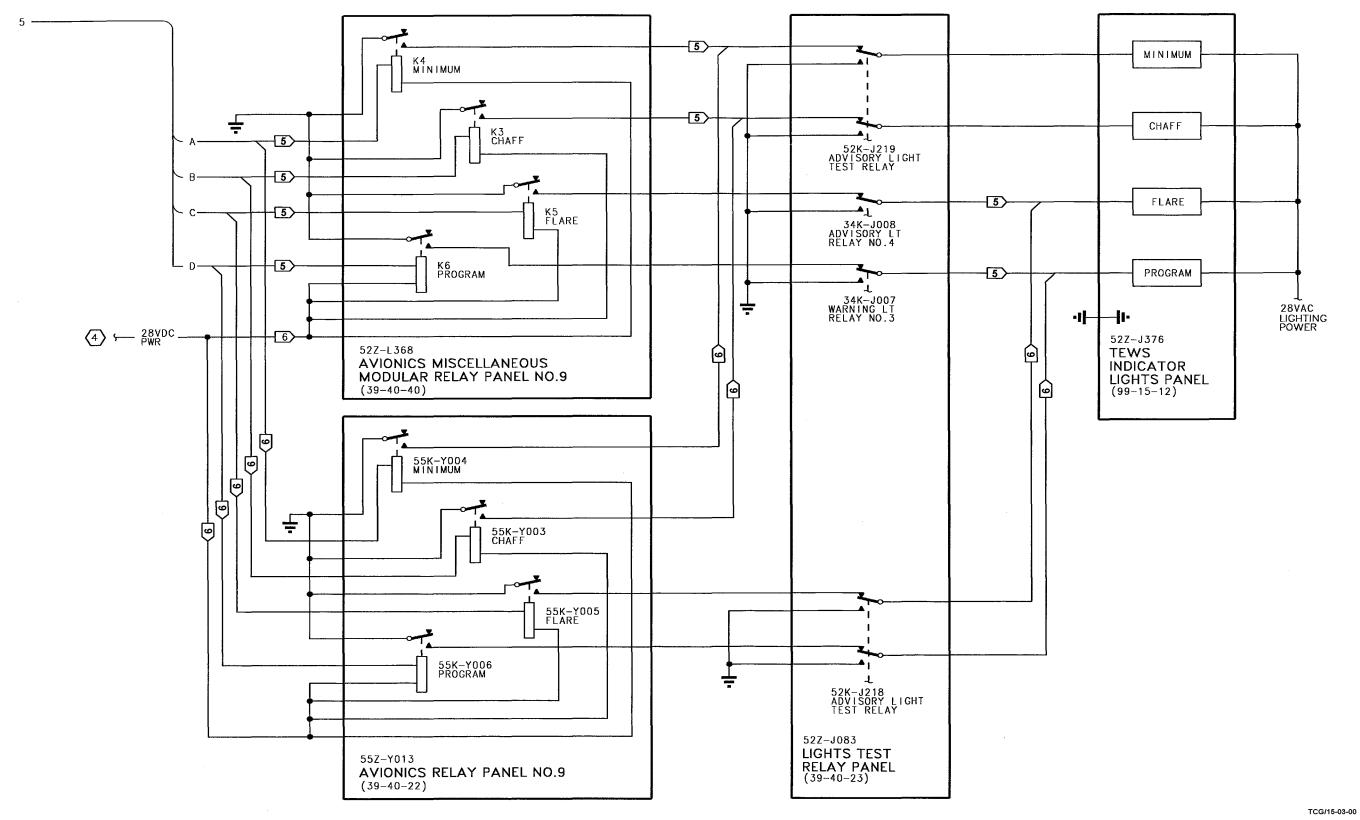

| 15-4      | CMD Power and Control Simplified Schematic                 | 15-17 |

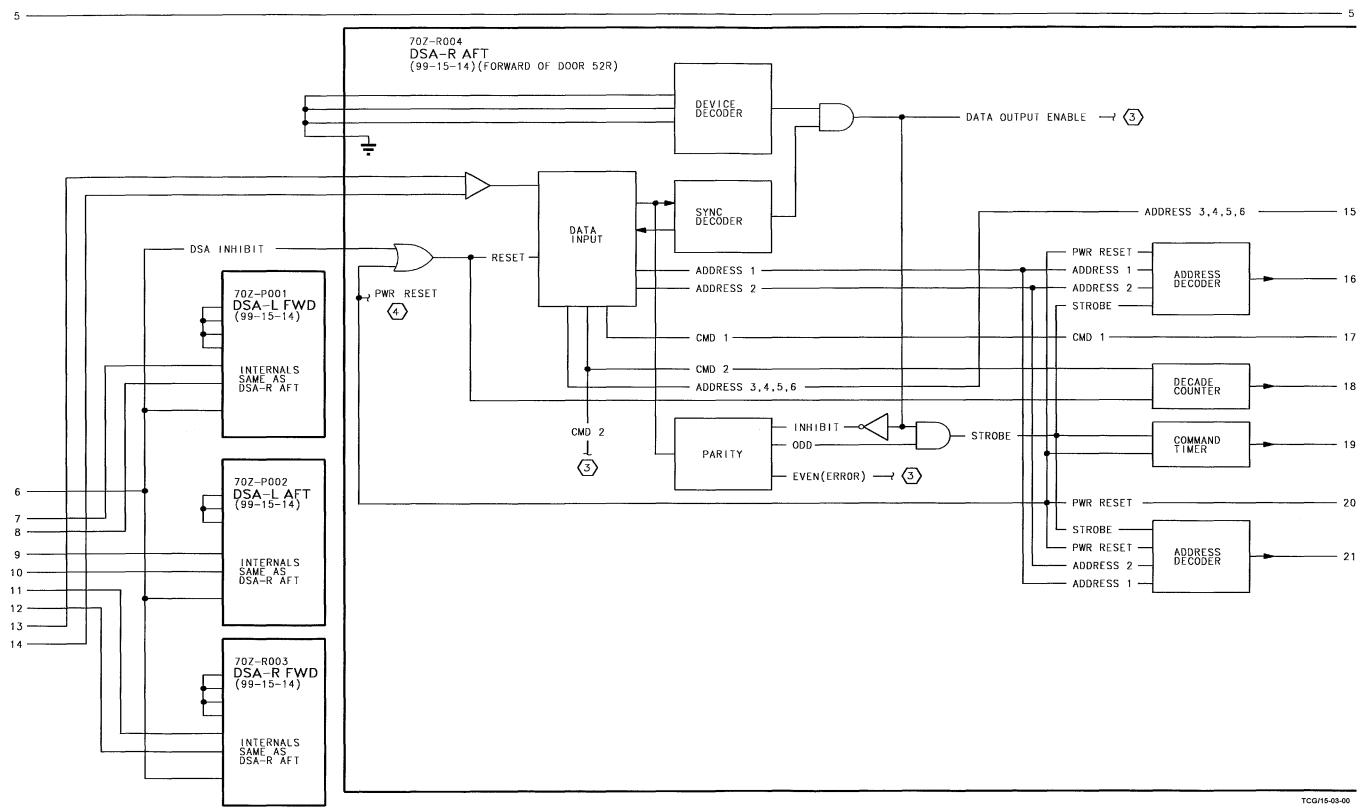

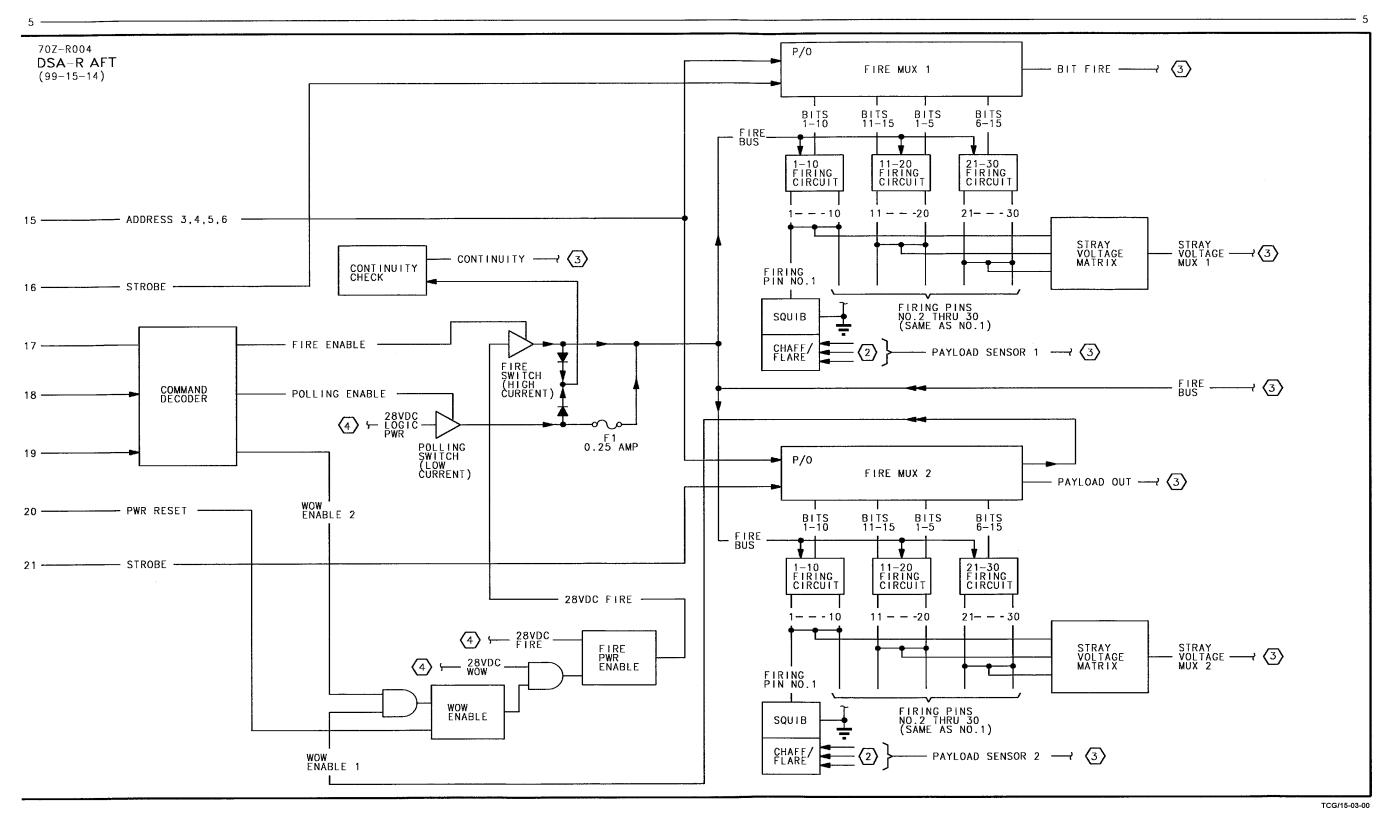

| 15-5      | CMD Logic and Firing Simplified Schematic                  | 15-23 |

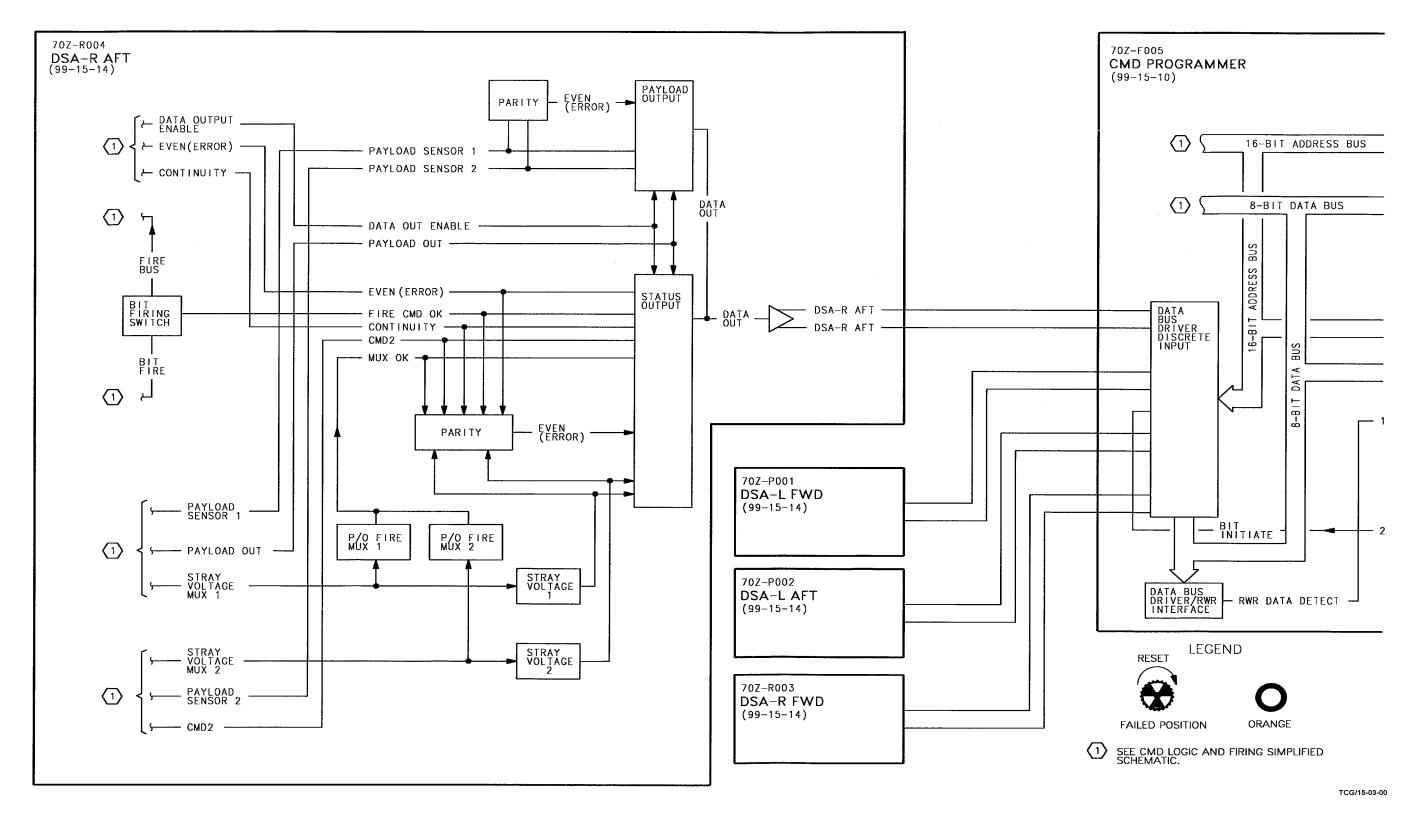

| 15-6      | CMD BIT Simplified Schematic                               | 15-28 |

|           |                                                            |       |

|           | LIST OF TABLES                                             |       |

| Table No. | Title                                                      | Page  |

| 11-1      | Line Replaceable Units                                     | 11-3  |

| 11-2      | Controls and Indicators                                    | 11-11 |

| 11-3      | RWR Functional Failure Descriptions                        | 11-77 |

| 11-4      | Supplies (Consumables)                                     | 11-80 |

| 11-5      | Test Equipment List                                        | 11-80 |

| 11-6      | Special Tools List                                         | 11-80 |

| Table No. | Title                              | Page   |

|-----------|------------------------------------|--------|

| 13-1      | Line Replaceable Units             | 13-3   |

| 13-2      | Configuration Table                | 13-5   |

| 13-3      | Controls and Indicators            | 13-19  |

| 13-4      | Band 1 and 2 Status Field Displays | 13-22  |

| 13-5      | Band 3 Status Field Displays       | 13-22  |

| 13-6      | Band 3 Limitation Field Displays   | 13-23  |

| 13-7      | BIT Operating Modes                | 13-57  |

| 13-8      | Supplies (Consumables)             | 13-107 |

| 13-9      | Test Equipment List                | 13-107 |

| 14-1      | Input/Output Distribution Matrix   | 14-12  |

| 14-2      | Supplies (Consumables)             | 14-14  |

| 14-3      | Test Equipment List                | 14-14  |

| 14-4      | Special Tools List                 | 14-14  |

| 15-1      | Line Replaceable Units             | 15-1   |

| 15-2      | Controls and Indicators            | 15-2   |

| 15-3      | Supplies (Consumables)             | 15-31  |

| 15-4      | Test Equipment List                | 15-31  |

#### INTRODUCTION

#### PURPOSE AND SCOPE.

This technical manual is one of a series providing maintenance instructions for the F-15C and F-15D aircraft. Maintenance instructions are compatible with the provisioning of spare parts, test equipment and special tools. This manual provides descriptions and principles of operation for the tactical electronics warfare system (TEWS), which is made up of the subsystems below:

Radar Warning Receiver (RWR) - AN/ALR-56C

Internal Countermeasures System (ICMS) -

AN/ALQ-135E(V)

Interference Blanker

Countermeasures Dispenser Set (CMD) - AN/ALE-45

Test equipment, consumable supplies and special tools required for servicing and maintenance are listed.

Five digit codes used throughout this publication to identify equipment manufacturer may be designated as Mfg. Code, FSCM or CAGE.

#### SIGNIFICANT CHANGES.

The significant changes in this revision are the removal of the PREMSIP data and drawings and incorporation of F-15C/D Suite 2 data.

#### APPLICABILITY NOTATIONS.

Information and instructions contained in this manual unique to one model are identified as F-15C or F-15D. Data applicable to specific aircraft within a series are identified by RSAF serial number.

#### IMPROVEMENT REPORTS.

Recommendations for improvements to this technical order shall be submitted on AFTO Form 22, Technical Order System Publication Improvement Report, in accordance with TO 00-5-19. Completed forms shall be forwarded to WR-ALC/LFI, 296 COCHRAN STREET, ROBINS AFB, GA 31098-1622.

### RECORD OF APPLICABLE TIME COMPLIANCE TECHNICAL ORDERS.

The record of applicable time compliance technical orders is a list of all TCTO's which affect the technical content (text or illustration) of this manual. Only current TCTO's are listed. A TCTO is deleted from the list when any of the below occurs:

- a. The equipment configuration to which the TCTO is applicable is no longer covered in the manual.

- b. The TCTO is rescinded.

- c. The TCTO is superseded or replaced.

#### **Record of Applicable Time Compliance Technical Orders**

| TCTO No.     | Title                                                            | TCTO Date        |

|--------------|------------------------------------------------------------------|------------------|

| SR1F-15-1019 | Increased High Pressure Water Separator (ECP MDA-F-15-1617R1-OW) | 30 November 1992 |

#### **SECTION 00**

#### TACTICAL ELECTRONIC WARFARE SYSTEM (TEWS)

### 00-1. SYSTEM FUNCTIONAL DESCRIPTION.

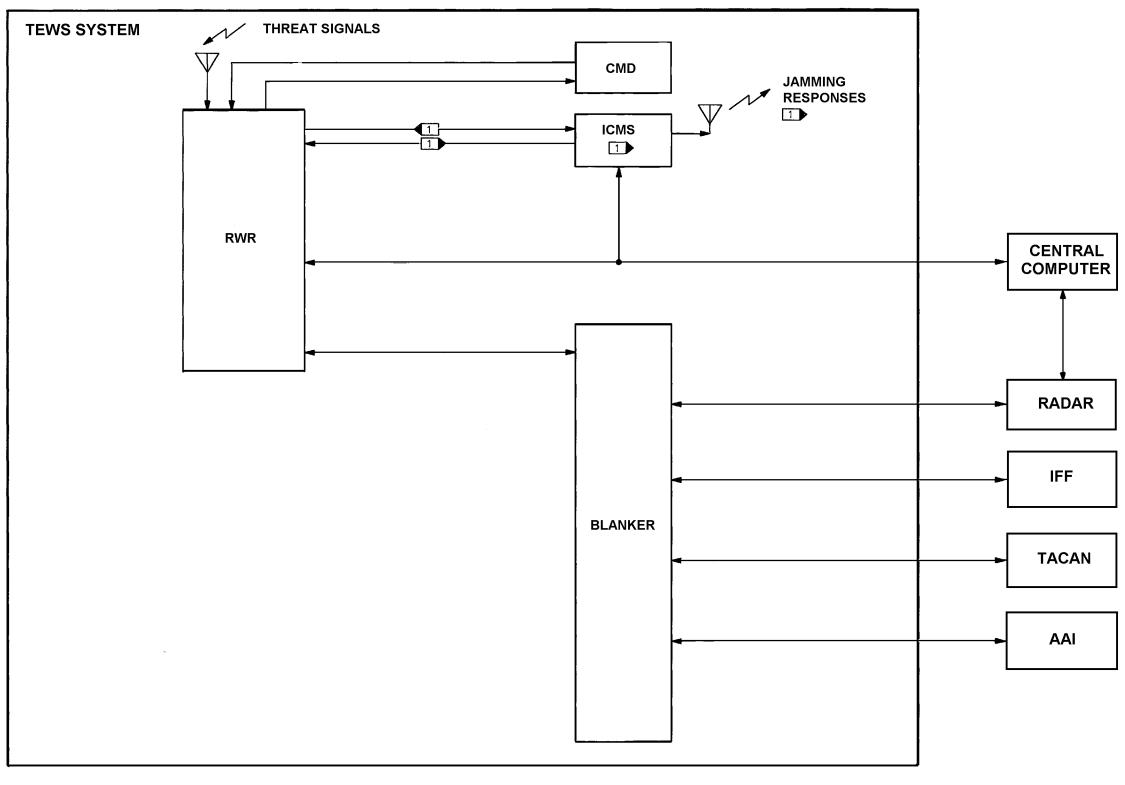

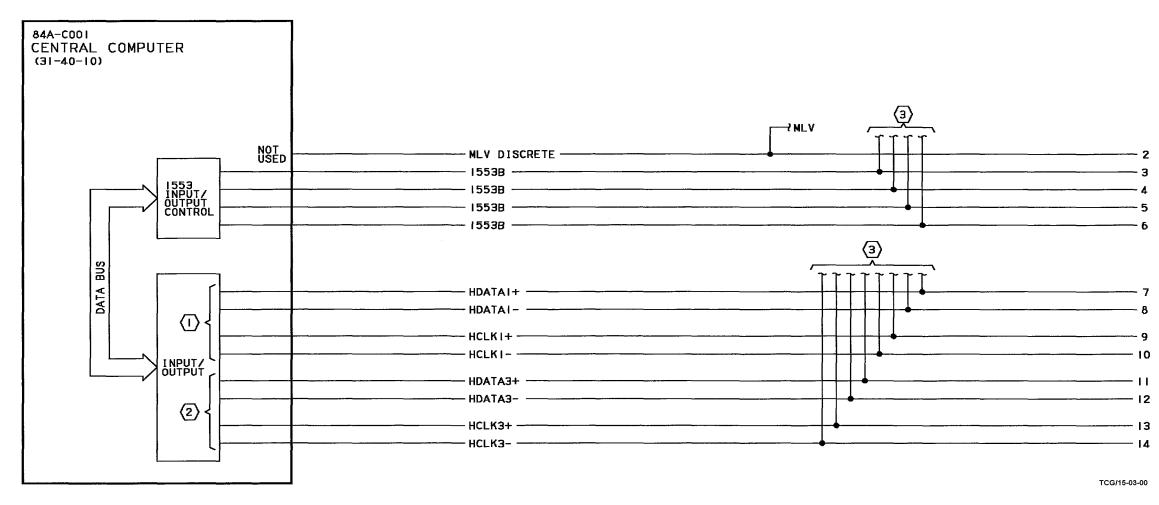

- 00-2. **DESCRIPTION.** Refer to figure 00-1.

- 00-3. This section describes the overall aspects of the F-15 aircraft Tactical Electronic Warfare System (TEWS).

- 00-4. The primary function of the TEWS system is to provide defensive and offensive electronic warfare ability for the F-15 aircraft under various tactical environments. The TEWS system is several related subsystems integrated into one system, with automatic or pilot-initiated reaction to any threat situation.

- 00-5. Radar Warning Receiver (RWR). The RWR subsystem receives, analyzes and stores threat data transmitted by surface-to-air missiles (SAM), air intercept (AI), anti-aircraft artillery (AAA) control and communication systems. The stored data is provided to the pilot as warning lamp and CRT displays to enable determination of the threat situation.

- 00-6. The RWR also provides automatic control and tuning data for the Internal Countermeasures Set (ICMS) and Countermeasures Dispenser Set (CMD).

#### 00-7. Internal Countermeasures Set (ICMS)

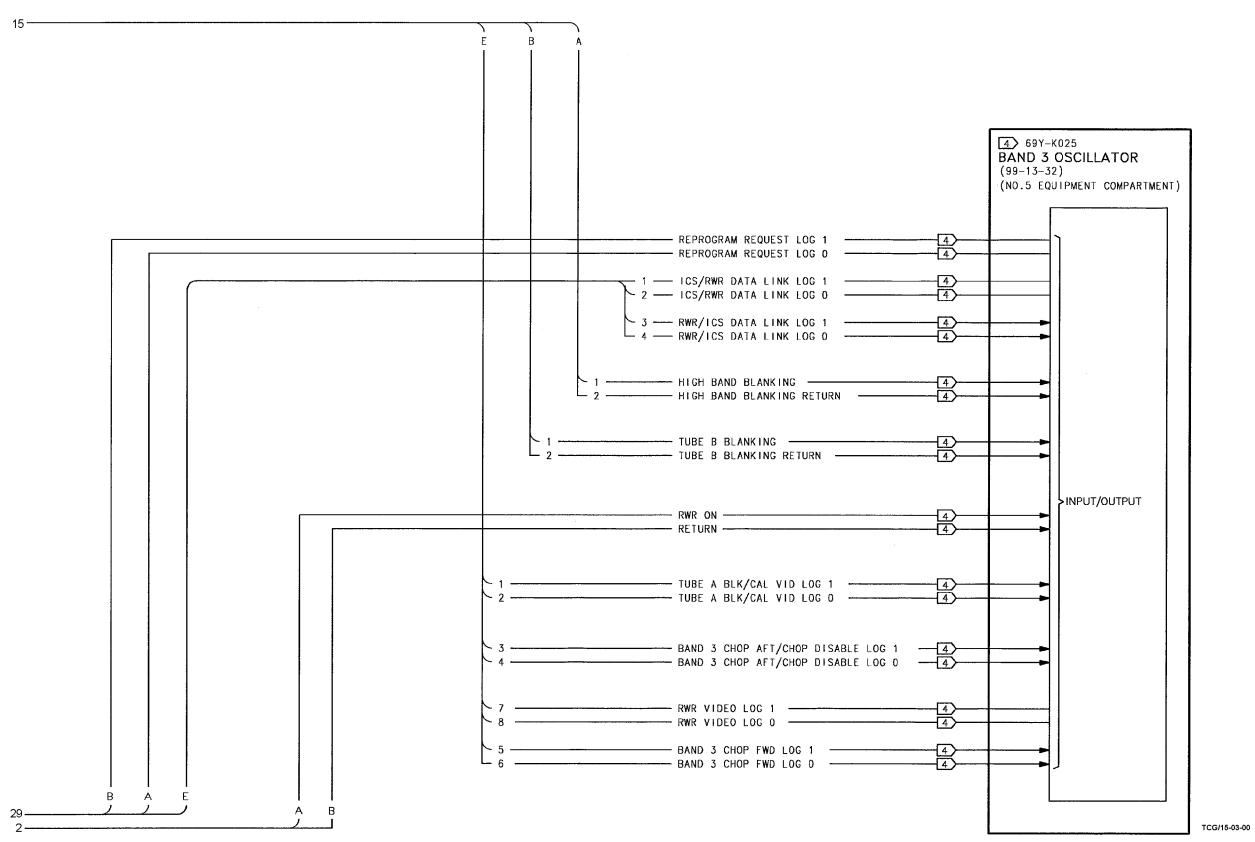

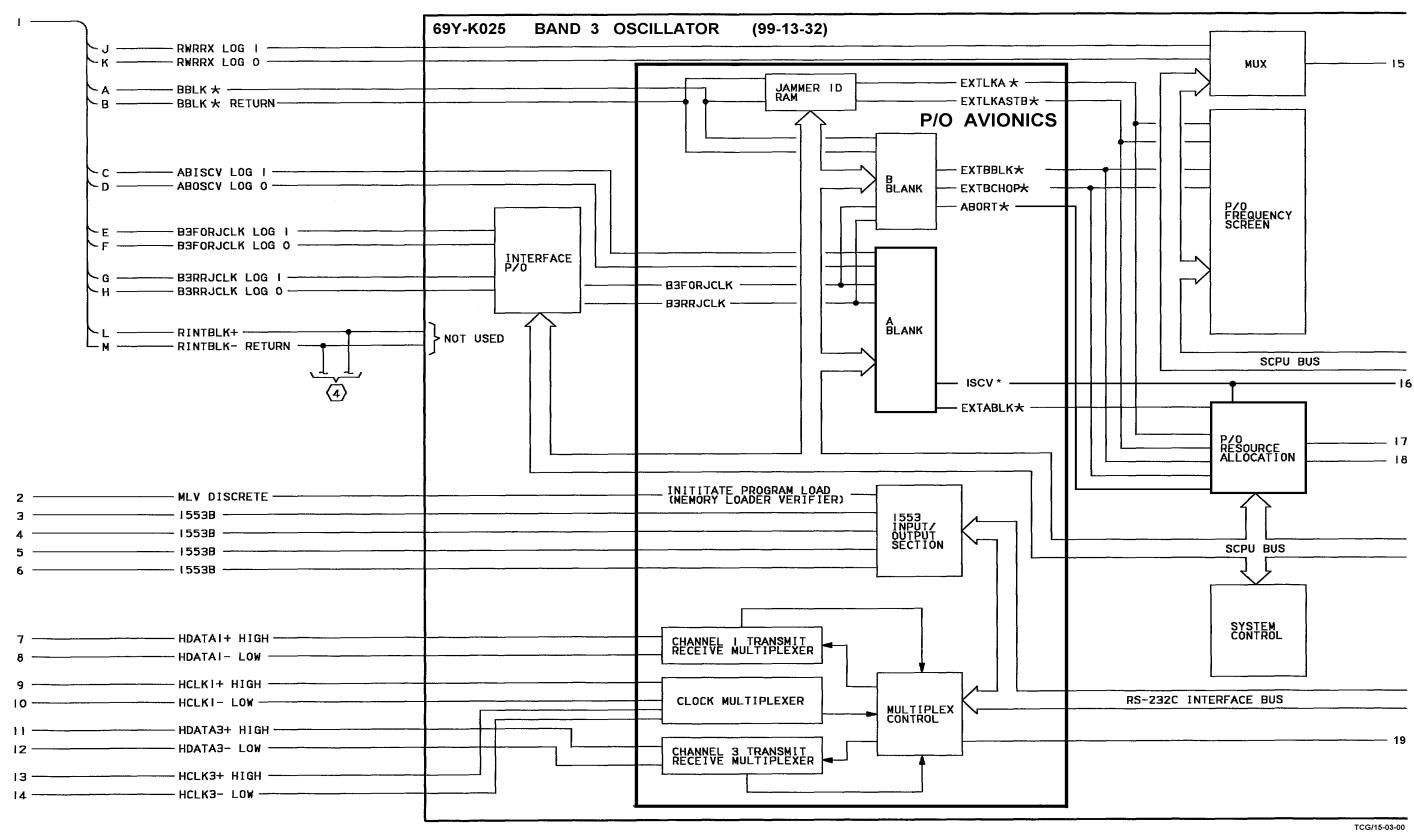

(F-15C). The ICMS contains three separate sets (band 1, 2 and 3) that provide jamming ability against threat signals. Band 1 and 2 jamming parameters are derived either by automatic program control under the direction of the RWR, or by fixed, repeating parameter control by a self-contained program. Band 3 operates in two modes auto (normal) and manual (emergency). During band 3 set operation in the auto mode, the RWR provides threat information for comparison with threat information obtained by the band 3 set. During manual operation, the RWR RF environment threat information is used.

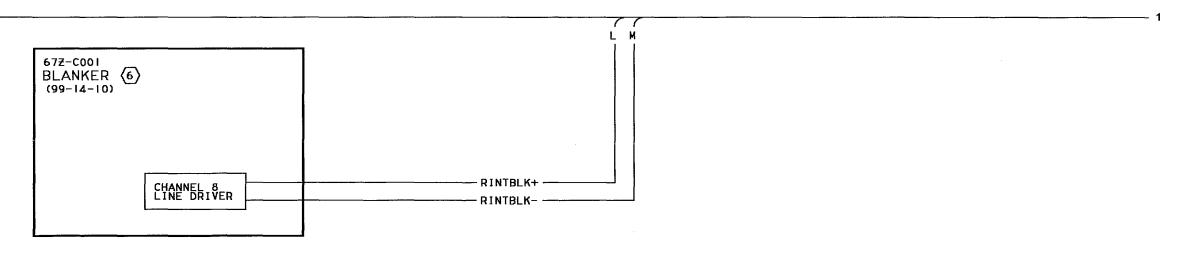

- 00-8. **Interference Blanker (Blanker).** The blanker is a maintenance-programmable device that suppresses the responses of the RWR and other on-board receiving equipment to electronic interference from on-board transmitting equipment.

- 00-9. Tactical Electronic Warfare Pod (TEWS

- **Pod).** The TEWS pod is used as an auxiliary to the TEWS system to extend the abilities of the internal TEWS system. The TEWS pod is carried externally on station 5 (centerline).

- 00-10. **Countermeasures Dispenser Set AN/ALE-45 (CMD).** The CMD counters most immediate threats by dispensing chaff, IR flare, and/or other expendable countermeasure payloads.

- 00-11. **Transmission Line Testing.** Refer to TO SR1F-15C-2-99GS-00-2.

- 00-12. **SPECIAL MAINTENANCE REQUIREMENTS.** Refer to TO SR1F-15C-2-99GS-00-2.

- 00-13. **RF TRANSMISSION LINE/WAVEGUIDE/RF COMPONENT TEST PROCEDURES.** Refer to TO SR1F-15C-2-99GS-00-2.

- 00-14. **CONSUMABLE MATERIALS LIST.** Refer to TO SR1F-15C-2-99GS-00-2.

- 00-15. **SUPPORT EQUIPMENT LIST.** Refer to TO SR1F-15C-2-99GS-00-2.

- 00-16. **TEST EQUIPMENT.** Refer to TO SR1F-15C -2-99GS-00-2.

#### **LEGEND**

Figure 00-1. TEWS Block Diagram.

#### **SECTION XI**

#### RADAR WARNING RECEIVER SET AN/ALR-56C (RWR)

## 11-1. SYSTEM FUNCTIONAL DESCRIPTION.

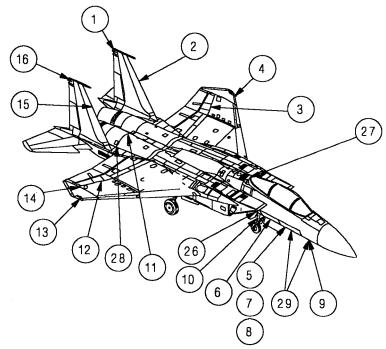

- 11-2. This section contains maintenance instructions for Radar Warning Receiver Set AN/ALR-56C (RWR), which includes equipment listed in Table 11-1 installed on the F-15C and F-15D aircraft. The RWR is one of the subsystems which makes up the tactical electronic warfare system (TEWS).

- 11-3. The primary function of the RWR is to detect RF from enemy fire control radar systems (threats). After detection, the RWR uses this information to process and classify threats and provide jammer management. An audible tone and visual display are produced by the RWR to attract attention to the detected threats and threat location. Determination of jamming requirements is made by comparison of received signals and a stored program threat table. The RWR has a multiple function built-in test (BIT).

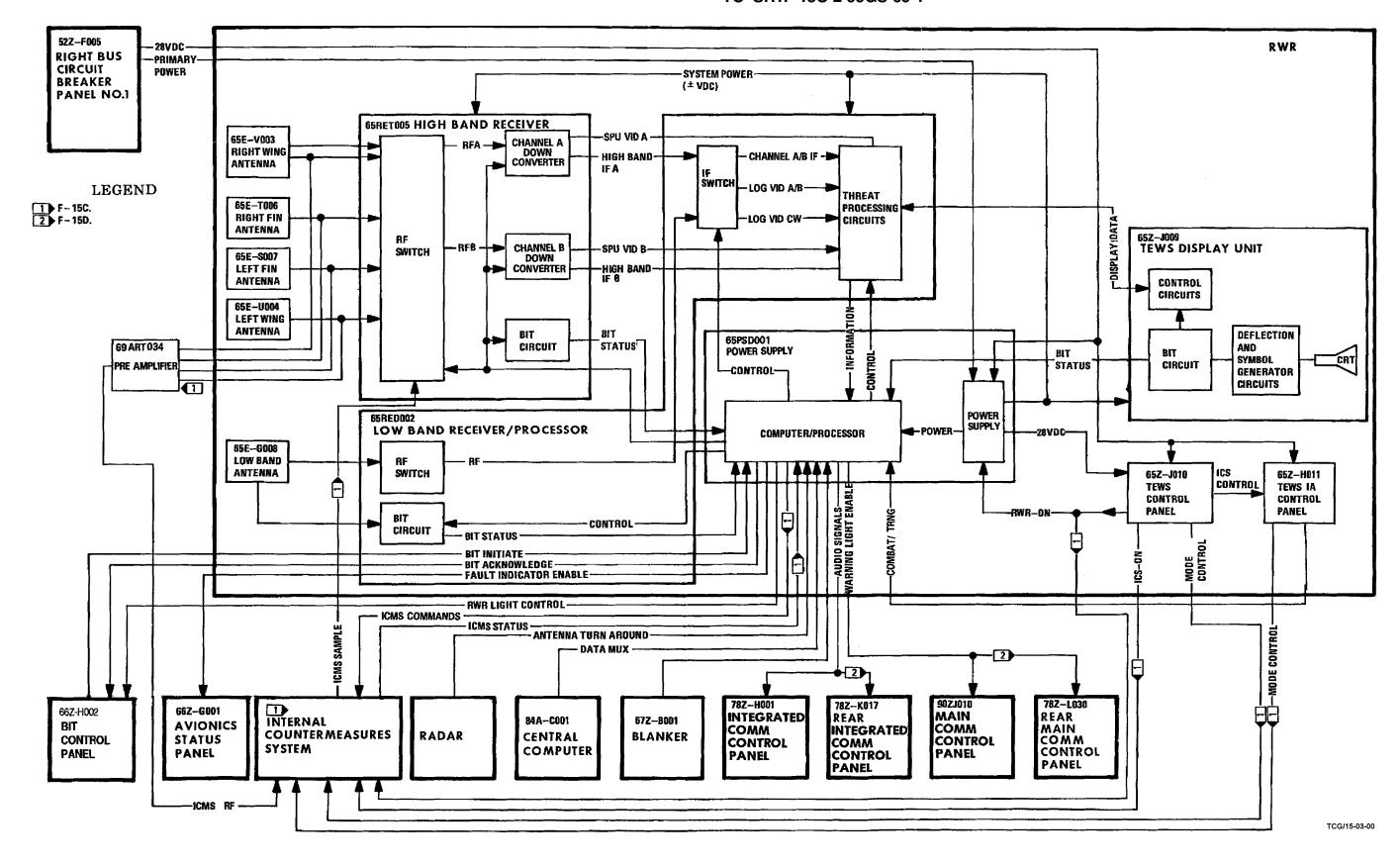

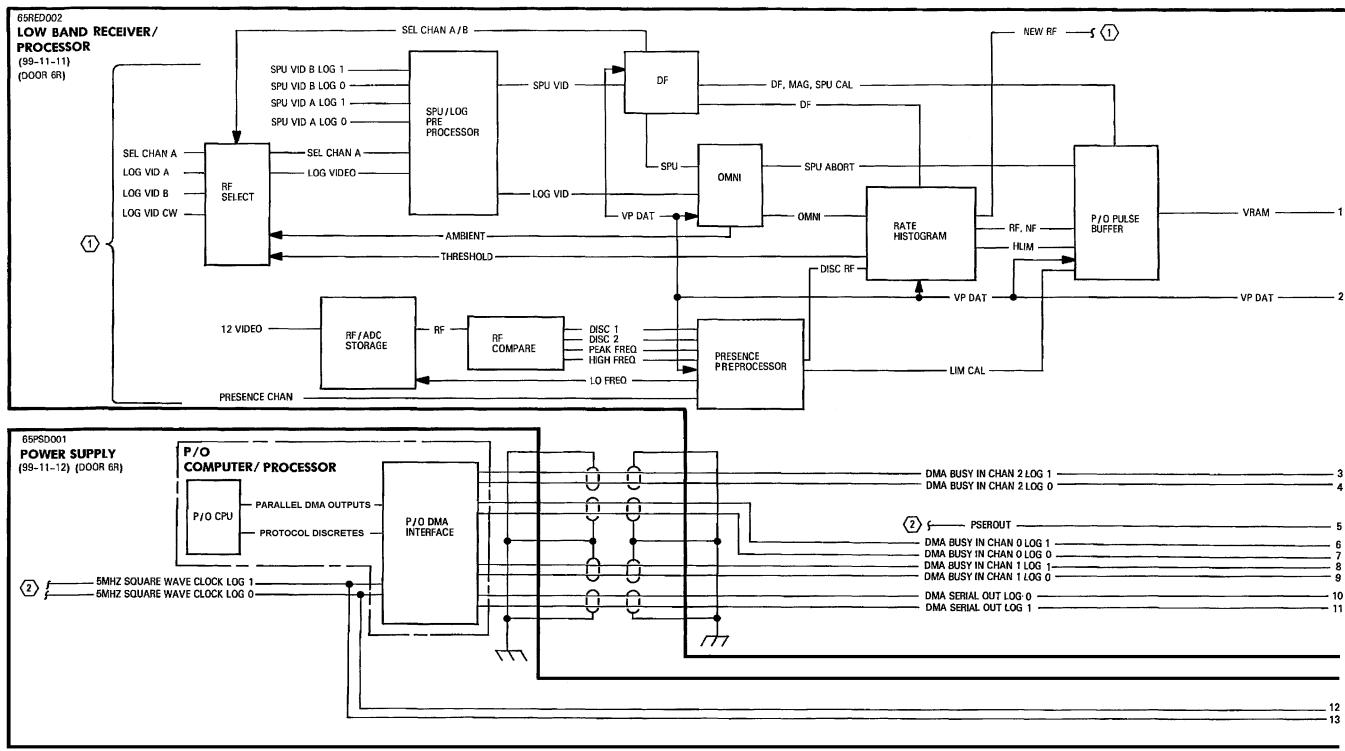

- 11-4. **DESCRIPTION.** See Figures 11-1 and 11-2. The RWR, under programmed control, detects and analyzes RF threats. After detection, the information is used to control jamming against RF transmitting devices that show a threat to the aircraft. RF energy is received through one or more combinations of five antennas and provided to the high band or low band receiver.

- 11-5. Signal Processing. The digitally controlled, low and high band, superheterodyne receivers convert the RF to the required IF. The IF is routed to the processor section of the low band receiver/processor where the received RF intelligence (frequency spectrum) is detected, processed and digitized for transfer to the computer in the power supply. The computer analyzes the digitized information for possible threat transmissions. A match between the received RF sample and a frequency in the threat spectrum will call for threat evaluation.

- 11-6. A computer program enables circuitry in the low band receiver/processor to digitize suspect RF for analysis by the computer to identify potential threats. A threat signal causes the RWR to produce visual and audio warning signals and to automatically activate applicable jamming transmitters in the internal countermeasures set (ICMS).

- 11-7. The RWR BIT verifies hardware and software integrity through C-BIT (continuous BIT), P-BIT (periodic BIT), I-BIT (initiated BIT). It also has a MAINT BIT function that displays a record of RWR BIT failures and a pilot BIT that allows the pilot to monitor the system in-flight.

- a. C-BIT monitors system computer memory parity, the system deadman timer (DMT), and the receiver scan. In the event of power fluctuations, memory parity errors, DMT activation, or scan hang-up, BIT interrupts system processing to perform fault isolation.

- b. P-BIT, also called automatic BIT, invoked by the OFP verifies the operation of the AN/ALR-56C system by doing periodic tests of RWR functions. The complete BIT set has three segments, with one segment performed approximately every four seconds (all three segments are completed approximately every twelve seconds). Some functions, however, require more than one cycle for a complete test. A full system test is completed approximately every minute. Its general approach is to verify that an end to end RWR function is working (excluding actual antenna reception capability), rather than checking individual LRU's or hardware components.

- c. I-BIT, also called manual BIT, initiates a check on the system computer and its memory and verifies the integrity of the software load. It also provides a graphic display of symbology on the TEWS Display for approximately five seconds, then a second display appears for approximately four seconds indicating the word RANCH, brackets and three lines of numbers that represent the RWR OFP, Band 2 ICMS OFP and Band 3 ICMS OFP. In addition, the launch and caution tones can be heard through the headsets.

- d. Maintenance BIT displays matrix "B" (confirmed failures). These failures have been confirmed by the double 5/7 rule and will be displayed with flight write prom data (failures detected in flight). Access to this feature of BIT is provided by initiating manual BIT and cycling the RWR/ICS switch on the TEWS IA control panel between the COMBAT and TRAINING modes.

- 11-8. **LINE REPLACEABLE UNITS.** RWR system line replaceable units (LRU) are identified and listed in Table 11-1.

- 11-9. **COMPONENT DESCRIPTION.** The paragraphs below describe the RWR units. Each unit is hard-mounted and, where required, cooled by the aircraft environmental control system (ECS) that provides air flow to dissipate heat.

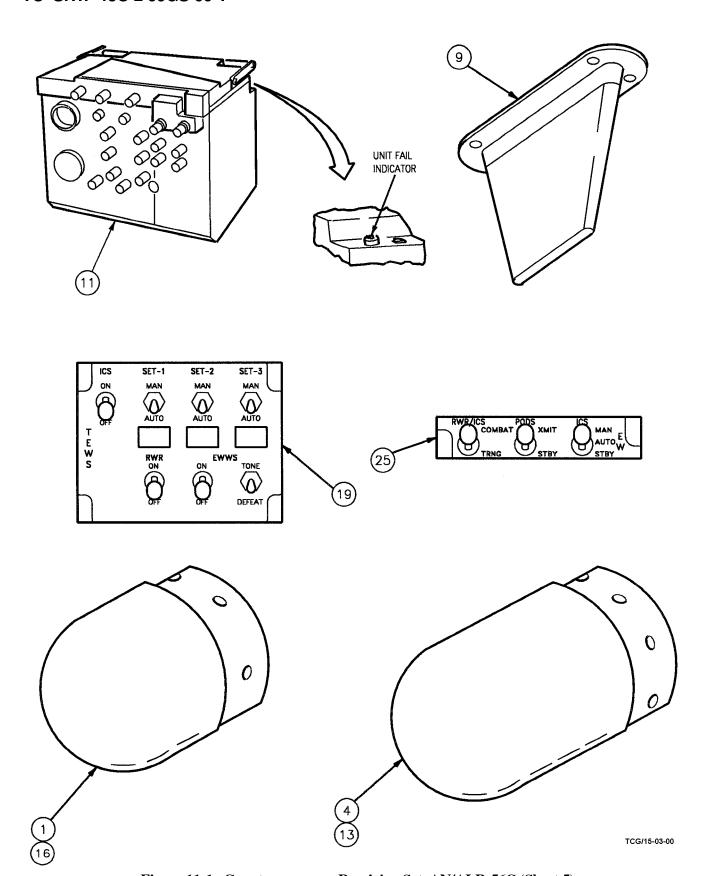

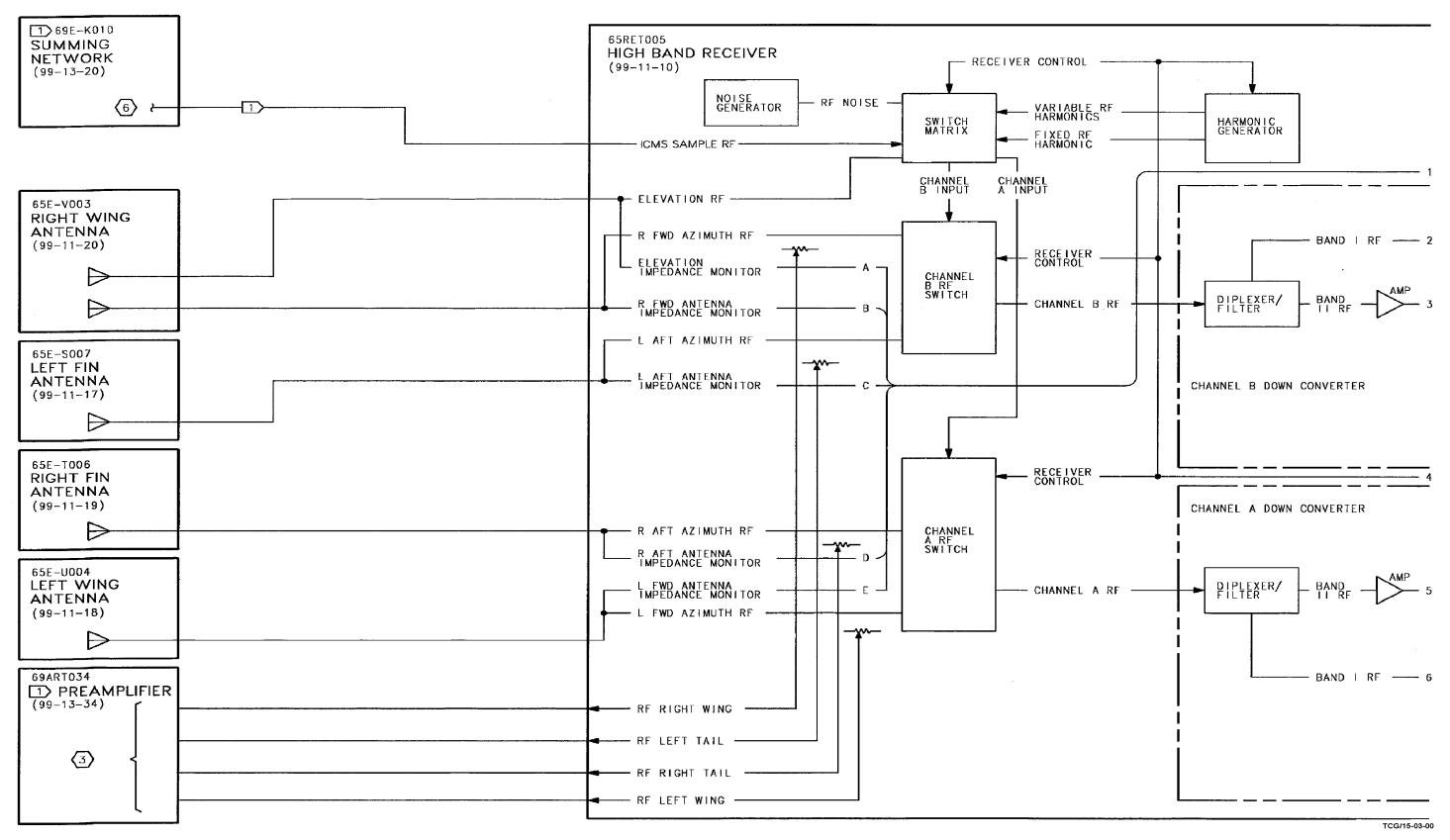

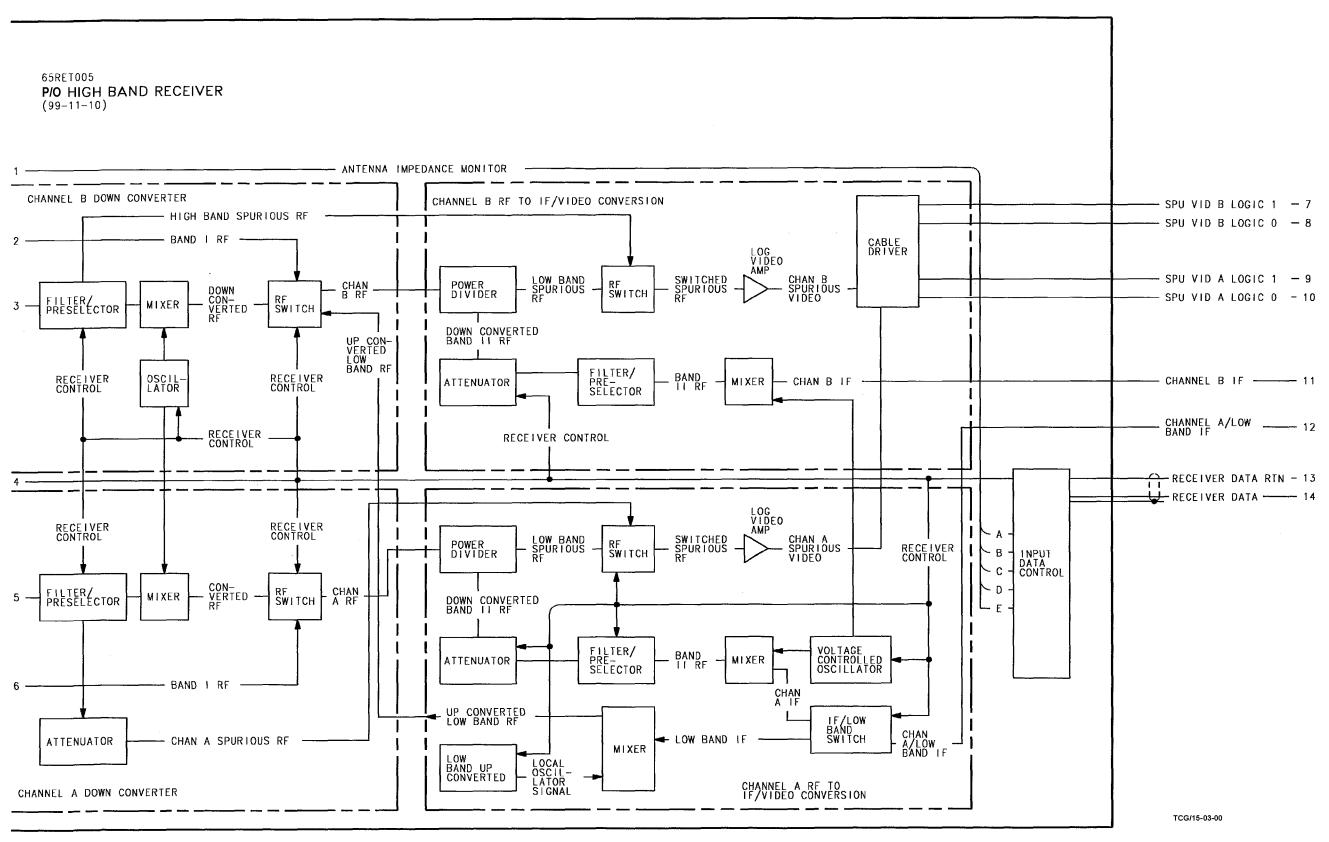

- 11-10. **High Band Receiver (99-11-10).** The high band receiver detects high band RF transmissions and processes them to be analyzed in the low band receiver/processor. The high band transmissions are also used in the direction finding function of the RWR.

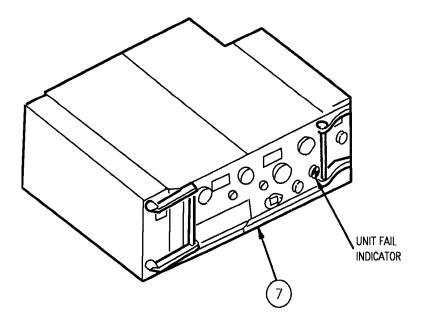

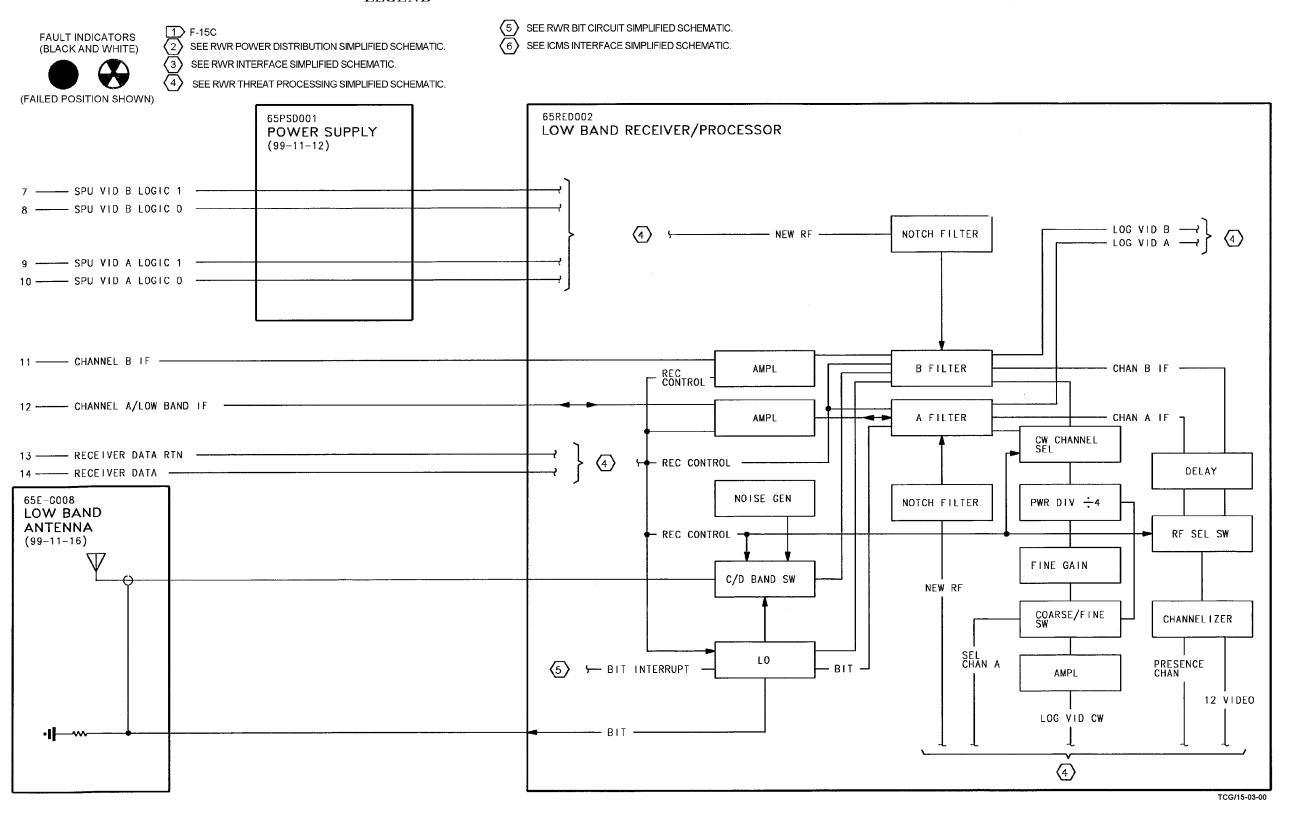

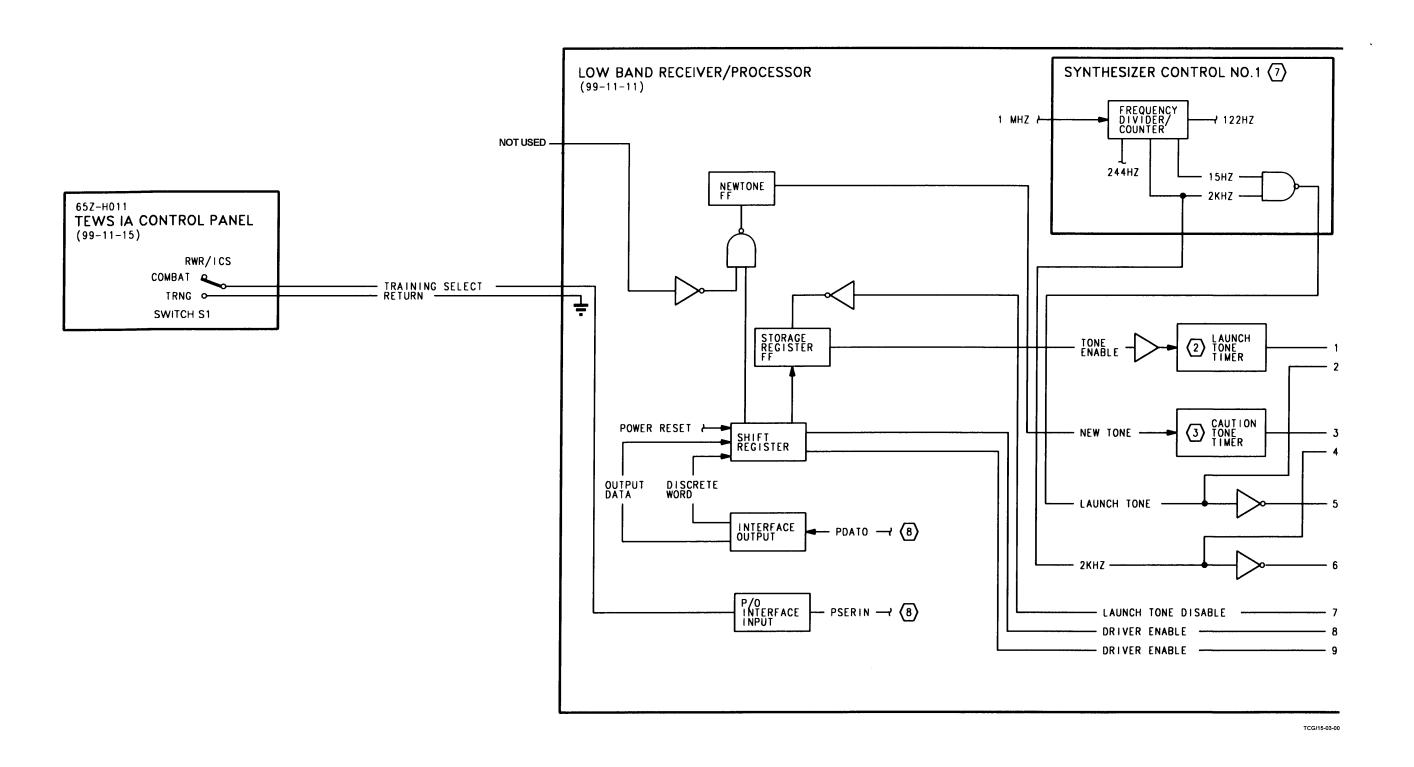

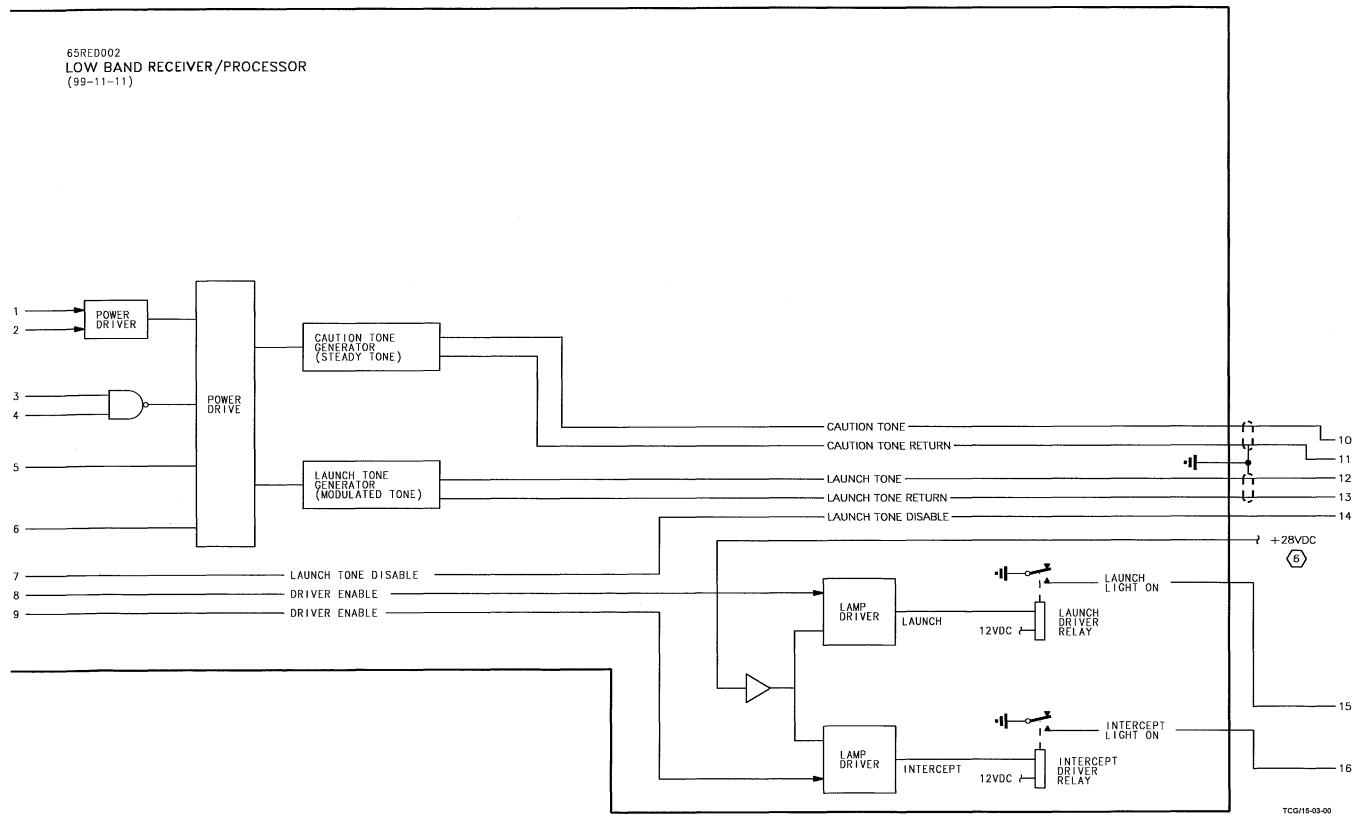

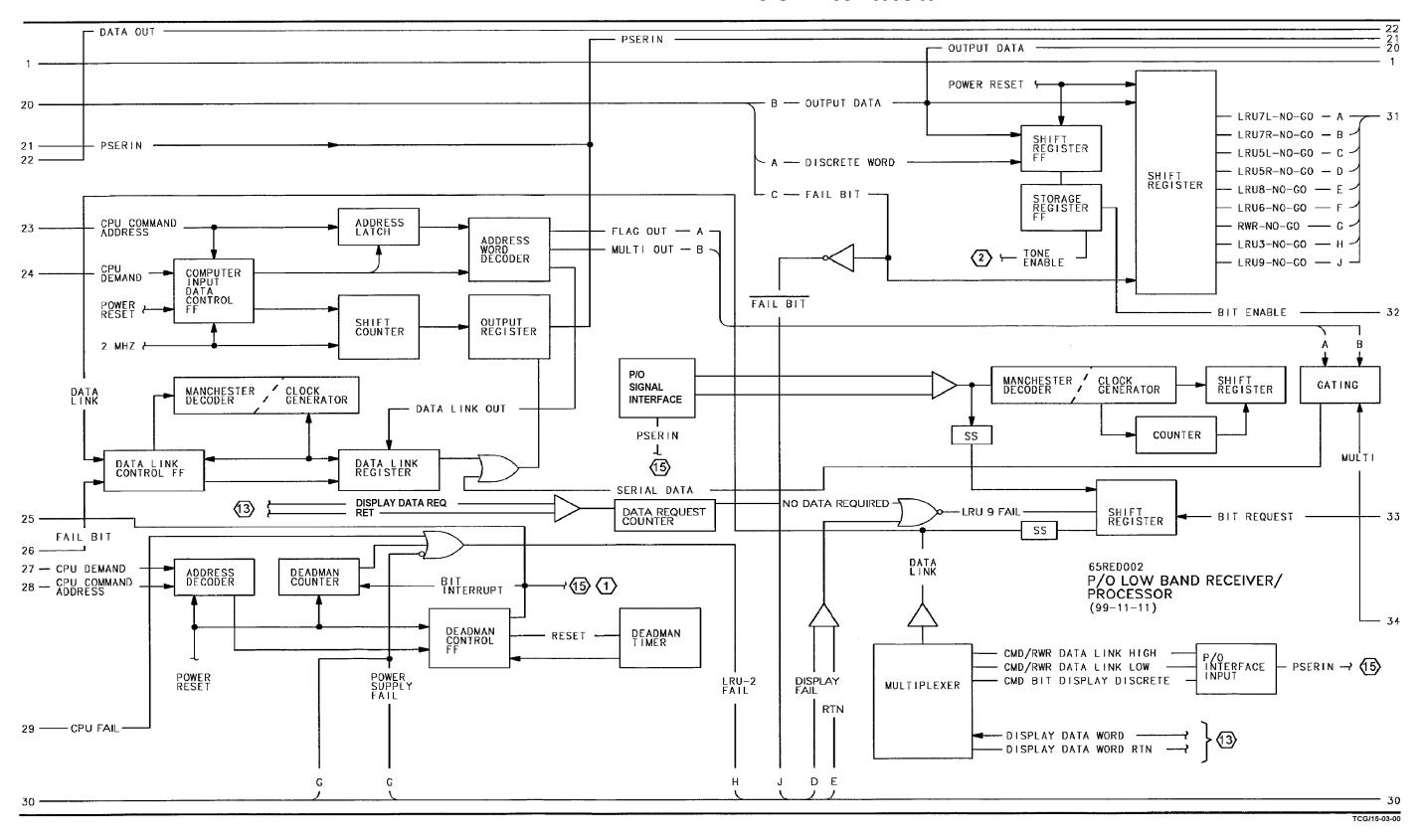

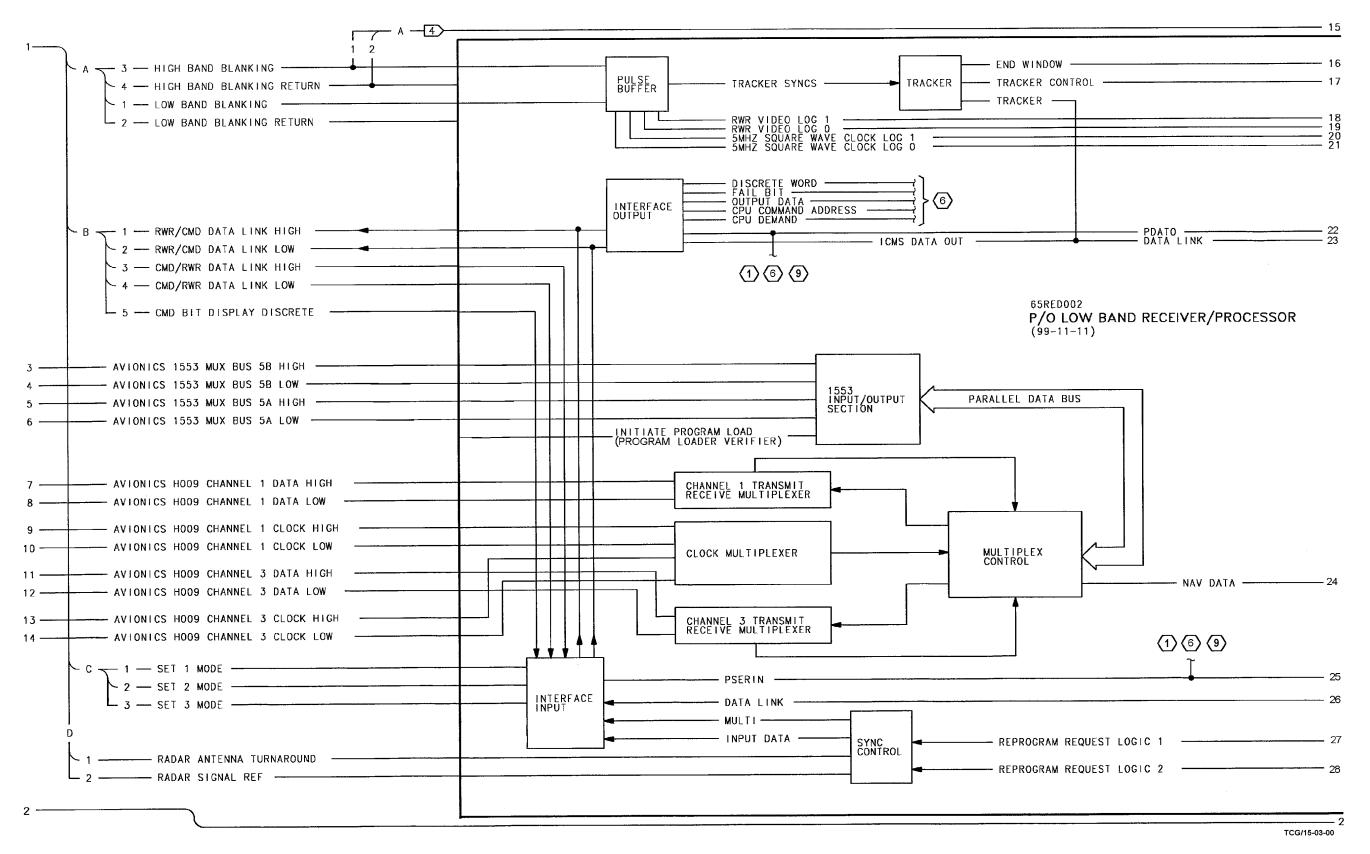

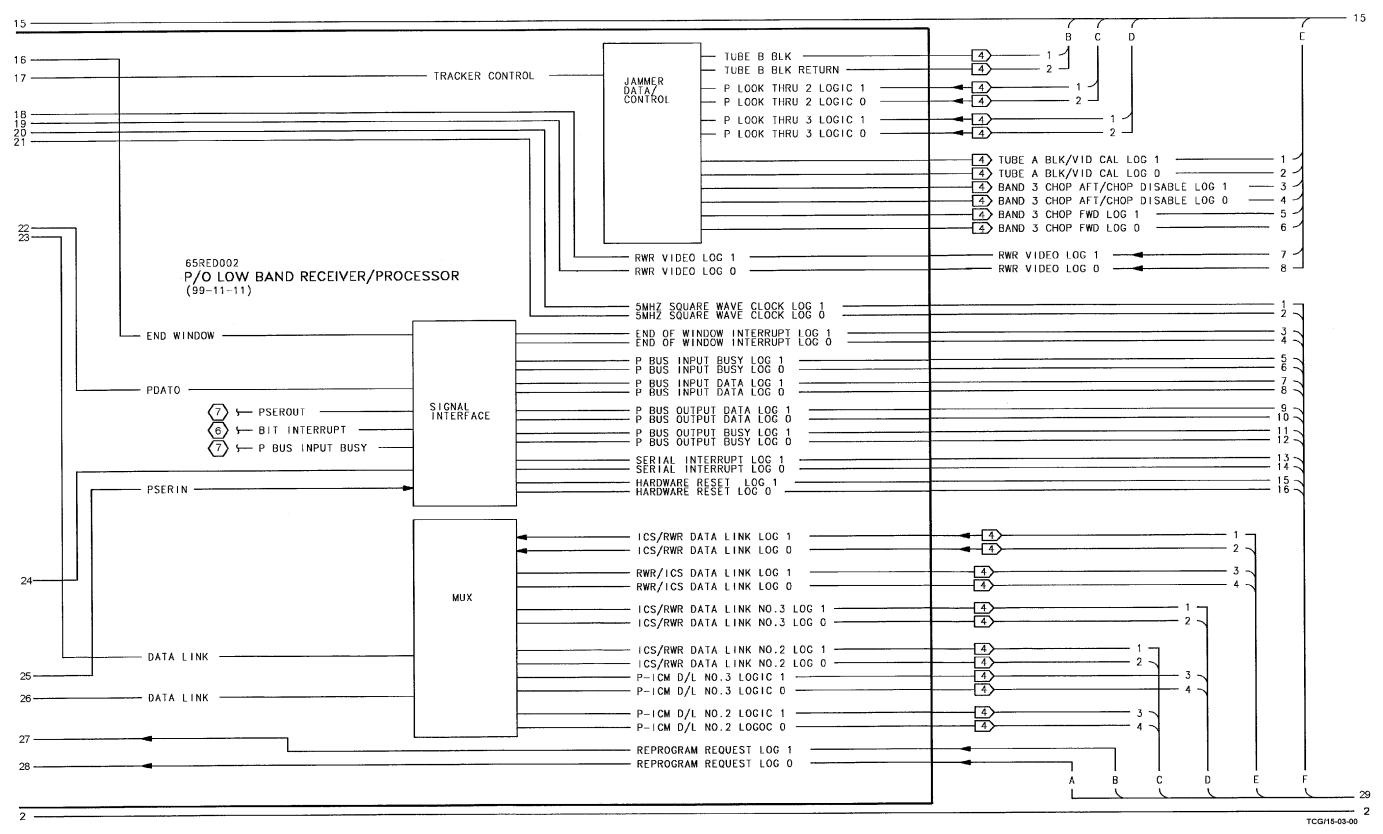

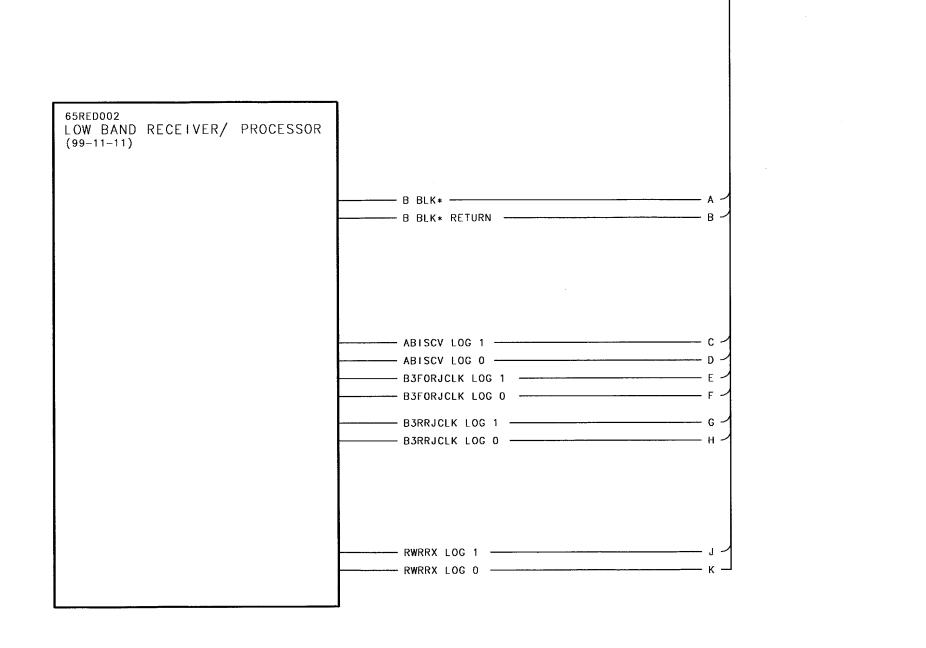

- 11-11. Low Band Receiver/Processor (99-11-11). The low band receiver/processor detects and processes low band transmissions. These transmissions along with high band transmissions are processed and digitized for transfer to the computer in the power supply.

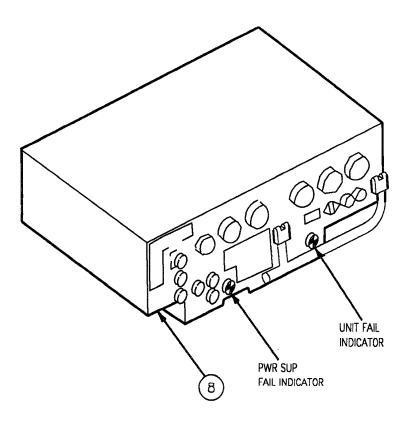

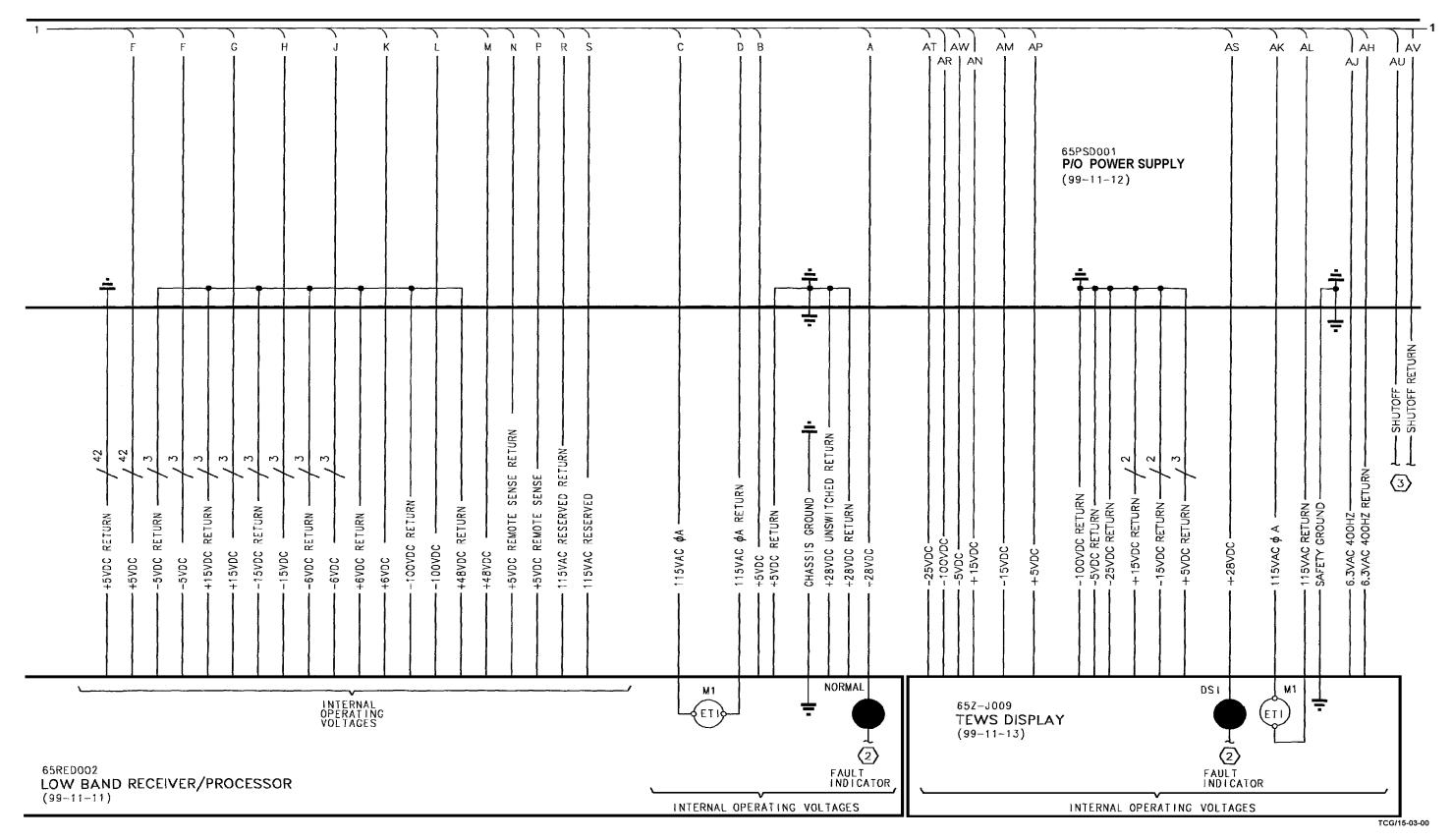

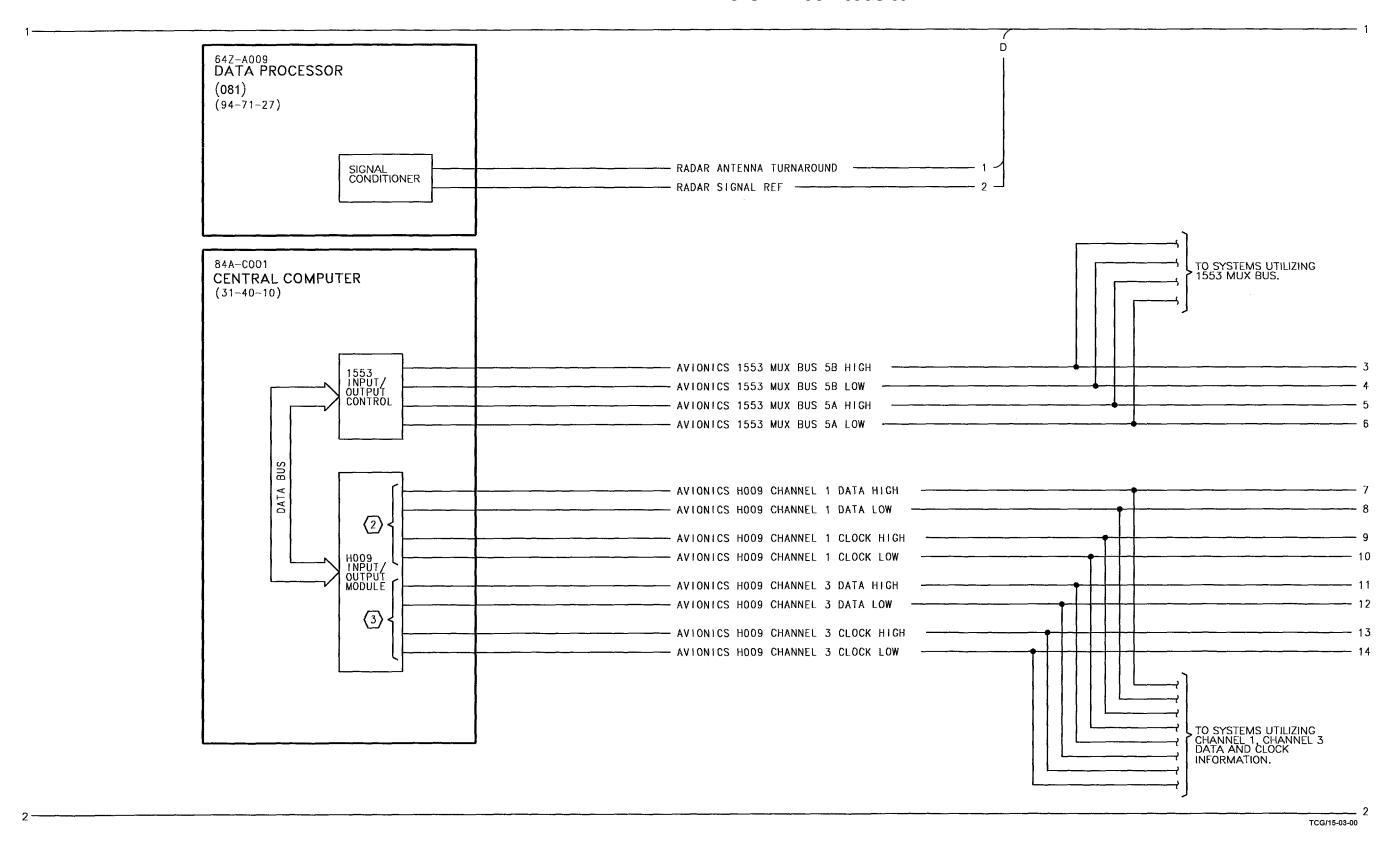

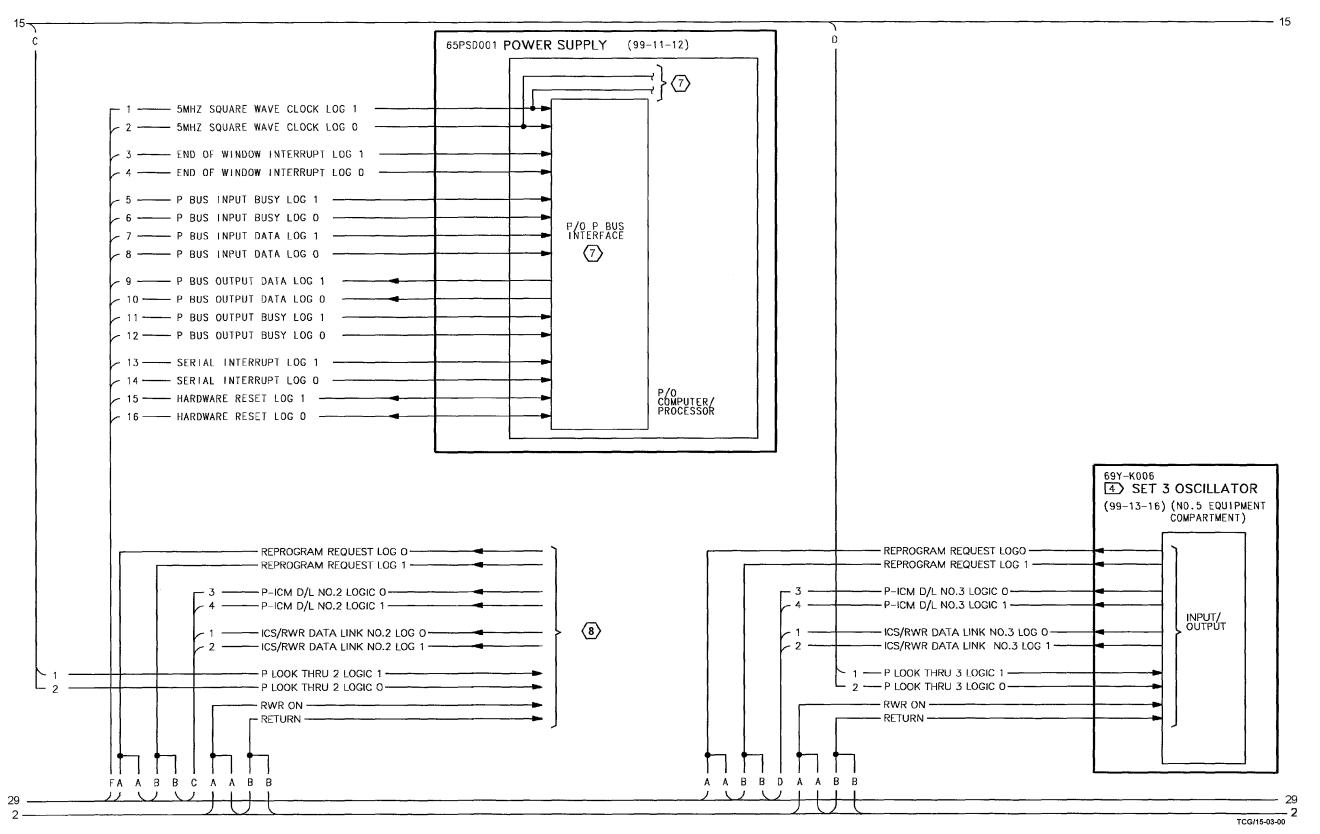

- 11-12. **Power Supply** (**99-11-12**). The power supply converts 115vac, 400 Hz, 3Ø aircraft power to the required ±DC voltages used by the RWR system. The +28vdc aircraft voltage is used for control. An internal computer analyzes digitized low band and high band transmissions to determine all threat parameters.

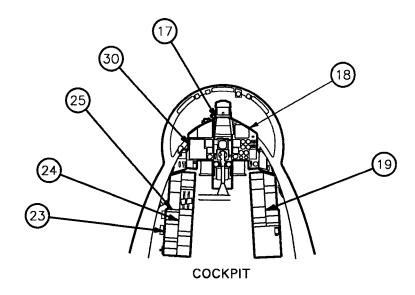

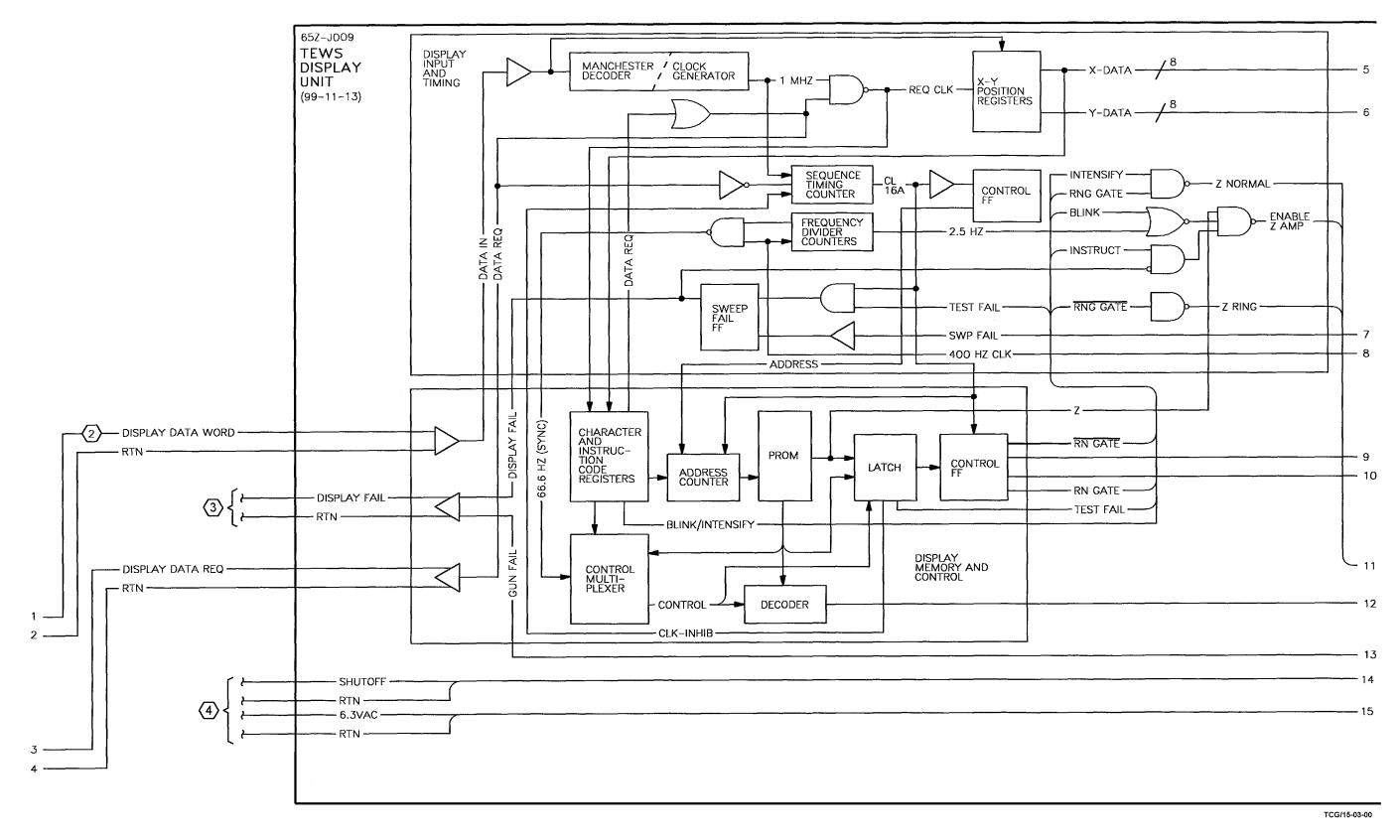

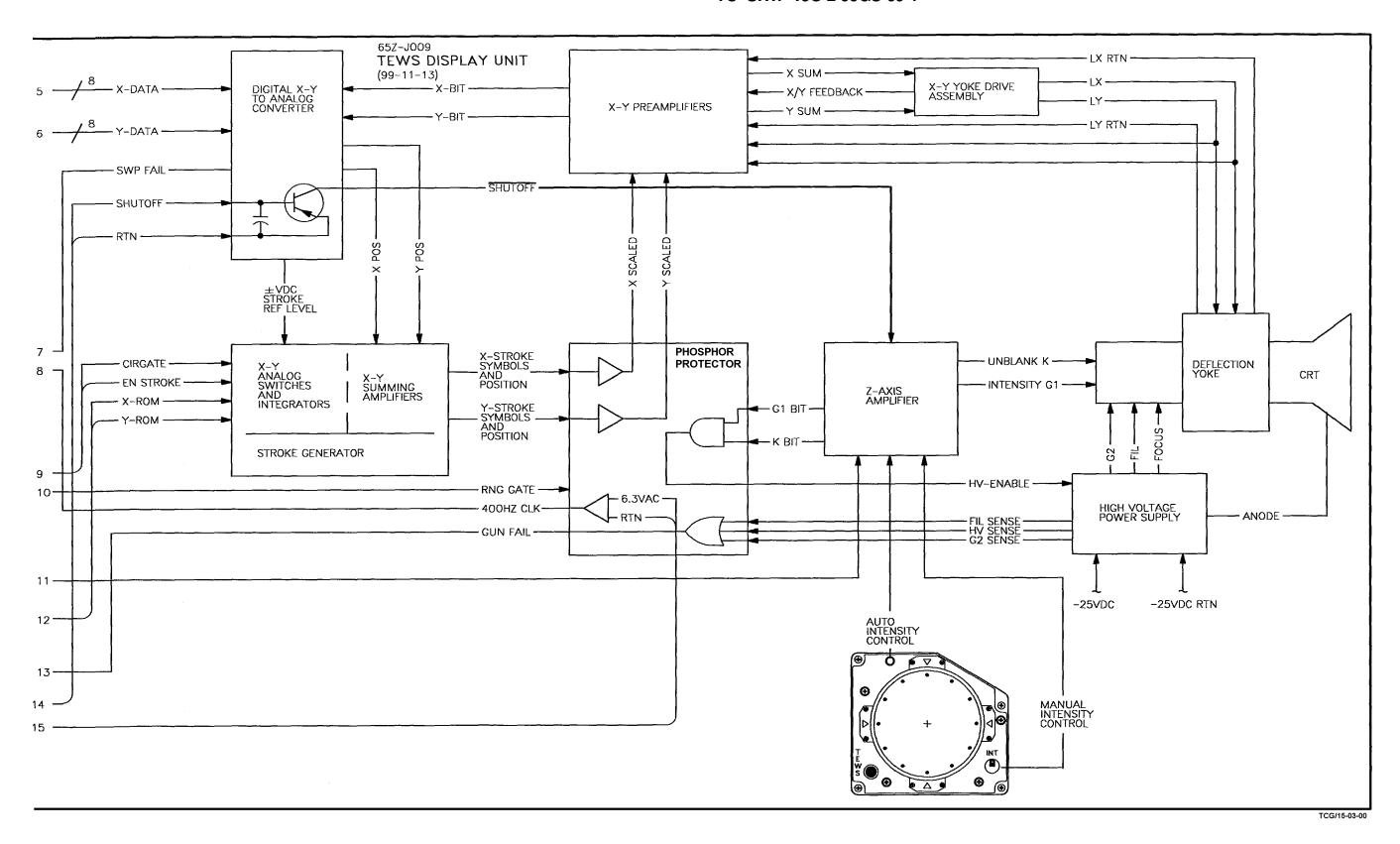

- 11-13. **TEWS Display Unit (99-11-13).** The TEWS display unit visually displays the threat environment.

- 11-14. **TEWS Control Panel (99-11-14).** The TEWS control panel controls the operation of the TEWS.

- 11-15. **TEWS IA Control Panel (99-11-15).** The TEWS IA control panel controls the operational modes of the TEWS.

- 11-16. **Low Band Antenna (99-11-16).** The low band antenna has a single omnidirectional element with a resistively coupled tap for BIT use.

- 11-17. **Left Fin Antenna (99-11-17).** The left fin antenna is used for RF detection and direction finding with the other three high band antennas.

- 11-18. **Left Wing Antenna (99-11-18).** The left wing antenna is used for RF detection and direction finding with the other three high band antennas.

- 11-19. **Right Fin Antenna (99-11-19).** The right fin antenna is used for RF detection and direction finding with the other three high band antennas.

- 11-20. **Right Wing Antenna (99-11-20).** The right

- wing antenna contains two elements. One element is used for RF detection and as an elevation reference for the direction finding function of the system. The other element is used for RF detection and direction finding with the other three high band antennas. The four high band antennas form an omnidirectional pattern around the aircraft each defining 90 degrees of azimuth.

- 11-21. Cable Assembly(ies) (99-11-21 thru 99-11-32). Six cable assemblies transfer RF signals detected by the RWR antennas to the receiving circuits in the high band receiver and low band receiver/processor. The other cable assemblies provide system interface connections. Refer to Table 11-1.

- 11-22. **PRINCIPLES OF OPERATION.** See Figure 11-2. The RWR principles of operation are shown as a description of operating controls and indicators, and operation of the system functions as below:

- a. Power Distribution

- b. Receiving Circuits

- c. Computer/Processor

- d. Threat Processing Circuits

- e. Display Circuits

- f. Warning Lights and Audio Circuits

- g. BIT Circuits

- h. System Interface

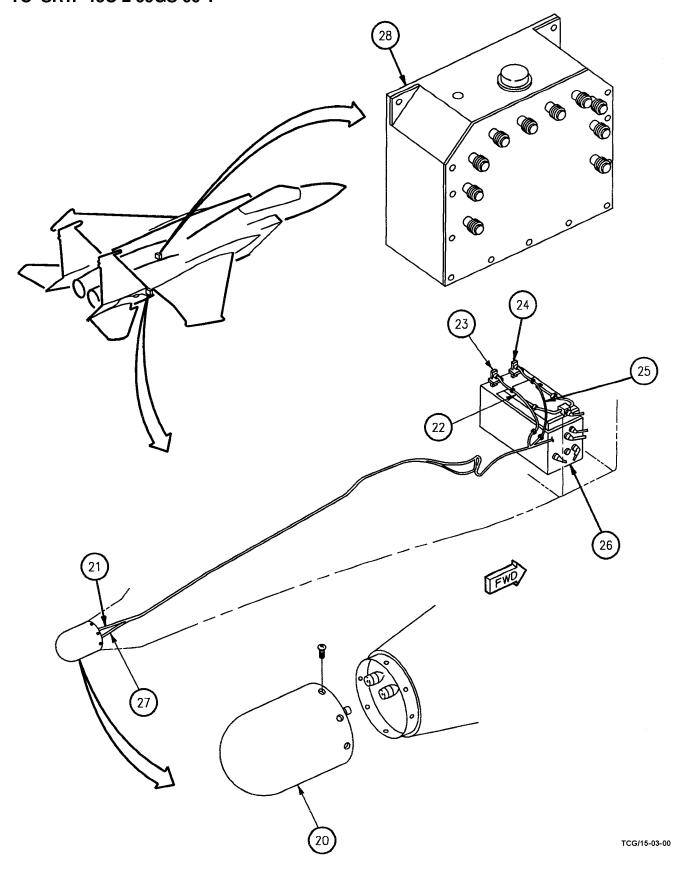

- 11-23. **Controls and Indicators.** All controls and indicators used in RWR operation are shown in Figure 11-1 and described in Table 11-2.

- 1-24. **Display Symbols.** Classified secret. Refer to TO SR1F-15C-2-99GS-00-2, section 11.

- 11-25. **Cockpit Light Indicators.** Classified secret. Refer to TO SR1F-15C-2-99GS-00-2, section 11.

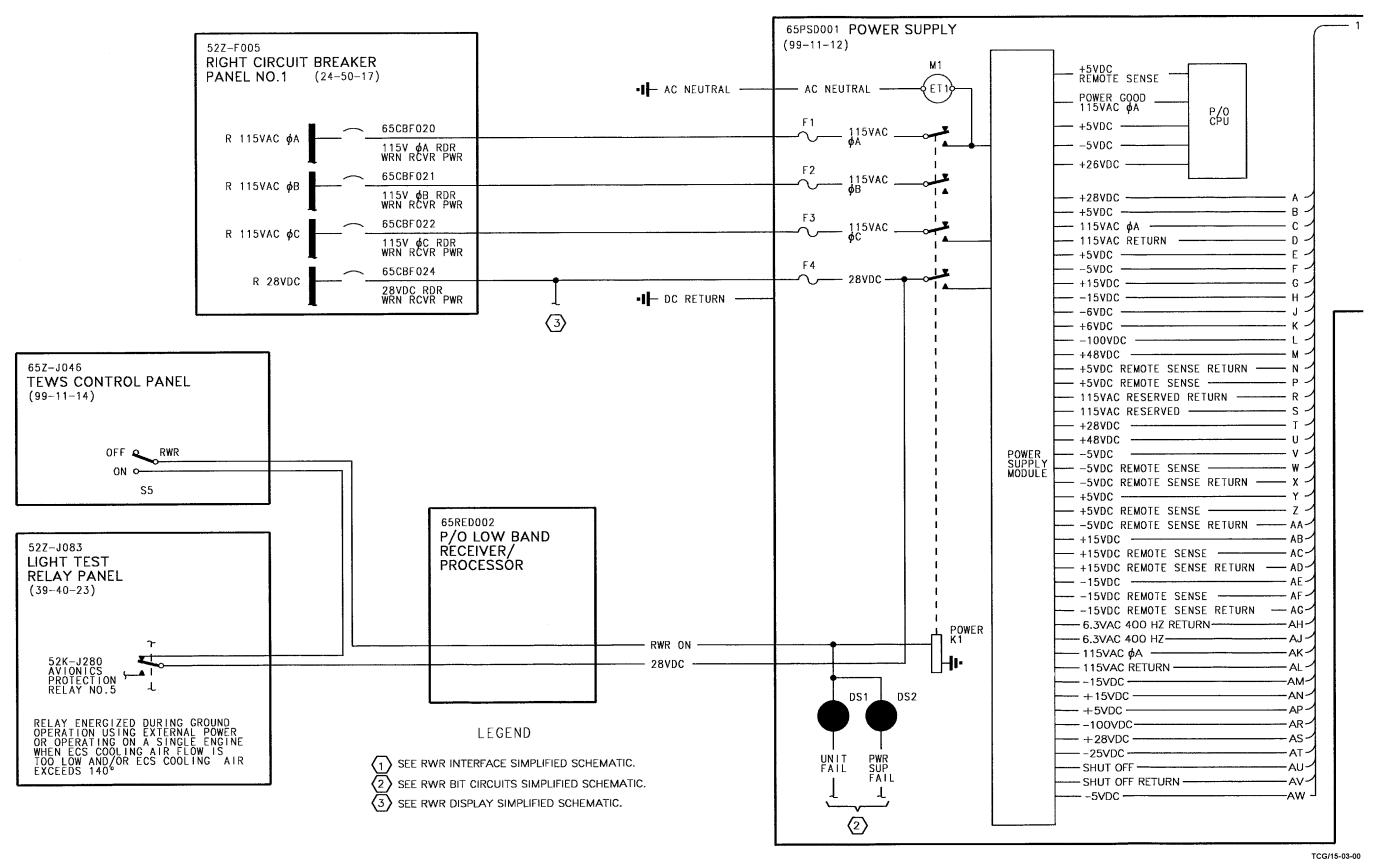

- 11-26. **Power Distribution.** See Figure 11-3. Primary power of 115vac, 400 Hz, 3 Ø and 28vdc is routed to the power supply, while 28vdc only is routed to the TEWS control panel. When external electrical power is applied to the aircraft and before the RWR system is turned on, the RWR light on the BCP is on. RWR power on is done by turning the RWR switch on the TEWS control panel to the ON position. The 28vdc supply is routed from the power supply through the deenergized contacts of avionics protection relay no. 5 (52K-J280) to the control panel. This relay energizes, removing power from RWR, if there is not enough

Table 11-1. Line Replaceable Units

| Common Name                         | S/S/SN   | Ref. Des.         | Nomenclature                                |

|-------------------------------------|----------|-------------------|---------------------------------------------|

| 1 AI Light Relay                    | 39-40-22 | 55K-Y008          | Relay                                       |

| SAM Light Relay                     | 39-40-22 | 55K-Y006          | Relay                                       |

| High Band Receiver (LRU-6)          | 99-11-10 | 64RET005          | Countermeasures Receiver,<br>R-2245/ALR-56C |

| Low Band Receiver/Processor (LRU-3) | 99-11-11 | 65RED002          | Countermeasures Receiver,<br>R-2244/ALR-56C |

| Power Supply (LRU-2)                | 99-11-12 | 65PSD001          | Power Supply<br>PP-7855/ALR-56C             |

| TEWS, Display Unit (LRU-9)          | 99-11-13 | 65Z-J009          | Countermeasures Display IP-1164B/<br>ALR-56 |

| TEWS, Control Panel (LRU-10)        | 99-11-14 | 65Z <b>-</b> J010 | Receiver Control C-9428/ALR-56              |

| TEWS IA Control Panel (LRU-11)      | 99-11-15 | 65Z-H011          | Receiver Control C-9429/ALR-56              |

| Low Band Antenna (LRU-8)            | 99-11-16 | 65E-G008          | Antenna AS-2934/ALR-56                      |

| Left Fin Antenna (LRU-7L)           | 99-11-17 | 65E-S007          | Antenna Group OE-169/ALR-56                 |

| Left Wing Antenna (LRU-5L)          | 99-11-18 | 65E-U004          | Antenna Group OE-167/ALR-56                 |

| Right Fin Antenna (LRU-7R)          | 99-11-19 | 65E-T006          | Antenna Group OE-168/ALR-56                 |

| Right Wing Antenna (LRU-5R)         | 99-11-20 | 65E-V003          | Antenna Group OE-166/ALR-56                 |

| BIT Cable Assembly (SW289A)         | 99-11-21 | 65E-G008          | Cable Assembly (SW289A)                     |

| 2 RF Sample Cable Assembly          | 99-11-22 | TE186A            | Cable Assembly (TE186A)                     |

| 2 RF Sample Cable Assembly          | 99-11-23 | TE186B            | Cable Assembly (TE186B)                     |

| 2 RF Sample Cable Assembly          | 99-11-24 | TE186C            | Cable Assembly (TE186C)                     |

| Cable Assembly                      | 99-11-25 | 65W-R501          | Cable Assembly (SW1A)                       |

| Cable Assembly                      | 99-11-26 | 65W-V502          | Cable Assembly (SW2A)                       |

| Cable Assembly                      | 99-11-29 | 65W-V503          | Cable Assembly (SW3A)                       |

| Cable Assembly                      | 99-11-30 | 65W-U504          | Cable Assembly (SW4A)                       |

| Cable Assembly                      | 99-11-31 | 65W-T506          | Cable Assembly (SW5A)                       |

| Cable Assembly                      | 99-11-32 | 65W-S507          | Cable Assembly (SW6A)                       |

| BIT Cable Assembly (SW289B)         | 99-11-33 | 65E-G008          | Cable Assembly (SW289B)                     |

| F-15D<br>2 F-15C                    |          |                   |                                             |

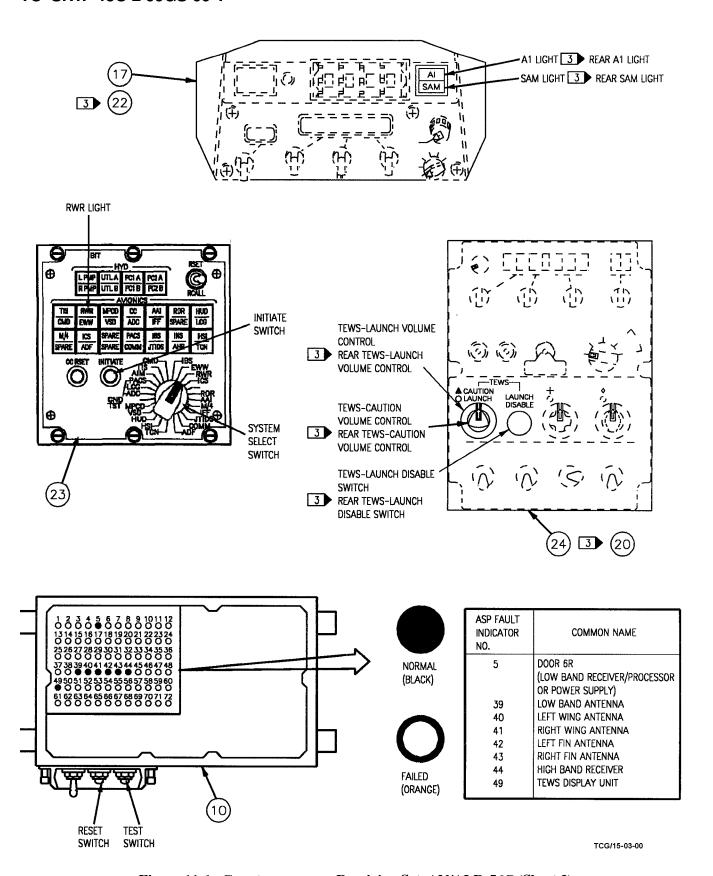

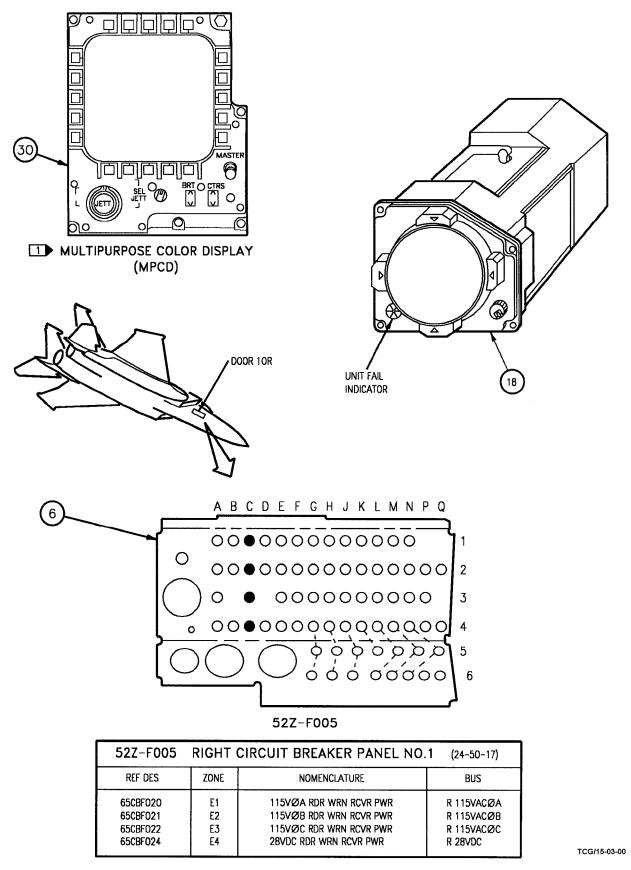

# LEGEND 1 RELATED TO BUT NOT PART OF RADAR WARNING RECEIVER 2 F-15C 3 F-15D

| INDEX NO. | COMMON NAME                           | S/S/SN   | REF DES  | ACCESS                       |

|-----------|---------------------------------------|----------|----------|------------------------------|

| 1         | LEFT FIN ANTENNA                      | 99-11-17 | 65E-S007 | LEFT VERTICAL STABILIZER     |

| 2         | CABLE ASSEMBLY                        | 99-11-32 | 65W~S507 | AFT FUSELAGE AND LEFT FIN    |

| 3         | CABLE ASSEMBLY                        | 99-11-30 | 65W-U504 | LEFT WING                    |

| 4         | LEFT WING ANTENNA                     | 99-11-18 | 65E~U004 | LEFT WING TIP                |

| 5         | CABLE ASSEMBLY                        | 99-11-25 | 65W-R501 | NLG FORWARD DOOR AND DOOR 6R |

| 6         | RIGHT BUS CIRCUIT BREAKER PANEL NO. 1 | 24-50-17 | 52Z-F005 | D00R 10R                     |

| 7         | LOW BAND RECEIVER/PROCESSOR           | 99-11-11 | 65RED002 | DOOR 6R                      |

| 8         | POWER SUPPLY                          | 99-11-12 | 65PSD001 | DOOR 6R                      |

| 9         | LOW BAND ANTENNA                      | 99-11-16 | 65E-G008 | NLG FORWARD DOOR             |

| 10        | AVIONICS STATUS PANEL                 | 31-50-18 | 66Z-G001 | NOSE WHEELWELL               |

| 11        | HIGH BAND RECEIVER                    | 99-11-10 | 65RET005 | DOOR 197                     |

| 12        | CABLE ASSEMBLY                        | 99-11-29 | 65W-V503 | RIGHT WING                   |

| 13        | RIGHT WING ANTENNA                    | 99-11-20 | 65E-V003 | RIGHT WING TIP               |

| 14        | CABLE ASSEMBLY                        | 99-11-26 | 65W-V502 | RIGHT WING                   |

| 15        | CABLE ASSEMBLY                        | 99-11-31 | 65W-T506 | AFT FUSELAGE AND RIGHT FIN   |

| 16        | RIGHT FIN ANTENNA                     | 99-11-19 | 65E-T006 | RIGHT VERTICAL STABILIZER    |

| 17        | MAIN COMM CONTROL PANEL               | 23-24-30 | 90Z-J010 | COCKPIT                      |

| 18        | TEWS DISPLAY UNIT                     | 99-11-13 | 65Z-J009 | COCKPIT                      |

| 19        | TEWS CONTROL PANEL                    | 99-11-14 | 65Z-J010 | COCKPIT                      |

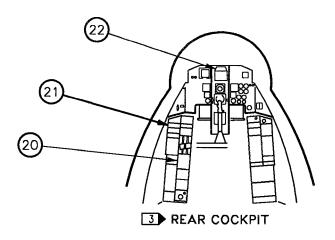

| 3 20      | REAR INTEGRATED COMM CONTROL PANEL    | 23-24-29 | 78Z-K017 | REAR COCKPIT                 |

| 3 21      | AVIONICS REPLAY PANEL 4               | 39-40-22 | 55Z-Y013 | REAR COCKPIT                 |

| 3 22      | REAR MAIN COMM CONTROL PANEL          | 23-24-31 | 78Z-L030 | REAR COCKPIT                 |

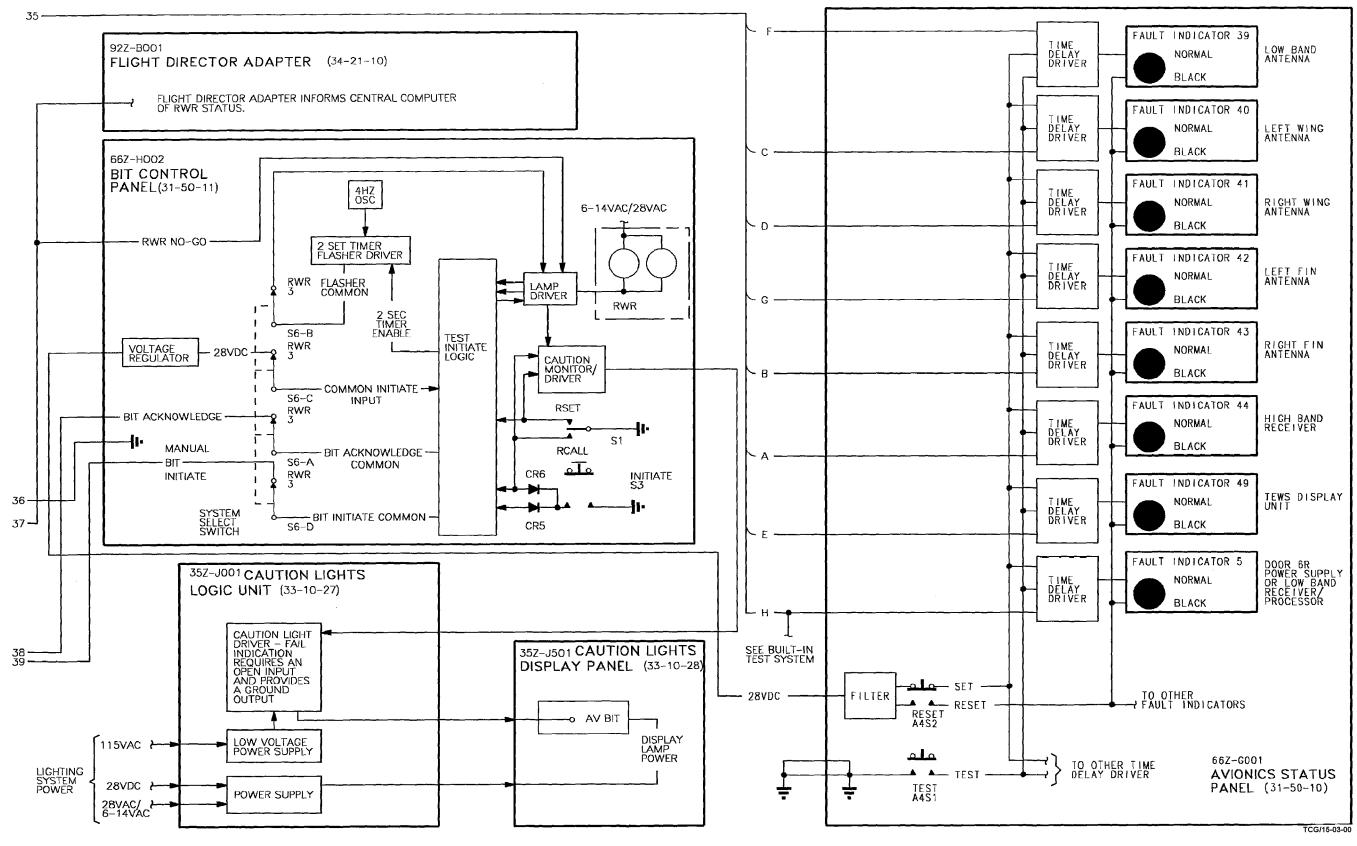

| 1 23      | BIT CONTROL PANEL                     | 31-50-11 | 66Z-H002 | COCKPIT                      |

| 1 24      | INTEGRATED COMM CONTROL PANEL         | 23-24-28 | 78Z-H001 | COCKPIT                      |

| 25        | TEWS IA CONTROL PANEL                 | 99-11-15 | 65Z-H011 | COCKPIT                      |

| 2 26      | RF SAMPLE CABLE ASSEMBLY              | 99-11-22 | TE-186A  | AFT FUSELAGE AND ECS BAY     |

| 2 27      | RF SAMPLE CABLE ASSEMBLY              | 99-11-23 | TE-186B  | NO. 5 EQUIPMENT COMPARTMENT  |

| 2 28      | RF SAMPLE CABLE ASSEMBLY              | 99-11-24 | TE-186C  | AFT FUSELAGE                 |

| 29        | BIT CABLE ASSEMBLY                    | 99-11-21 | SW289A   | NLG FOWARD DOOR AND DOOR 6R  |

| 1 30      | MULTIPURPOSE COLOR DISPLAY            | 94-10-27 |          | COCKPIT                      |

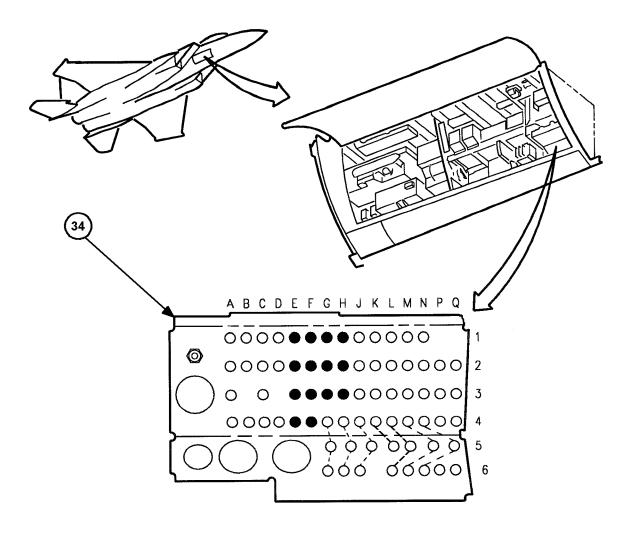

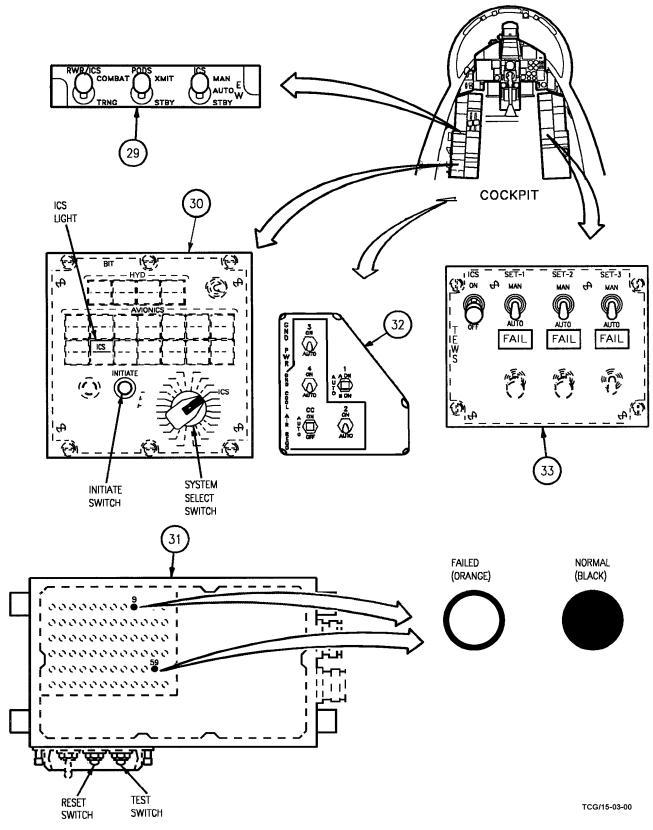

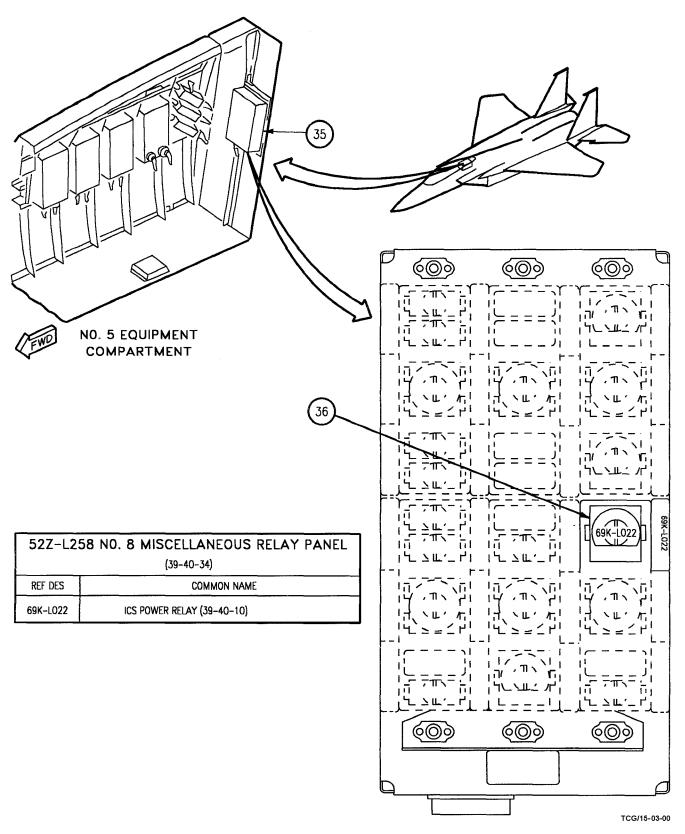

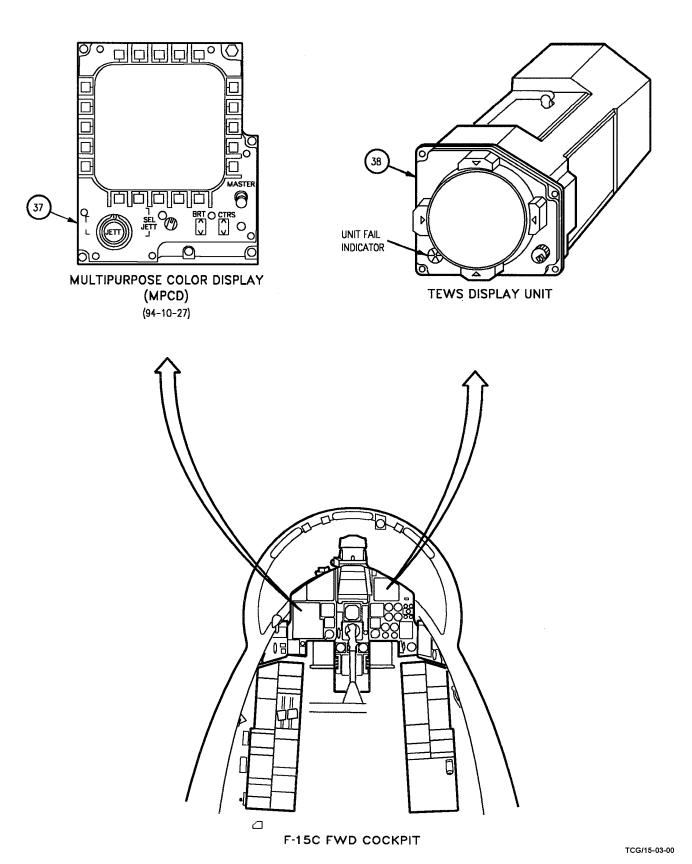

Figure 11-1. Countermeasures Receiving Set AN/ALR-56C (Sheet 1 of 6)

Figure 11-1. Countermeasures Receiving Set AN/ALR-56C (Sheet 2)

Figure 11-1. Countermeasures Receiving Set AN/ALR-56C (Sheet 3)

Figure 11-1. Countermeasures Receiving Set AN/ALR-56C (Sheet 4)

Figure 11-1. Countermeasures Receiving Set AN/ALR-56C (Sheet 5)

99-11-00

Figure 11-1. Countermeasures Receiving Set AN/ALR-56C (Sheet 6)

Figure 11-2. RWR Functional Block Diagram

11-10

cooling air flow when using external electrical power or single engine operation. The ECS light on caution lights display panel indicates low air flow when on.

11-27. The RWR on signal energizes relay K1 providing fused 3 Ø primary voltage to the power supply module. A 115vac, 400 Hz, Ø A power source is routed to the low band receiver/processor and TEWS display unit to drive their elapsed time indicators. The high band receiver elapsed time indicator uses 28vdc. The 6.3vac, 400 Hz is routed to the TEWS display unit as a display reference voltage. The fused 28vdc is routed to each system LRU fail indicator. The RWR light on the BCP goes out, indicating that power has

been applied and the power supply is functional. However, if the power supply fails to turn on, the light remains on. After the RWR has been turned on, the RWR light will come on if there is a system failure.

11-28. The -5vdc, 5vdc, and 15vdc outputs are sent to the high band receiver. The 5vdc output to the low band receiver/processor CPU is remotely sensed. This is to provide voltage regulation at the load for these voltages. At turn-on, all outputs from the DC power supplies are continuously monitored for high voltage, low voltage, or overcurrent conditions. If a malfunction is detected, the power supply and the defective LRU are disabled.

Table 11-2. Controls and Indicators

| Control/Indicator                                     | Position/Condition | Function/Indication                                                                                                                                                                           |  |  |

|-------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TEWS Control Panel                                    |                    |                                                                                                                                                                                               |  |  |

| RWR ON/OFF switch                                     | ON                 | a. Enables 115vac, 400 hz 3Ø and +28vdc aircraft power application to RWR.                                                                                                                    |  |  |

|                                                       |                    | b. Applies an RWR ON signal to ICMS, indicating to ICMS that RWR is on and will receive and/or transmit ICMS programmed data.                                                                 |  |  |

|                                                       | OFF                | a. Removes RWR system power.                                                                                                                                                                  |  |  |

|                                                       |                    | b. Disables RWR and ICMS data communication.                                                                                                                                                  |  |  |

| I ICS ON/OFF switch                                   | ON                 | Enables 115vac, 400 Hz, 3Ø and +28vdc aircraft power application to ICMS.                                                                                                                     |  |  |

|                                                       | OFF                | a. Removes ICMS system power.                                                                                                                                                                 |  |  |

|                                                       |                    | b. Keeps relay K1, in TEWS control panel, energized, enabling a reduced (10 percent) cooling air application to ICMS.                                                                         |  |  |

| SET-1, SET-2, SET-3 switches                          | AUTO               | Enables selected ICMS transmitting Set 2 or Set 3 to be controlled by RWR when ICS MAN/AUTO/STBY switch on TEWS IA control panel is in MAN. This switch is non-functional for Set 1 (Band 3). |  |  |

| NOTE: SET 1= Band 3<br>SET 2= Band 2<br>SET 3= Band 1 |                    |                                                                                                                                                                                               |  |  |

|                                                       | MAN                | Enables a selected ICMS transmitting set to be controlled independently when ICS MAN/AUTO/ STBY switch on TEWS IA control panel is in MAN.                                                    |  |  |

Table 11-2. Controls and Indicators (CONT.)

| Control/Indicator               | Position/Condition | Function/Indication                                                                                                                                                                                                |  |  |

|---------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| SET-1, SET-2, SET-3 FAIL lights | ON                 | Indicates a failure in selected ICMS transmitting set.                                                                                                                                                             |  |  |

|                                 | Not on             | Indicates selected ICMS transmitting set is operating correctly.                                                                                                                                                   |  |  |

| EWWS ON/<br>OFF switch          | ON                 | Not used.                                                                                                                                                                                                          |  |  |

|                                 | OFF                | Not used.                                                                                                                                                                                                          |  |  |

| EWWS TONE/DEFEAT switch         | TONE               | Not used.                                                                                                                                                                                                          |  |  |

|                                 | DEFEAT             | Not used.                                                                                                                                                                                                          |  |  |

| TEWS IA Control Panel           |                    |                                                                                                                                                                                                                    |  |  |

| RWR/ICS switch                  | COMBAT             | Enables RWR normal preflight message (PFM). Enables ICMS AUTO mode.                                                                                                                                                |  |  |

|                                 | TRNG               | Enables RWR training mode and alternate preflight message. Enables ICMS training mode.                                                                                                                             |  |  |

| PODS XMIT/STBY switch           | XMIT               | Not used.                                                                                                                                                                                                          |  |  |

|                                 | STBY               | Not used                                                                                                                                                                                                           |  |  |

| ☐☐ ICS MAN/AUTO/STBY switch     | MAN                | Enables AUTO or MAN modes to be selected by SET-1, 2 or 3 switches on the TEWS control panel.                                                                                                                      |  |  |

|                                 | AUTO               | ICMS sets are maintained in AUTO mode and are controlled by RWR.                                                                                                                                                   |  |  |

|                                 | STBY               | a. Puts all ICMS sets in STBY mode.                                                                                                                                                                                |  |  |

|                                 |                    | b. Keeps relay K1, in TEWS control panel energized, enabling a reduced (10 percent) cooling air application to ICMS.                                                                                               |  |  |

| TEWS Display Unit               |                    |                                                                                                                                                                                                                    |  |  |

| INT control                     | CW or CCW rotation | Normally controls display intensity. CW rotation increases intensity; however an ambient light photo sensor, mounted on display, automatically adjust display intensity in proportion to ambient light variations. |  |  |

**Table 11-2.** Controls and Indicators (CONT)

| Control/Indicator        | Position/Condition         | Function/Indication                                                                                                                                                                                          |

|--------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | BIT C                      | ontrol Panel                                                                                                                                                                                                 |

| System select switch     | RWR                        | In RWR position selects and tells RWR system when manual BIT is to be done.                                                                                                                                  |

| INITIATE                 | Press and release          | Enables RWR BIT program.                                                                                                                                                                                     |

| RWR light                | On (steady)                | a. When RWR is OFF.                                                                                                                                                                                          |

|                          |                            | b. When RWR is on and an RWR system failure occurs.                                                                                                                                                          |

|                          | On ( flashing )            | a. Flashes for approximately 10 seconds during time duration of initiated BIT cycle and then goes off.                                                                                                       |

|                          |                            | b. If light flashes intermittently during normal operation, a partial failure is being detected by program controlled automatic BIT. Receiver operation continues with a possibility of reduced performance. |

|                          | Not on                     | When RWR system is on and operating normally.                                                                                                                                                                |

|                          | Multipurpo                 | ose Color Display                                                                                                                                                                                            |

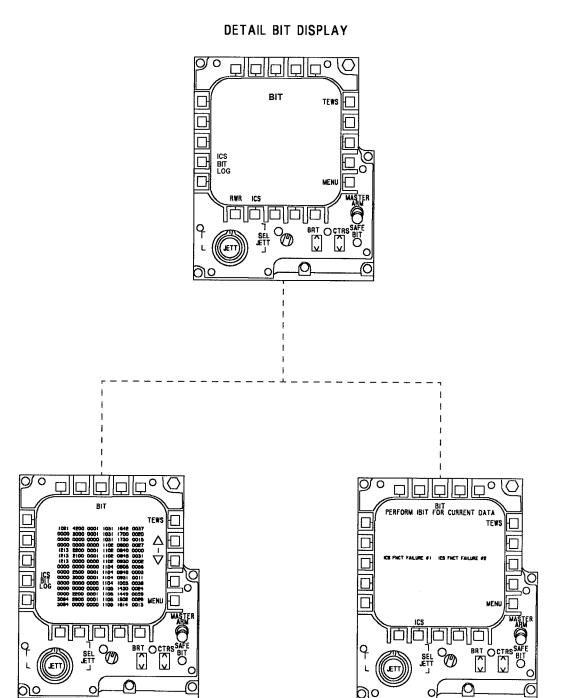

| Detail BIT display (acce | ssed from BIT 1 display)   |                                                                                                                                                                                                              |

| S15 (TEWS)               | Press and release          | Enables TEWS detail bit display.                                                                                                                                                                             |

| TEWS detail BIT displa   | y (accessed from detail BI | T display)                                                                                                                                                                                                   |

| S4 (ICS BIT LOG)         | Press and release          | Enable ICS BIT log display.                                                                                                                                                                                  |

| S6 (RWR)                 | Press and release          | Enables RWR functional fault display.                                                                                                                                                                        |

| S7 (ICS)                 | Press and release          | Enables ICMS functional fault display.                                                                                                                                                                       |

| RWR detail BIT display   | (accessed from TEWS de     | tail BIT display)                                                                                                                                                                                            |

| S6 (RWR)                 | Press and release          | a. Will be displayed in the RWR detail BIT display to indicate RWR detail BIT data is being provided.                                                                                                        |

|                          |                            | b. When pressed from the RWR detail BIT, display will return to the TEWS detail BIT display.                                                                                                                 |

| S11 (MENU)               | Press and release          | Returns to menu 1 display.                                                                                                                                                                                   |

| S15 (TEWS)               | Press and release          | Returns to the TEWS detail BIT display.                                                                                                                                                                      |

| BIT                      | Displayed                  | Indicates the system is in a BIT display.                                                                                                                                                                    |

**Table 11-2. Controls and Indicators (CONT)**

| Control/Indicator                      | Position/Condition | Function/Indication                                                                                                                                                                                        |  |  |

|----------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NO DATA<br>AVAILABLE                   | Displayed          | Indicates that CC recognizes a previous software version.                                                                                                                                                  |  |  |

| NO RWR/CC 1553<br>COM                  | Displayed          | Indicates there is no RWR/CC communication the 1553 data bus, or that there is communication on the H009 data bus.                                                                                         |  |  |

| * Functional<br>Failure #              | Displayed          | An asterisk * to the left of the functional failure message indicates a frequency degradation associated with the failure message. The frequency range affected is specified at the bottom of the display. |  |  |

| TEWS display (accessed from menu 1)    |                    |                                                                                                                                                                                                            |  |  |

| S14                                    | Press and release  | Scrolls between combat PFM legends.                                                                                                                                                                        |  |  |

| Integrated Communication Control Panel |                    |                                                                                                                                                                                                            |  |  |

| TEWS LAUNCH<br>DISABLE switch          | Press and release  | Disables launch tone.                                                                                                                                                                                      |  |  |

| TEWS LAUNCH<br>AUDIO volume control    | CW or CCW rotation | Adjust volume of launch (modulated) tone.                                                                                                                                                                  |  |  |

| TEWS CAUTION<br>AUDIO volume control   | CW or CCW rotation | Adjusts volume of caution (steady) tone.                                                                                                                                                                   |  |  |

| Main Comm Control Panel                |                    |                                                                                                                                                                                                            |  |  |

| AI light                               | On                 | Classified secret. Refer to TO SR1F-15C-2-99GS-00-2, section 11.                                                                                                                                           |  |  |

| SAM light                              | On                 | Classified secret. Refer to TO SR1F-15C-99GS-00-2, section 11                                                                                                                                              |  |  |

| Not related to RWR operation.          |                    |                                                                                                                                                                                                            |  |  |

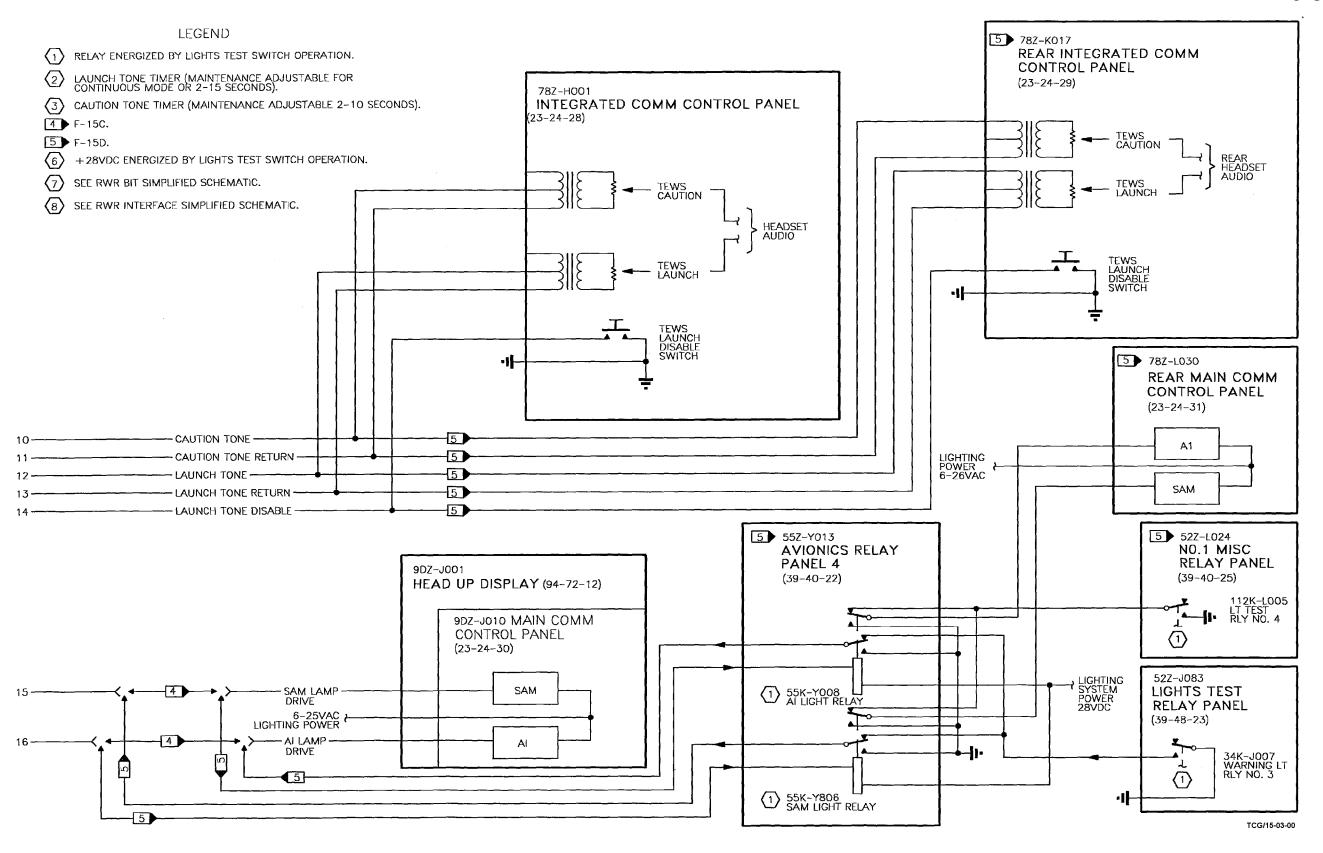

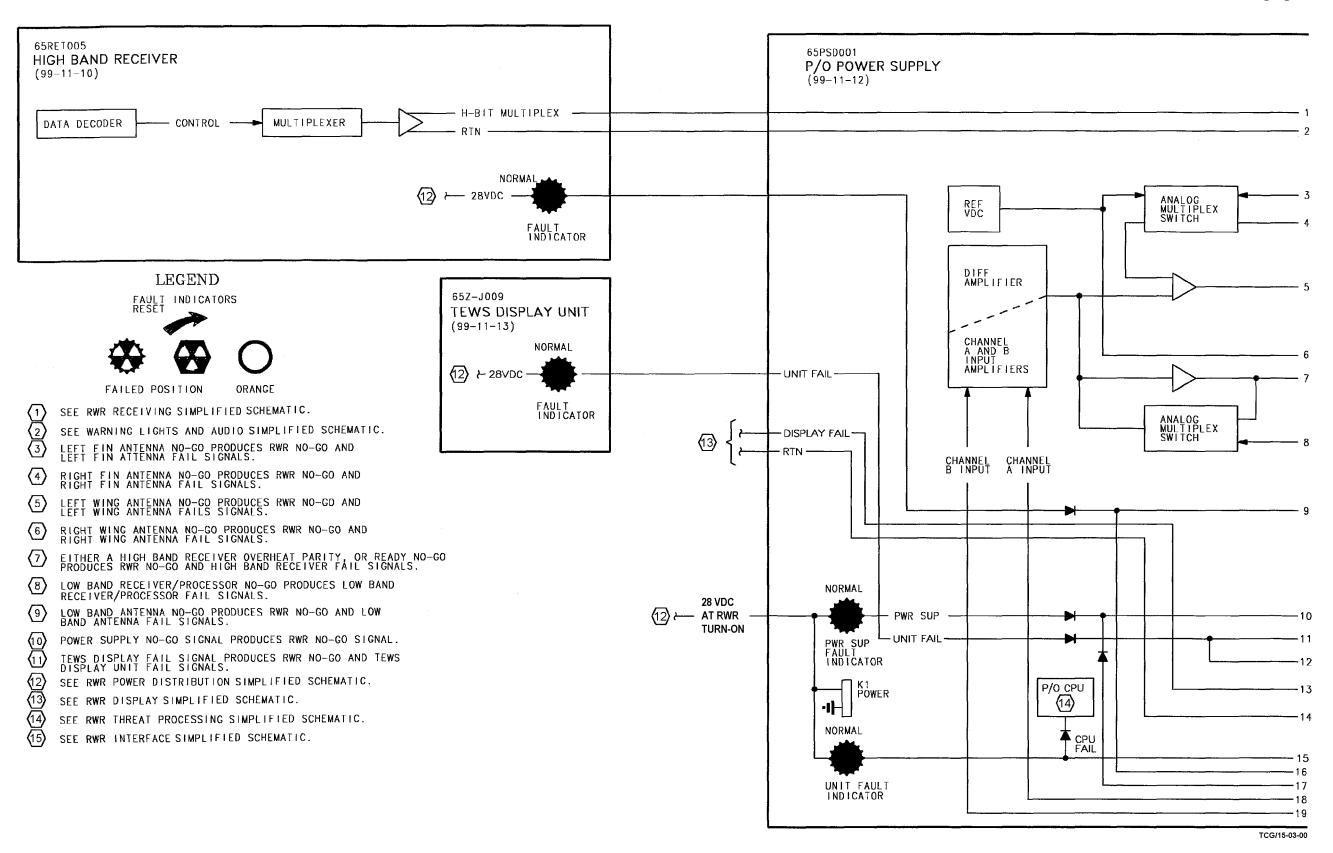

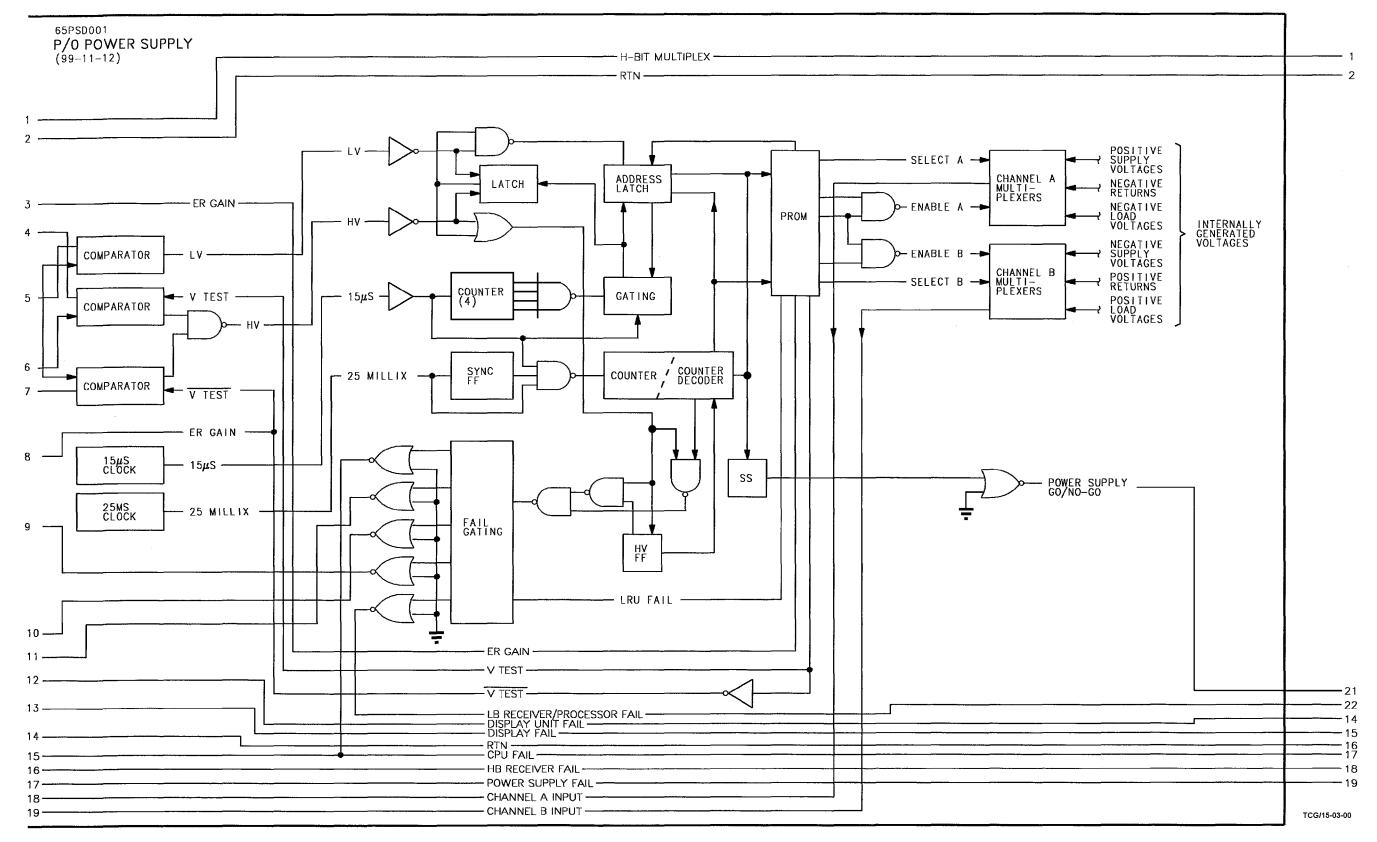

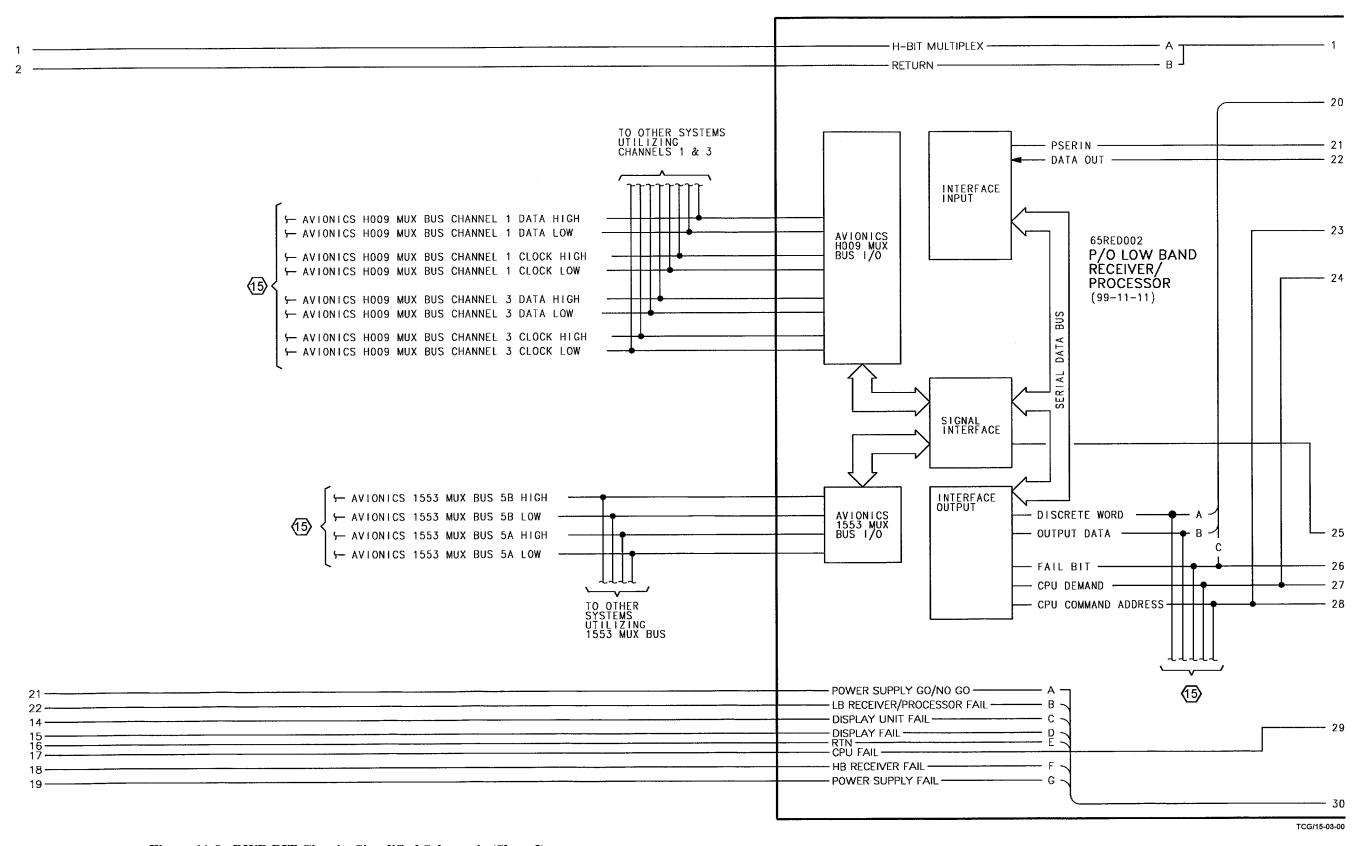

Figure 11-3. RWR Power Distribution Simplified Schematic (Sheet 1 of 3)

Figure 11-3. RWR Power Distribution Simplified Schematic (Sheet 2)

Figure 11-3. RWR Power Distribution Simplified Schematic (Sheet 3)

## **DETAIL BIT DISPLAY** BIT **TEWS** ICS BIT LOG MENU **RWR ICS** 9 $\circ$ О BIT **TEWS** FUNCTIONAL FAILURE #2 MENU

#### **RWR DETAIL BIT DISPLAY**

Figure 11-4. RWR Displays

- 11-29. **Receiving Circuits** See Figure 11-5.

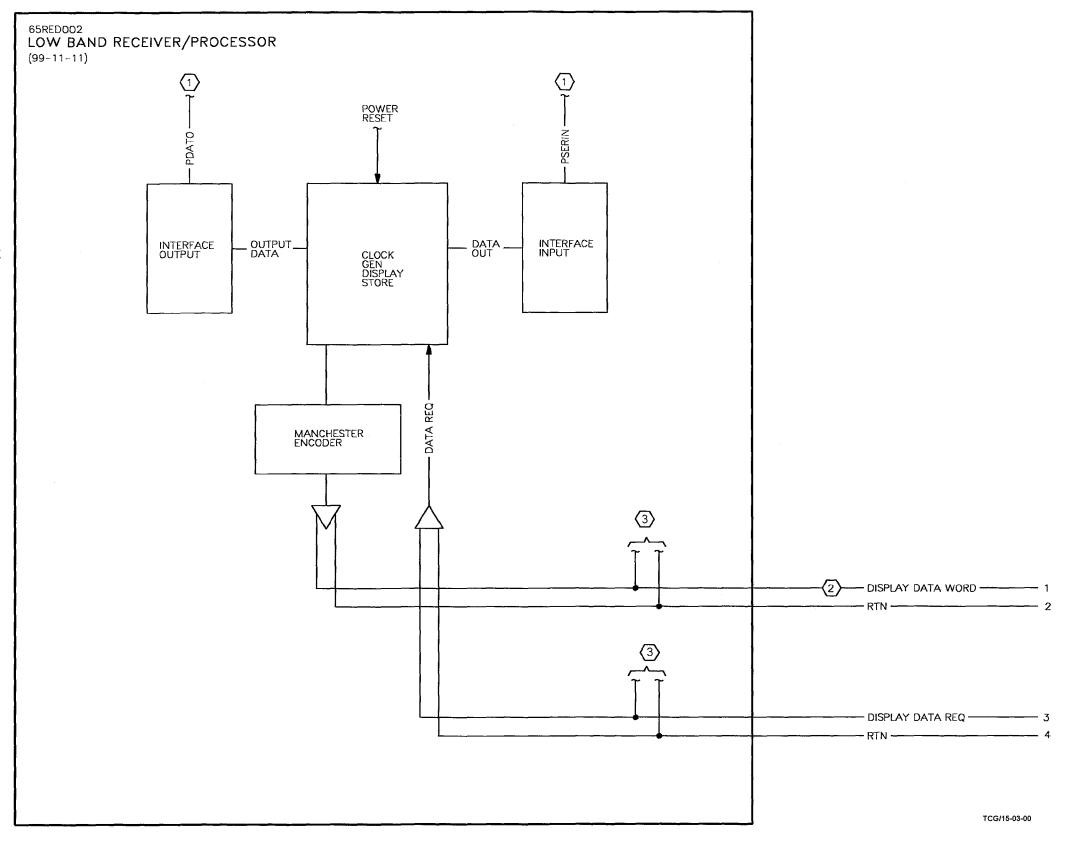

- 11-30. **High Band Signal Acquisition.** High band signal acquisition is done by the high band receiver and four antennas with a RF sample from the jammer. Processing of the incoming RF signals is controlled by receiver control signals applied in serial format from the computer/processor. This input data is received as a serial manchester coded word, allowing both data and clock signals to be transmitted on a single transmission line. Receiver control selects the RF switches and antennas, frequency band, receiver tuning, attenuation, and BIT during high band receiver operation.

- 11-31. After computer/processor initialization, the computer/processor transmits a receiver data signal which is applied to the input data control. The computer-demand and computer command address signals enable the data to be manchester coded. The received data is applied to a shift register and manchester decoder. The manchester decoder and clock generator decode the control instruction word and produce the clock frequency. The clock is used to shift the control instruction word out of the register to the address decoder and the various control latches in the receiver. The clock is also used for sychronization. and timing.

- 11-32. Signals in the high band frequency range are intercepted by four antennas; the right and left wing antenna and the right and left fin antenna. The right wing antenna has a down looking element for elevation coverage. The antenna inputs along with ICMS summing RF BIT oscillator inputs are applied to RF switches. Each antenna provides 90 degrees of coverage. Together, through switching, the signals provide omni coverage. During direction finding (DF) analysis, switch separation of the RF signals provide direction finding abilities.

- 11-33. The high band receiver amplifies high band antenna signals and converts these signals to the intermediate frequency. There are two separate channels (Channel A and Channel B) that deliver two IF and two SPU video output signals. Also, the low-band frequency range is up-converted to be processed in the same manner as the antenna signals.

- 11-34. The RF signals from the four antennas are applied to Channel A and B RF switches; where the antenna input signals are selected and switched. In normal mode, one antenna signal is fed to Channel B, and one to Channel A to provide two simultaneous IF

- output signals. The four antenna inputs may also be selected in any combination up to 50 nanoseconds after which time a new combination is selected for the next 50 nanoseconds. The cycle would then repeat continuously. Scanning may include the entire frequency range, or any number of segments in this range. The computer/processor controls the scan by generating digital signals which are applied to the low band receiver/processor Channel A and B in parallel. The Band II down converts in each channel converting the signals to Band I frequency range. The Band I signals are again down converted to IF signals. By power splitting the RF signal, SPU signals are developed.

- 11-35. Low Band Signal Acquisition. When there is a low band signal to be processed, the Chan A/low band RF is applied to the IF/low band switch of Channel A. The Chan A/low band sign IF is raised to a Band I frequency by mixing with a local oscillator signal. From this point, the IF and SPU video signals are developed for the Chan A/low band IF in the same manner as for the antenna input signals; except, only Channel B outputs are used, since Channel A is occupied with the Chan A/low band IF input from the low band receiver/processor.

- 11-36. BIT operating and calibration makes use of the harmonic generator and noise generator. The harmonic generator is used for calibration of the local oscillator and for digital delay calibration. It is also used as an input test signals to measure the difference between Channel B and Channel A gain (Channel unbalance). The noise generator provides a known excess noise level (power-frequency spectrum) to test average receiver gain over the IF bandpass of 500 MHz.

- 11-37. **IF Processing.** Each IF Channel has switches, filters, and amplifiers for bandwidth control and signal compression (logging). The receiver control signal sets the switches for the selected mode. Both channels operate symmetrically; so that, when a particular path is enabled in one, the same path is enabled in the other (with the exception of low band and BIT). There are four such modes that operate symmetrically: wide band, medium band, notch and CW.

- 11-38. In wideband, the full IF bandwidth from the high-band receiver is passed unfiltered. In medium band, the IF bandwidth is limited by an A and B filter. The notch filter is enabled when there is an undesired frequency anywhere in the bandwidth. In CW mode, the IF signal is steered to the channel sel for CW

filtering. The CW channel has two operating modes plus BIT. The two modes are CW coarse and CW fine. In CW coarse, the CW IF bandwidth is limited by CW channel sel. Since there is only one CW coarse filter, both channels are looked at sequentially. This is done by a commutating switch. In CW fine, the IF signal coming through the CW channel sel is distributed through a power divider. One output of the power divider is superheterodyned down in fine gain, so it falls within the bandpass of a very narrow-band surface acoustic wave (SAW) filter. The filter in conjunction with the VCO and a mixer allows for detection of multiple CW signals. The SAW mode operates only in high band. The CW coarse output of the power divider is fed directly to coarse/fine CW switch. The selected frequency (coarse or fine) is detected and amplified to produce LOG VID CW.

11-39. During BIT operation, LO (local oscillator) is used for a superheterodyned BIT source. The BIT source is used for low band antenna receiver and IF/ processor testing. The C/D band switch selects the signal from the low band antenna when low band mode is enabled, low band noise, or the local oscillator when BIT is required. The selected signal is amplified and sent back through channel A switching, to the high band receiver for up-conversion.

11-40. In wide and medium band, the channelizer is used to select one channel at a time. The channel with the greater amplitude is selected by the rec control signal from the computer/processor. The limiter receives the delayed signal and outputs a constant power range of input power. In the channelizer, power dividers distribute the signal simultaneously to 13 bandpass filters. A detector follows each filter and the resulting video signals identify the IF frequency.

11-41. **Computer/Processor Unit.** The computer/processor, located in the power supply, is a digital computer which meets all the high-speed mathematical processing requirements of the RWR. The computer/processor is made up of three major sections as listed below:

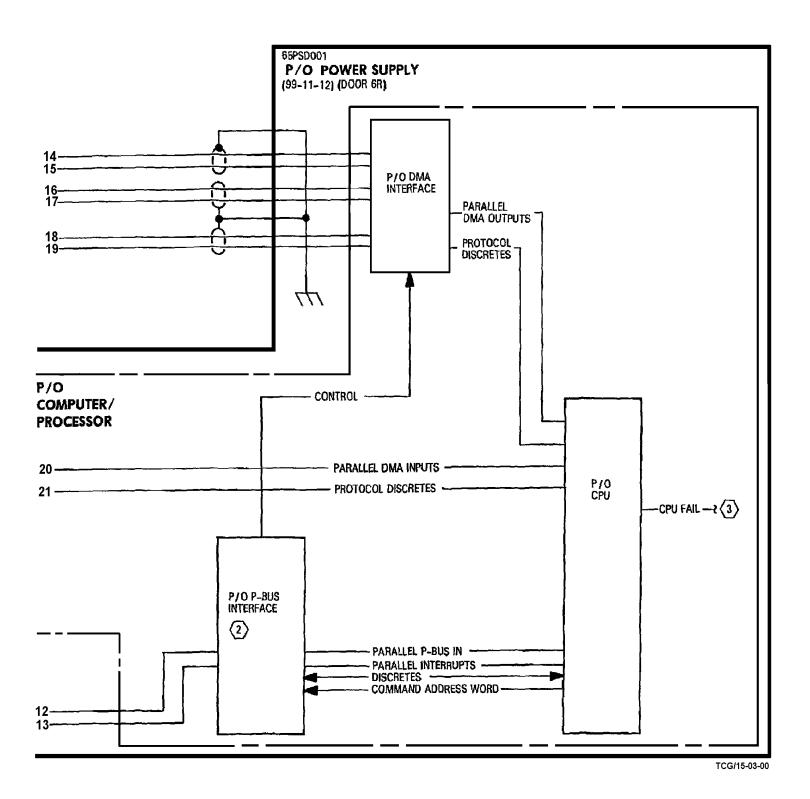

- a. PBUS interface

- b. DMA interface

- c. Processor (CPU)

A simplified diagram of the computer/processor is shown in Figure 11-6.

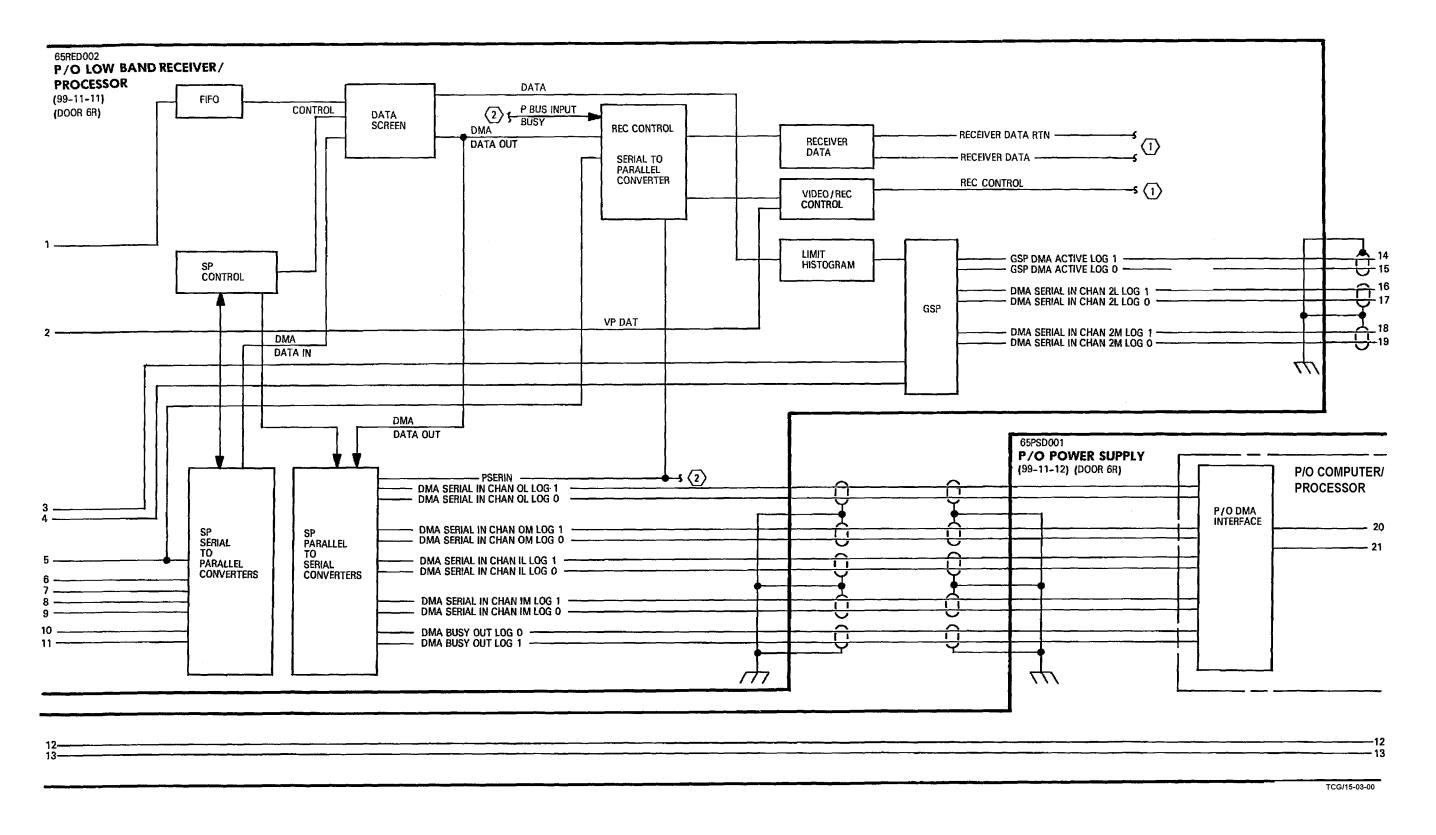

11-42. **P BUS Interface.** The P BUS interface provides one parallel to serial output channel, one serial to

parallel input channel, and the necessary protocol discrete inputs. The input channel, the output channel and controllers operate at a 5 megahertz rate. All command address words and demands for service originate at the processor. Control signals are passed on to the DMA interface after clearing and turning on all channels (initialization), the P BUS interface waits for a service demand from the processor. The processor can issue any of 11 commands. These include four DMA channel clears, four DMA channel enables, system reset, input or output P BUS data and load status data. When the processor commands the clearing or enabling of a DMA channel, the appropriate clear DMA signal or turn-on DMA signal is sent and receipt of the command is acknowledged. When the processor requests to output data, the P BUS interface tests the register full flag. If it is inactive, the data is loaded into the register and acknowledges receipt of the command. When the processor requests to input data, the P BUS interface tests to see if the register is full. If so, it outputs the data, acknowledges the command and clears. The interrupts from the low band receiver/ processor are applied to the P BUS interface.

11-43. **DMA Interface.** The DMA interface provides three serial-to-parallel input channels. parallel-to-serial output channel, and the necessary handshake protocols. The controllers and channels operate at a 5 megahertz rate. Control signals for the clearing of channels, the enabling of channels, and rebound testing are provided from the PBUS interface. The four channels of the DMA interface are initialized by enabling and clearing signals from the P BUS interface. Then, while waiting for the register to be filled with DMA input data from any one of the three input channels, the DMA CPU interface demands a DMA output from the processor. When any such input occurs, the DMA CPU interface immediately demands input service from the processor. Any refusal of service from the processor concerning a specific channel causes the DMA interface to disable the channel. The only way to re-enable the channel is by signal from the P BUS interface. When a full signal from any of the three input channels exists, the applicable register full flag is set. If two channels are simultaneously full, the state control firmware in the DMA interface establishes service priority. Any full input channel outputs a busy signal to the low band receiver/processor until it is serialized and cleared. When a full indication is sensed, the channel is enabled and it outputs a demand to the processor. Either a no-acknowledge or an acknowledge is received. The interface then either turns off the channel or outputs the data. The register full flag is

Figure 11-5. RWR Receiving Simplified Schematic (Sheet 1 of 3)

Figure 11-5. RWR Receiving Simplified Schematic (Sheet 2)

#### LEGEND

Figure 11-5. RWR Receiving Simplified Schematic (Sheet 3)

11-23

- **LEGEND**

- SEE RWR RECEIVING SIMPLIFIED SCHEMATIC

- 2 SEE RWR INTERFACE SIMPLIFIED SCHEMATIC

- (3) SEE RWR BIT SIMPLIFIED SCHEMATIC

Figure 11-6. RWR Threat Processing Simplified Schematic (Sheet 1 of 3)

Figure 11-6. RWR Threat Processing Simplified Schematic (Sheet 2)

11-25

Figure 11-6. RWR Threat Processing Simplified Schematic (Sheet 3)

**99-11-00** 11-26

cleared. When full flag is set and the channel is enabled, the interface test the DMA busy to determine if data can be sent. If any channel is running rebound tests, the DMA busy is not tested and the data is immediately shifted out. If no rebound test is in progress and busy is not active, the data is shifted out and the full flag is cleared. This allows the interface to load data again when the data is ready from the processor.

11-44. **Processor.** The processor provides the data paths, registers, arithmetic unit, and various other logic required to do the data handling specified by the program instruction being executed. The processor keeps track of the instruction being executed, provides temporary storage for the instruction word loaded from program memory, does all arithmetic, logical and shift and compare operations required for execution of program instructions. A 16-bit by 16-bit general register is used for temporary storage of primary operand, results of previous instructions, and input/ output data. Selection of one of the sixteen 16-bit registers is controlled by a selected field of the instruction word. The output of the register file is applied to multiplexers. This permits parallel operations within the general register file and removes the requirements of storing intermediate values in temporary memory locations.

11-45. Computer memory is addressed in 4K blocks. Successive addresses are compared to previous addresses in holding register. This reduces memory access time. The processor has the ability of directly accessing 256K words of the memory paging scheme. The processor handles the P BUS interface processing. The direct memory access controller provides data transfers between the computer memory and the low band receiver/processor on the DMA interface.

# 11-46. **THREAT PROCESSING CIRCUITS.** See Figure 11-6.

11-47. **High Band and Low Band Threat Processing.** Threat processing of the high and low band IF signals is completed by the threat processing circuits in the low band receiver/processor. The log video signals are tested for a lim video presence to determine if the radar signal exists in the IF bandpass and the channel receiving the strongest signal. Then, the pulse width of the log video signal selected for analysis is measured and tested against PFM limits. If the pulse width of the received signal is within limits, the time of arrival of each such confirmed pulse is measured. The signal is